Network communication cell used for multi-core microprocessor on-chip interconnected network

A nuclear microprocessor and on-chip interconnection technology, which is applied in the fields of electrical digital data processing, instruments, computers, etc., can solve the problems of different topological structure requirements of the on-chip interconnection network, weak reusability, and difficult design, etc., to achieve The effect of shortening design time, good reusability, and reducing design difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

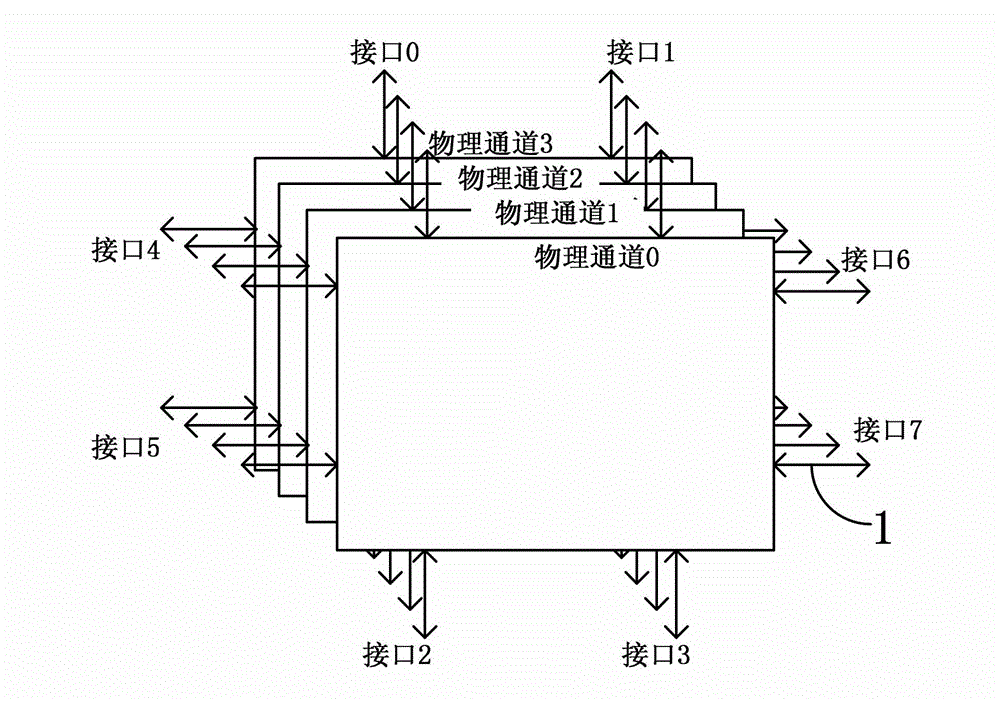

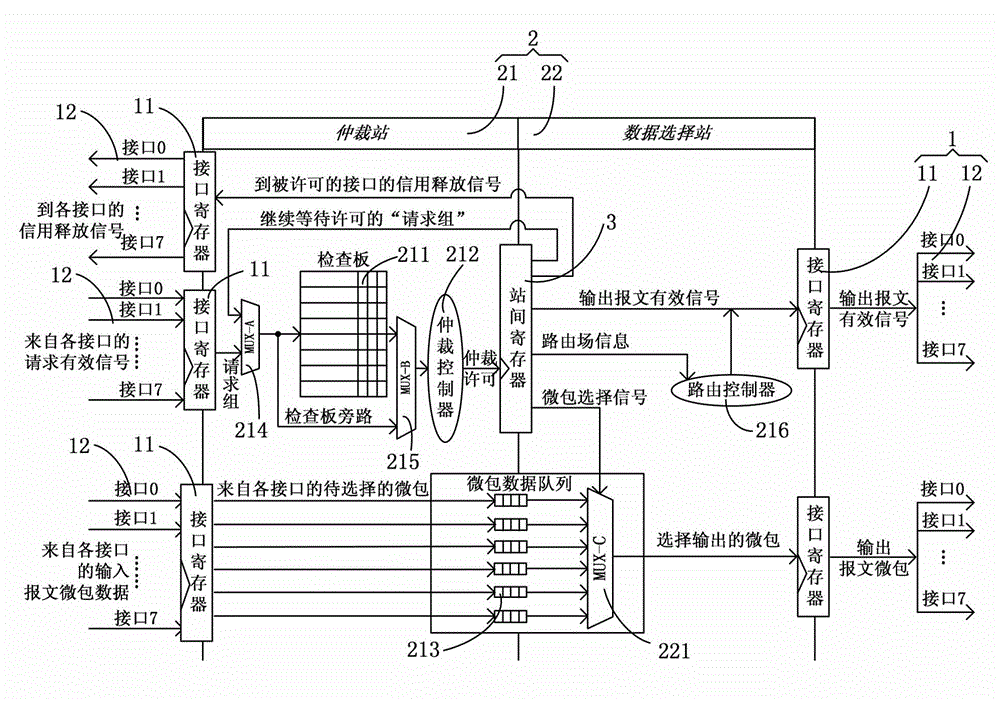

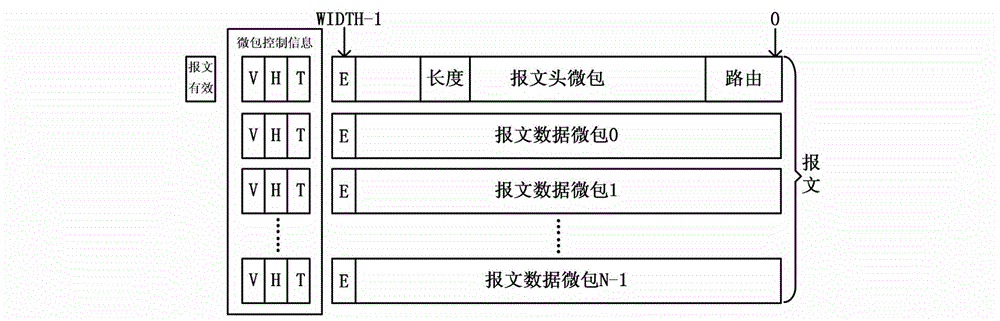

[0032] Such as figure 1 with figure 2 As shown, the network communication cell used in the multi-core microprocessor on-chip interconnection network of this embodiment includes at least one physical channel, the physical channel includes a communication interface unit 1 and a two-stage pipeline structure 2, and the communication interface unit 1 includes an interface register 11. And no more than 8 two-way communication interfaces 12, the two-stage pipeline structure 2 includes an arbitration station 21 used to arbitrate incoming message micro-packet data requests and buffer input message micro-packet data, and a message micro-packet that is allowed to be arbitrated. The data selection station 22 for selecting and outputting packet data, the arbitration station 21 and the data selection station 22 are respectively connected to the two-way communication interface 12 through the interface register 11, and the arbitration station 21 and the data selection station 22 are provided wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More