Laminated diode manufacturing process and chip sieve tray thereof

A manufacturing process and chip sieve technology, which is used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of chip mesa damage, improvement, restricting electrical yield rate, etc., to improve efficiency and accuracy, improve The effect of work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

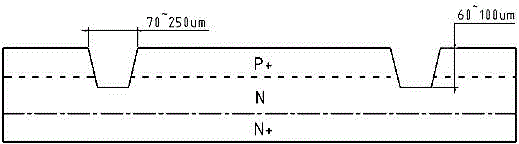

[0015] Such as figure 1 As shown, a wide groove is opened on the P side (or N side) of the silicon wafer, the groove width is 70~250um, and the groove depth is 60~100um (see figure 1 Medium size), adjust the groove width and groove depth in the above range according to the specific product requirements.

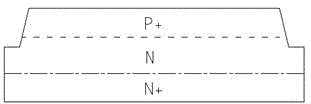

[0016] Such as figure 2 As shown, scribing is performed with the center of the bottom of the wide groove as the boundary, and the width of the scribing lane is about 50um, thereby forming a chip with a small face and a large face.

[0017] In the process of grooving and scribing on the P side (or N side) of the silicon wafer, by adjusting the chip size, the size of the small side is properly compensated, so as to meet the electrical parameter requirements of the product. The specific method is the same as the compensation principle of the size and surface area of the GPP chip known in the industry, and will not be repeated here.

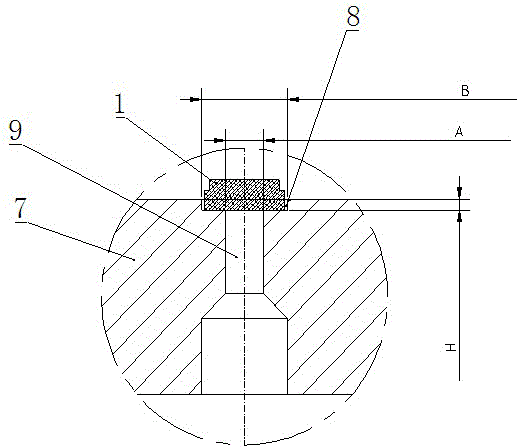

[0018] Such as image 3 As shown, lead...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More