Patents

Literature

32results about How to "No need for manual identification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

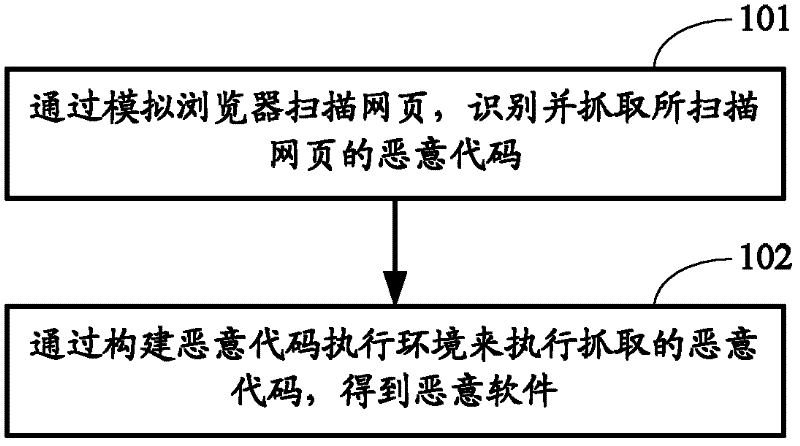

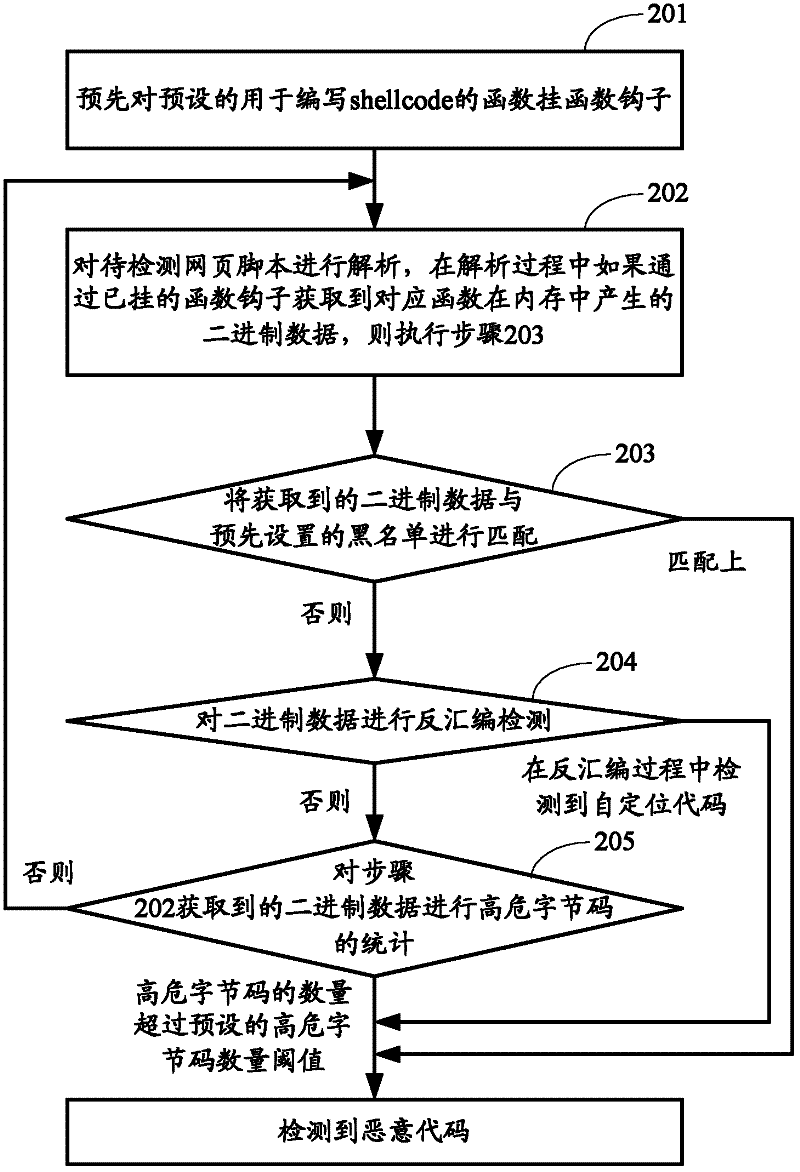

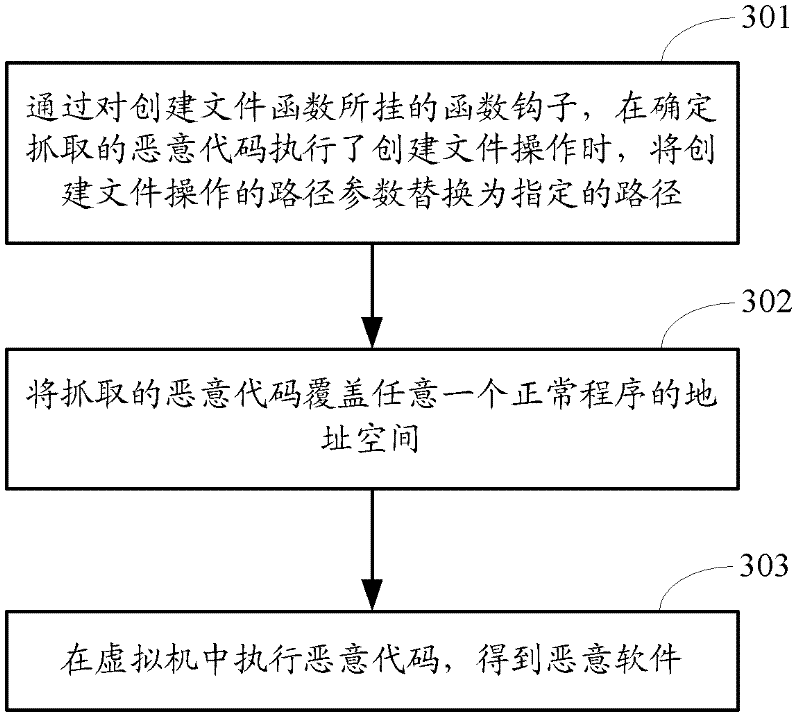

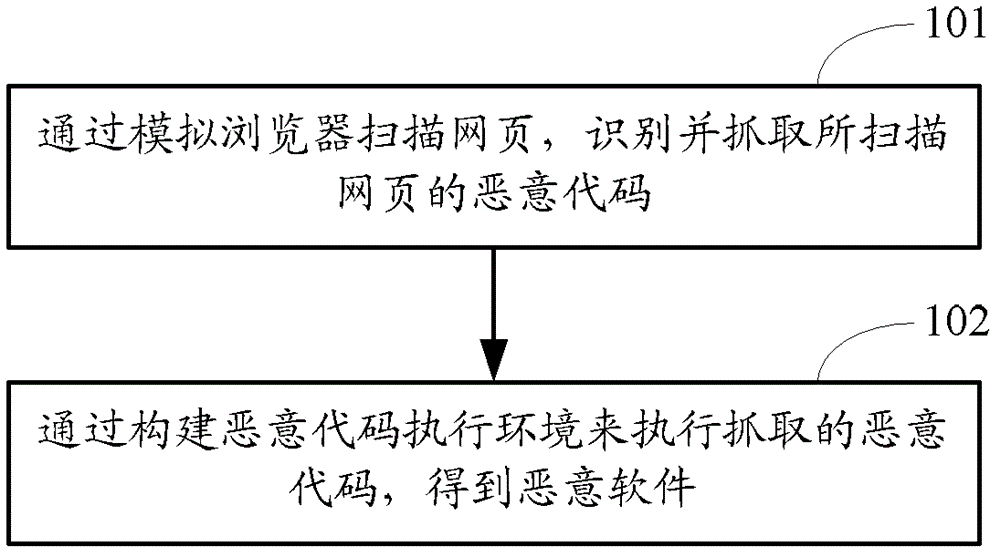

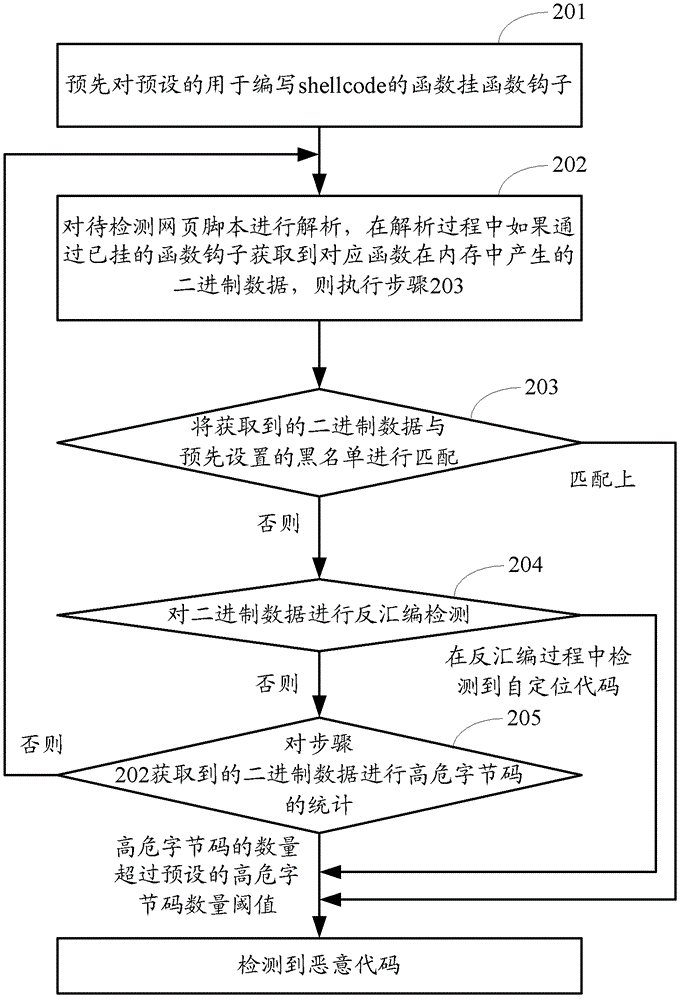

Method and device for collecting malicious software automatically

ActiveCN102609649ARealize automatic collectionNo need for manual identificationPlatform integrity maintainanceMalwareSoftware

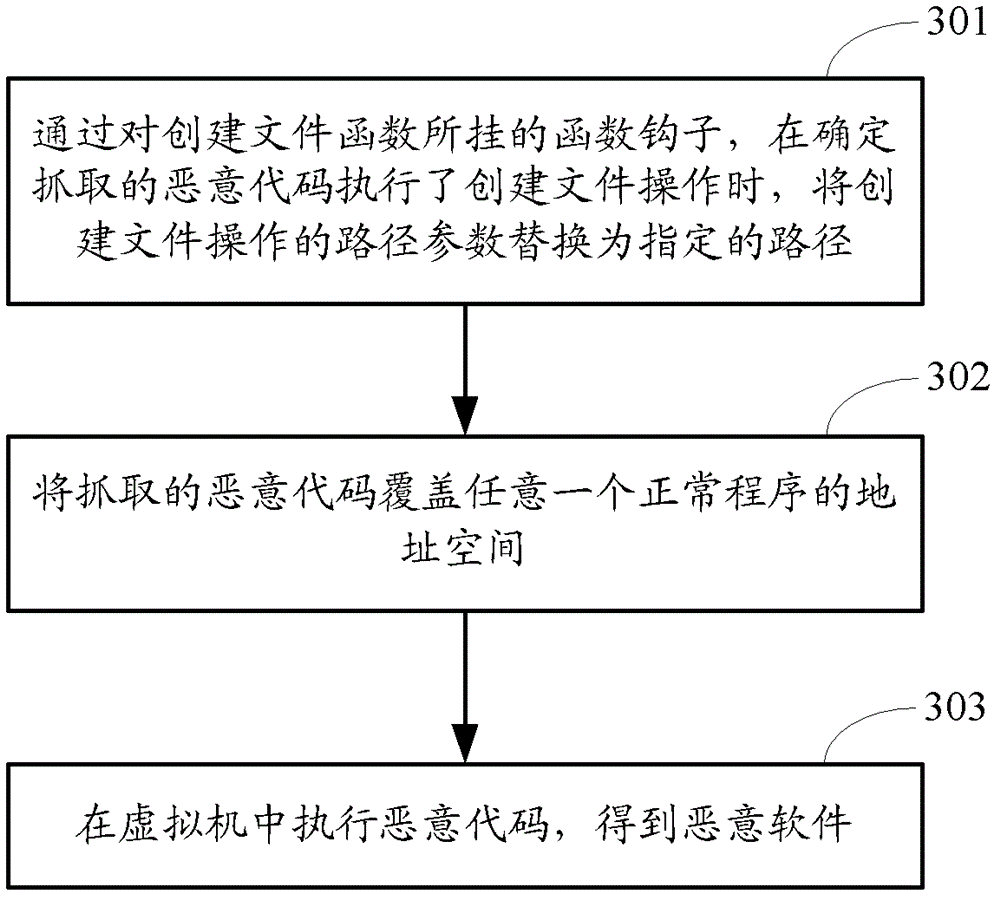

The invention provides a method and a device for collecting malicious software automatically, wherein the method comprises the following steps: S1, scanning web pages through a simulative browser, identifying and capturing a malicious code of the scanned web pages; and S2, constructing a malicious code executing environment to capture the malicious code so as to obtain the malicious software. The method can realize to collect the malicious software automatically without manual identification; therefore, efficiency is increased greatly; in addition, the method starts to identify the malicious code so as to obtain the malicious software without a method of collecting the static characteristics of the malicious software; the malicious software including the malicious code can be collected no matter the malicious software uses deformation methods; and reliability and relevance ratio are improved greatly.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

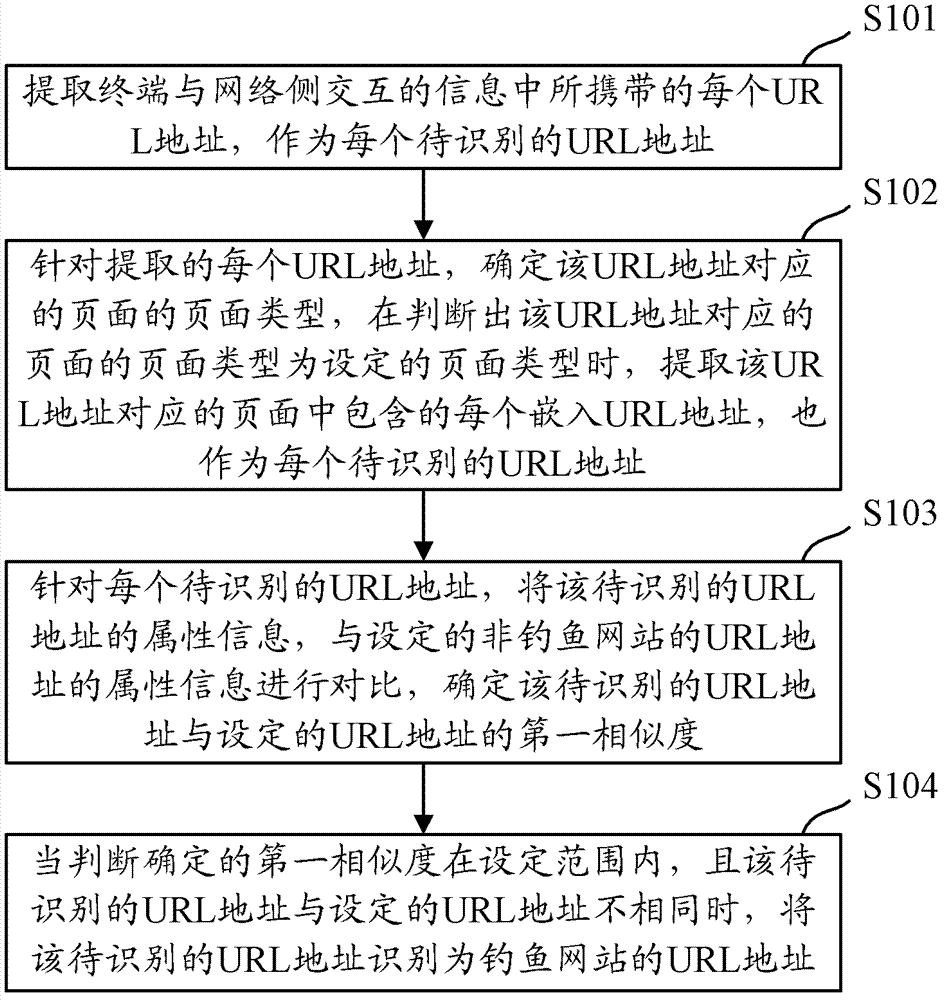

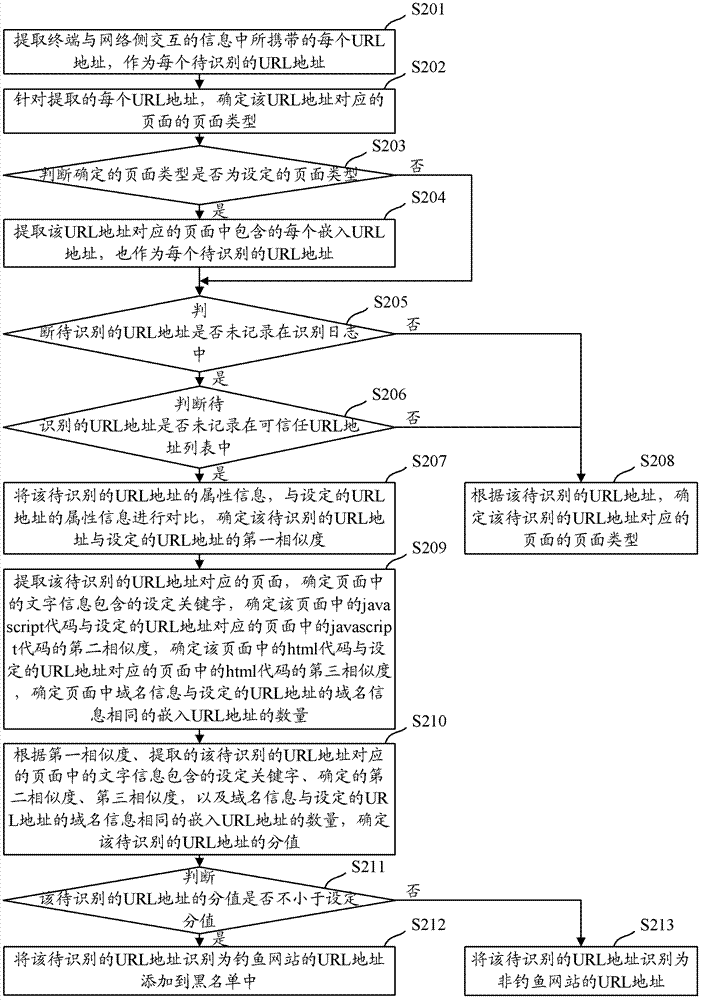

Method and device for identifying phishing websites

The invention discloses a method and device for identifying phishing websites and aims to solve the problem that efficiency and accuracy in identifying phishing websites by the prior art is low. The method includes: using a URL (uniform resource locator) in information of interaction between a terminal and a network side and a URL embedded in a page in preset page type as URLs to be identified; when first similarity between the URLs to be identified and a set URL is within a set range, identifying the URLs to be identified as URLs of phishing websites. Whether the URLs to be identified are the URLs of phishing websites or not is determined according to the first similarity between the URLs to be identified and the set URL, the method for automatically identifying phishing websites is realized, and the efficiency in identifying phishing websites is improved. The URL embedded in the page in the set page type is used as the URL to be identified for identification, so that accuracy in identifying phishing websites is improved.

Owner:ALIBABA CLOUD COMPUTING LTD

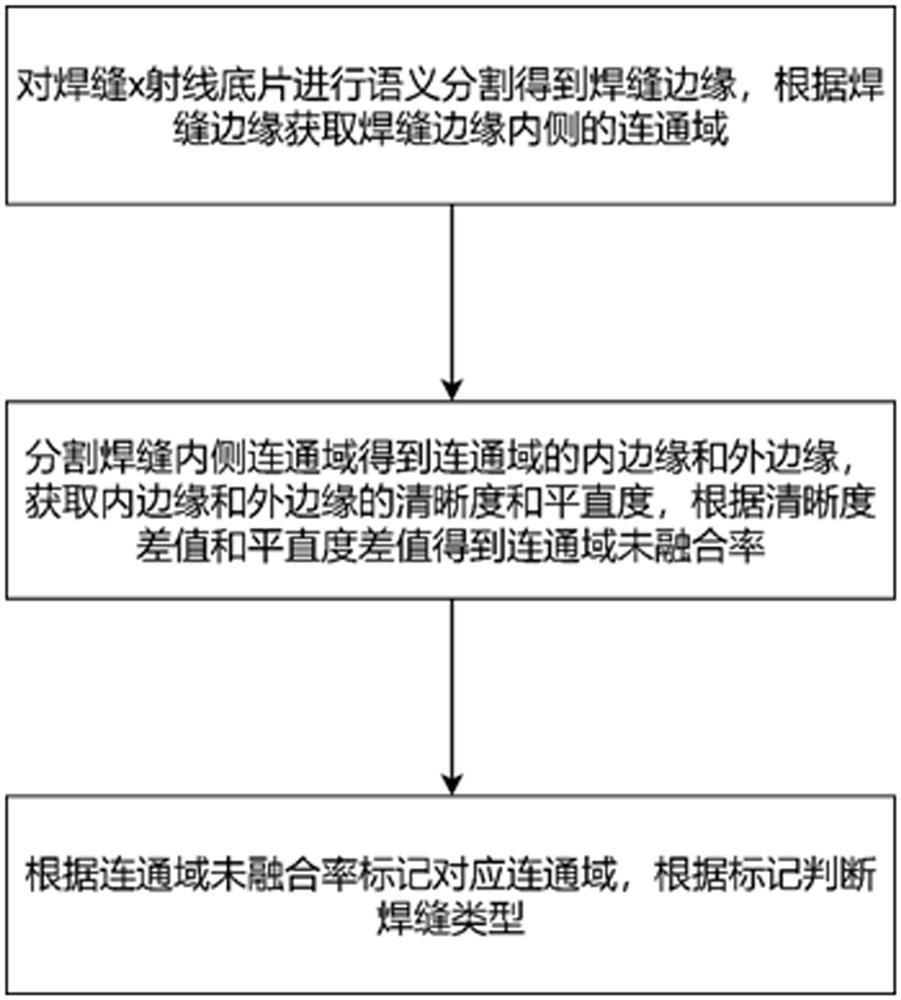

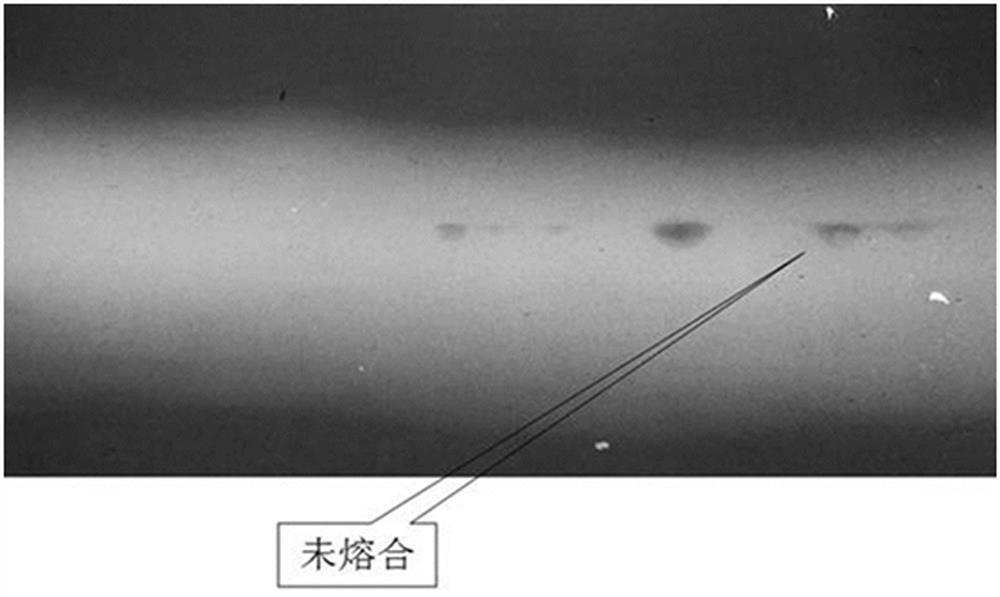

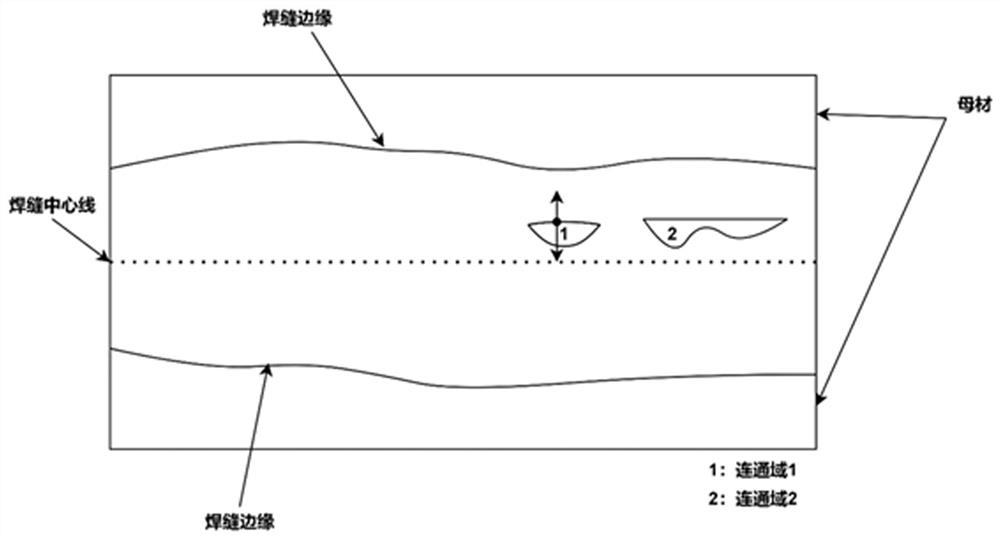

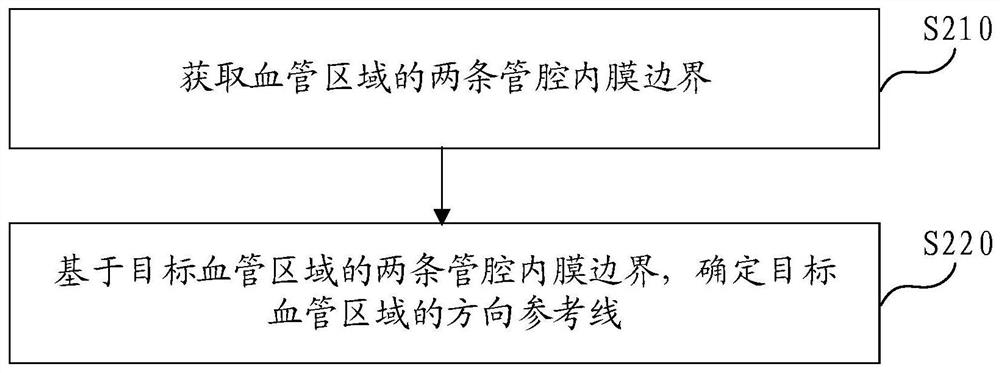

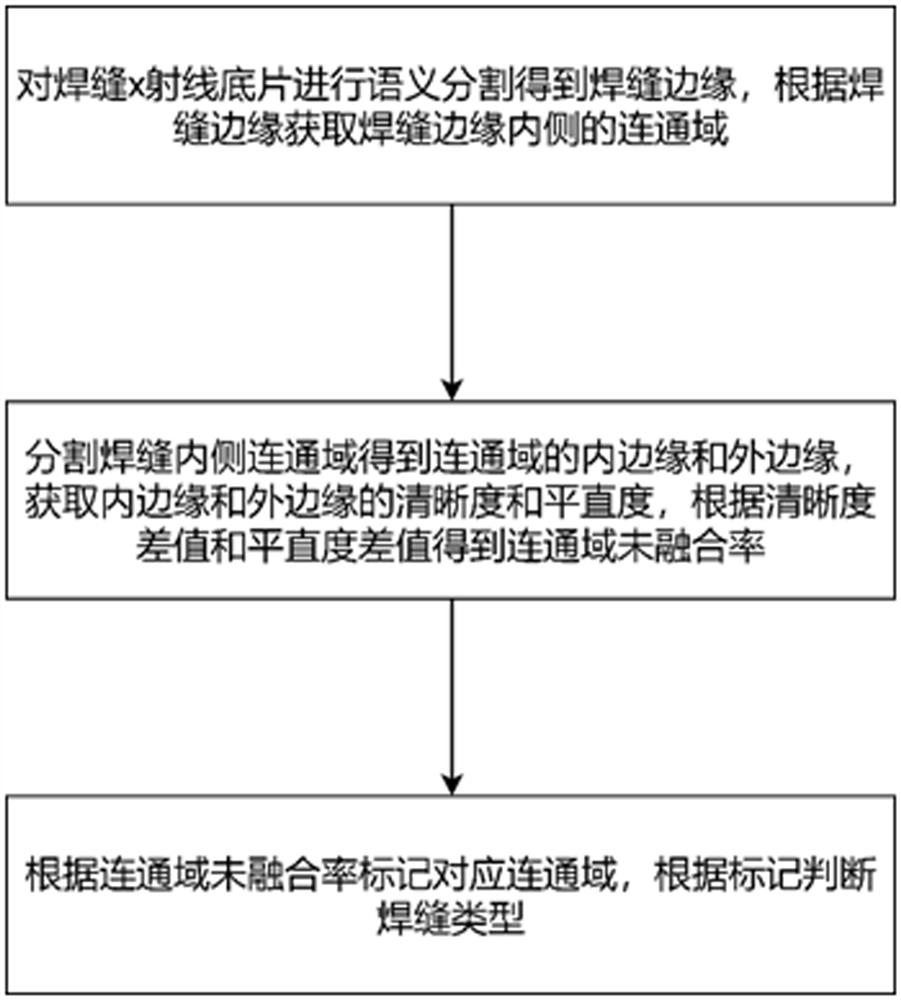

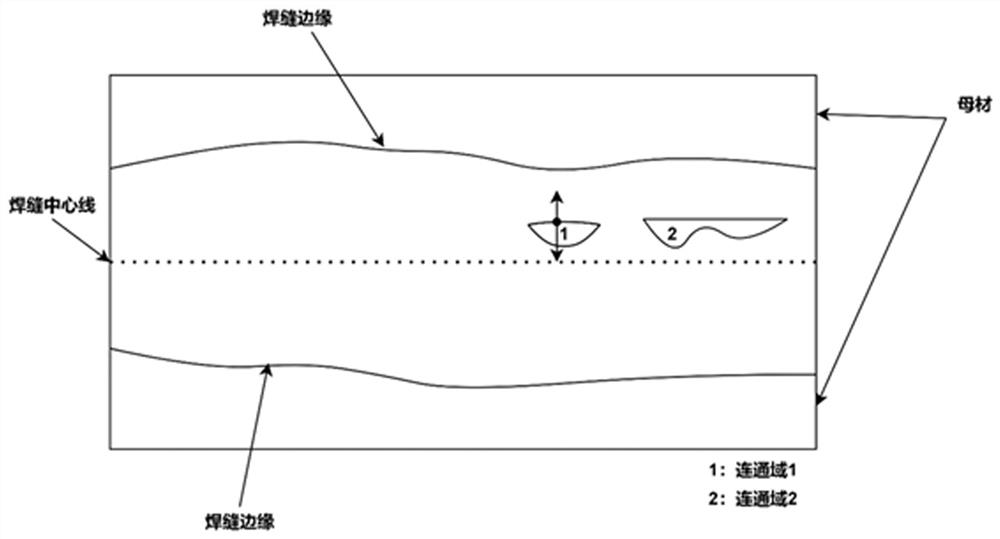

Nondestructive detection method for weld defects based on computer vision

ActiveCN113588692ANo need for manual identificationHigh degree of automationImage enhancementImage analysisAlgorithmDomain analysis

The invention relates to a nondestructive detection method for weld defects based on computer vision, which comprises the following steps of carrying out semantic segmentation on a weld x-ray negative film to obtain a weld edge, and carrying out connected domain analysis on an inner side area of the weld edge to obtain a connected domain on the inner side of the weld; segmenting the edge of each connected domain to obtain an outer edge close to one side of the base material and an inner edge close to one side of the center of the welding seam; respectively obtaining the identification degree, the blackness and the straightness of the inner edge and the outer edge; obtaining the definition of the inner edge and the outer edge by using the identification degree and the blackness; obtaining a non-fusion rate of the connected domain according to a definition difference value and a straightness difference value between the inner edge and the outer edge; and setting a threshold value, comparing the threshold value with the non-fusion rate corresponding to the connected domain, and marking the connected domain according to a comparison result of the threshold value and the non-fusion rate corresponding to the connected domain. According to the technical means provided by the invention, the non-fusion defect of the welding seam can be accurately identified, and the easy-to-confuse type identification of the welding seam defect is more accurate.

Owner:南通皋亚钢结构有限公司

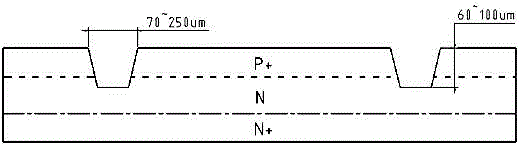

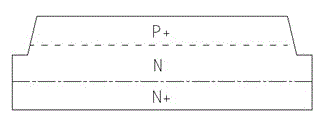

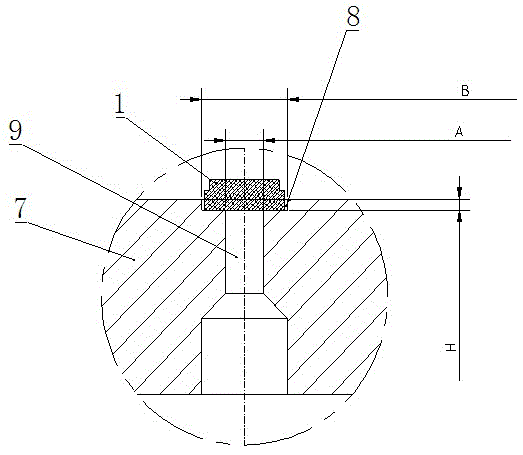

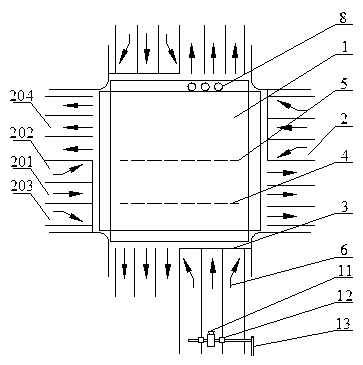

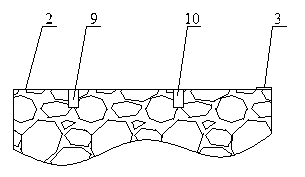

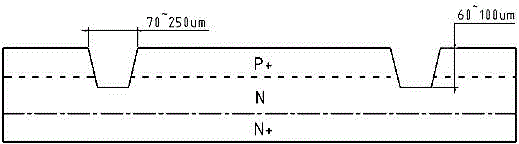

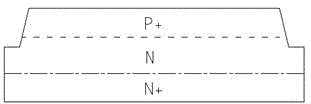

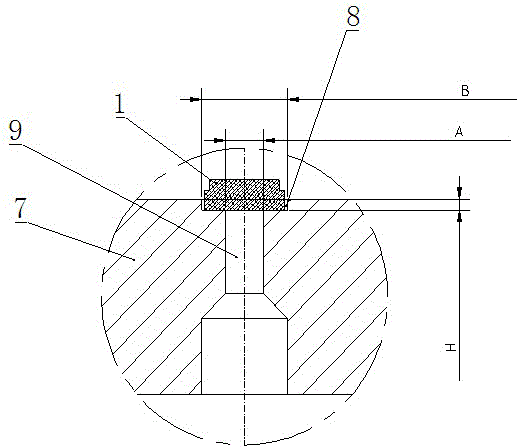

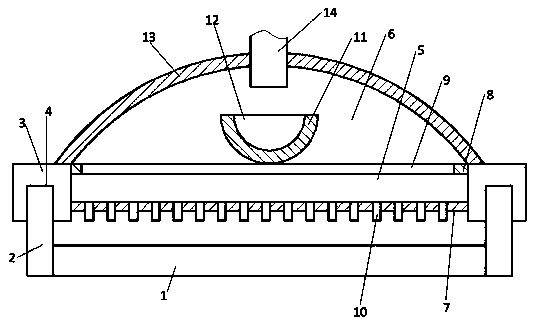

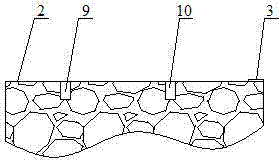

Novel laminated diode manufacturing process and chip sieve tray thereof

ActiveCN102881587AAvoid damageNo need for manual identificationSemiconductor/solid-state device manufacturingAcid washingEngineering

The invention relates to a novel laminated diode manufacturing process and a chip sieve tray thereof. The novel laminated diode manufacturing process is characterized by comprising the following steps of forming a wide groove in the P surface or the N surface of a silicon wafer, wherein the groove is 70 to 250 mum in width and 60 to 100 mum in depth; scribing in the way that the center of the bottom of the wide groove serves as a boundary; after filling a lead and sieving a chip, welding and fixing the chip and the lead by using a welding material, and when the chip is sieved, matching a small surface formed by forming the wide groove with a profile hole of the chip sieve tray to identify the polarity of the P surface or the N surface; and sequentially performing acid washing, strip combing, sizing, glue curing, mould pressing, post curing, electroplating, testing, character printing, packaging and goods delivery. Due to the steps of forming the wide groove in the P surface or the N surface of the silicon wafer, scribing in the way that the center of the bottom of the wide groove serves as the boundary, matching the small surface formed by forming the wide groove with the profile hole of the chip sieve tray to automatically identify and adjust the polarity of the P surface or the N surface, manual identification is not required, the efficiency and the accuracy are effectively improved, and the damage to the chip caused by manual adjustment with a nipper is avoided.

Owner:RUGAO DACHANG ELECTRONICS

Method and device for monitoring motor vehicle in case of regulation violation for running red light

InactiveCN103021182AEffective filteringReduce useless dataRoad vehicles traffic controlTime rangeMotor vehicle part

The invention discloses a method for monitoring a motor vehicle in case of regulation violation for running the red light. The method includes the following steps: A. a red light signal time range is obtained, and detection of running against guiding arrows beyond the red light signal time range is conducted; B. running speed V of the vehicle in front of a stop line in the red light signal time range is detected, and if the running speed is larger than a preset value Vy, a first evidence picture of the vehicle is shot; C. whether the vehicle is pressed on the strop line is detected, and if the vehicle is pressed on the stop line, a second evidence picture is shot, a step D is conducted, otherwise, detection stops; and D. a regulation violation type of the vehicle is judged, and a third evidence picture is shot. The invention further discloses a device for monitoring the motor vehicle in case of the regulation violation for running the red light. The method and device has the advantages of being high in collecting accuracy, small in data redundancy, low in cost and capable of further determining a detailed regulation violation type and monitoring regulation violation behaviors of the vehicle running against the indicating signs during the green light.

Owner:CHENGDU LINHAI ELECTRONICS

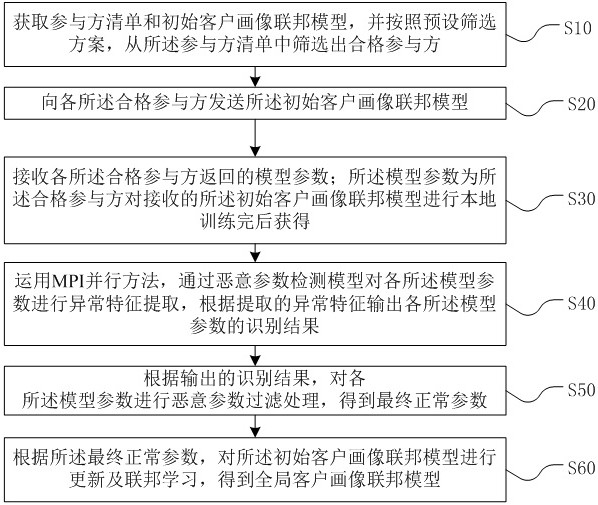

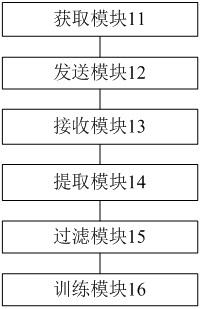

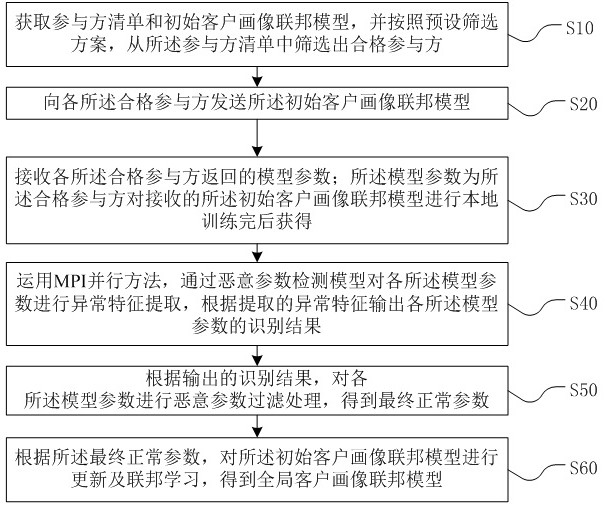

Federal model training method and device, customer portraying method and device, equipment and medium

ActiveCN113283185AShorten learning modeling cycleFast trainingCharacter and pattern recognitionDesign optimisation/simulationFeature extractionEngineering

The invention relates to the technical field of user portraying, and provides a federation model training method and device, a customer portraying method and device, equipment and a medium, and the method comprises the steps: obtaining a participant list and an initial customer portraying federation model, and screening out qualified participants from the participant list according to a preset screening scheme; sending the initial customer portrait federation model to each qualified participant; receiving returned model parameters; performing abnormal feature extraction through a malicious parameter detection model by applying an MPI parallel method, and outputting an identification result of each model parameter according to the extracted abnormal features; filtering malicious parameters to obtain final normal parameters; and performing updating and federation learning to obtain a global customer portrait federation model. According to the method, the MPI parallel method is applied, abnormal feature extraction and malicious parameter filtering processing are carried out through the malicious parameter detection model, malicious parameters provided by malicious participants are automatically removed, and the efficiency and precision of federal learning modeling are improved.

Owner:PING AN TECH (SHENZHEN) CO LTD

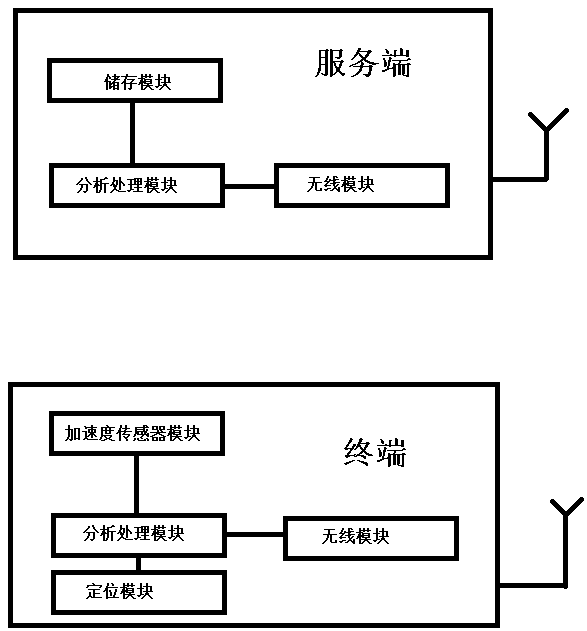

Road obstacle recognition device and method

InactiveCN110139216AQuick identificationLive UpdateParticular environment based servicesNavigation by speed/acceleration measurementsReal-time dataTraffic accident

With the continuous popularization of automobiles, traffic accidents are increased. A plurality of obstacles may appear on the motor vehicle lane and may be pits, stones, templates and the like, and the potential safety hazards may greatly increase the possibility of traffic accidents. The road safety greatly threatens the life and property of the social public due to road traffic accidents everyyear, and becomes a key point of global attention. However, if a manual mode is adopted to collect stone sundries similar to road pits or bulges on a road, the efficiency is very slow and in-time performance cannot be guaranteed. Existing vehicles have navigation functions, or mobile phones have navigation functions, when people use navigation, a navigation server can also obtain real-time data ofthe mobile phones or vehicle-mounted navigation, but the information possibly becomes a breakthrough for people to analyze road obstacles. The invention discloses a method and a device for identifying road obstacles through terminals such as a mobile phone, a navigation server and the like, and is worthy of popularization.

Owner:李星辉

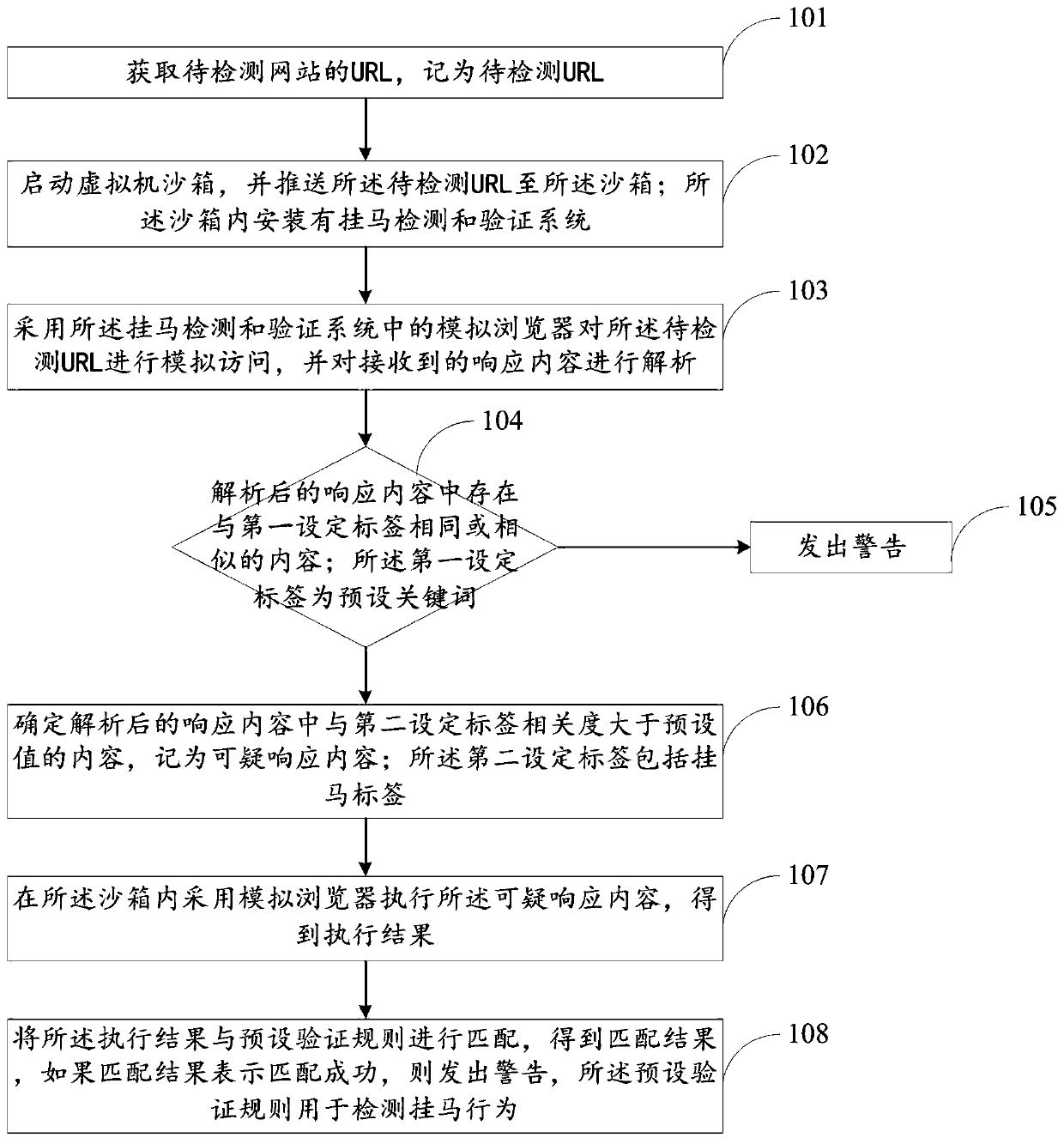

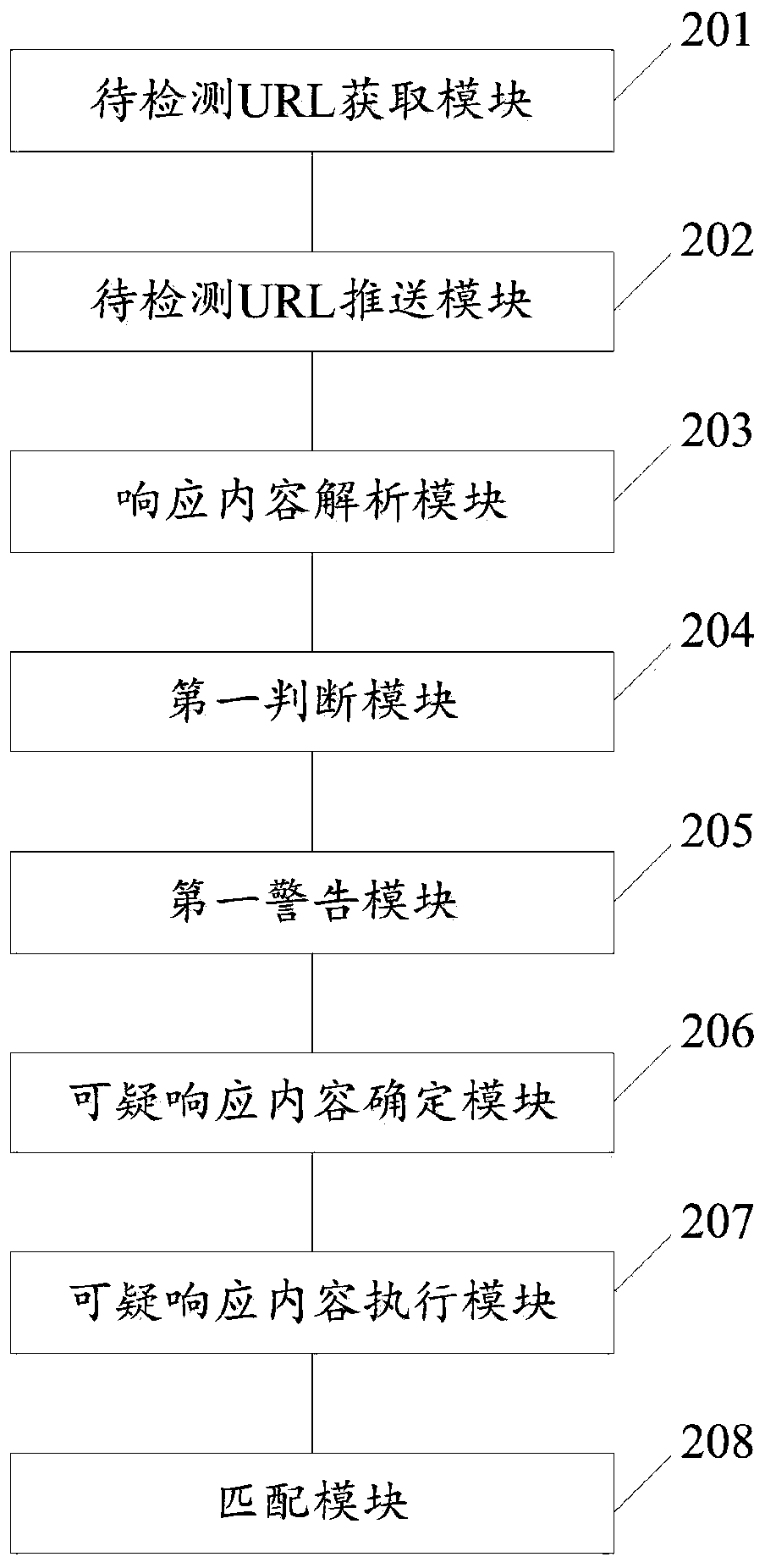

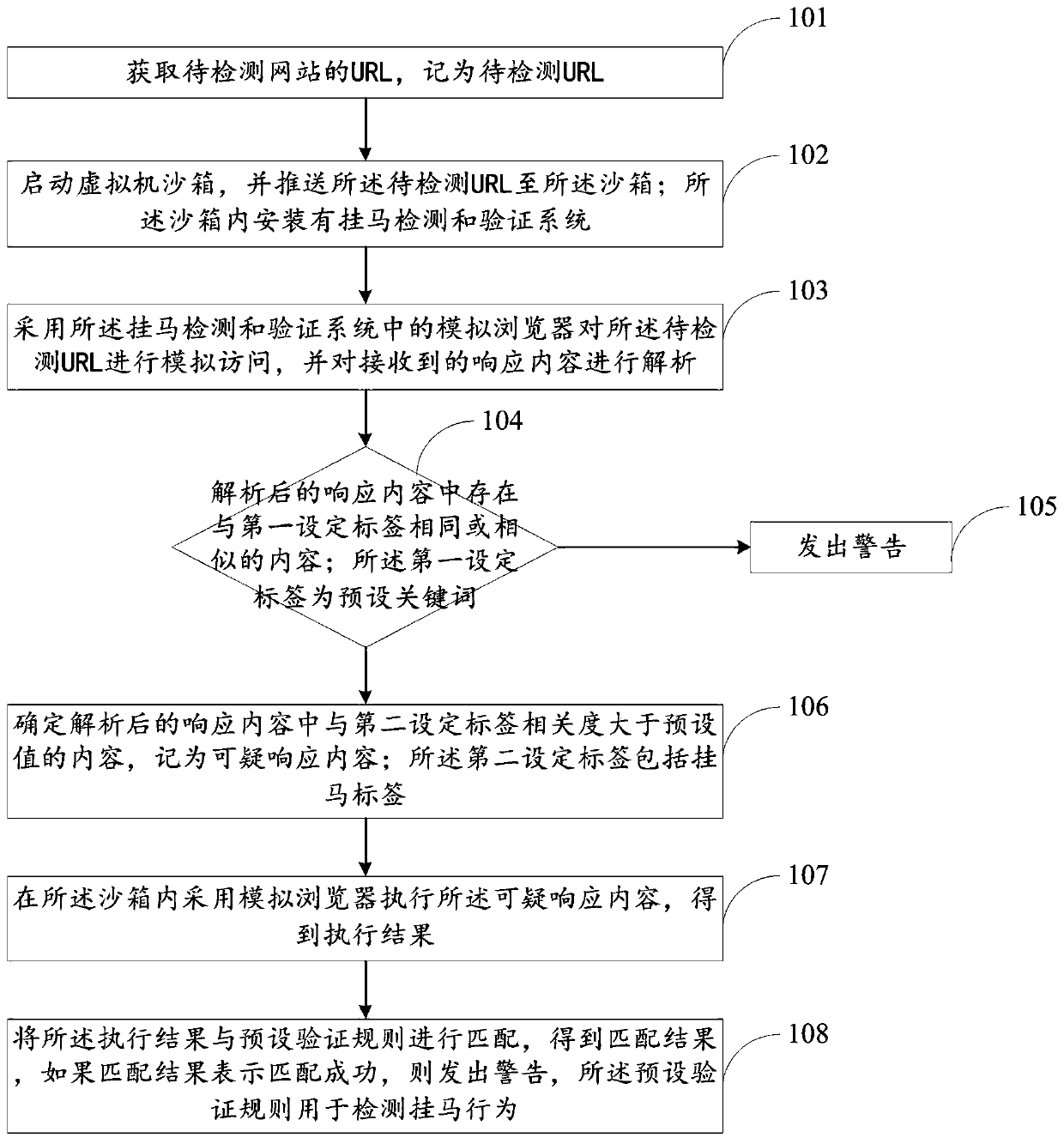

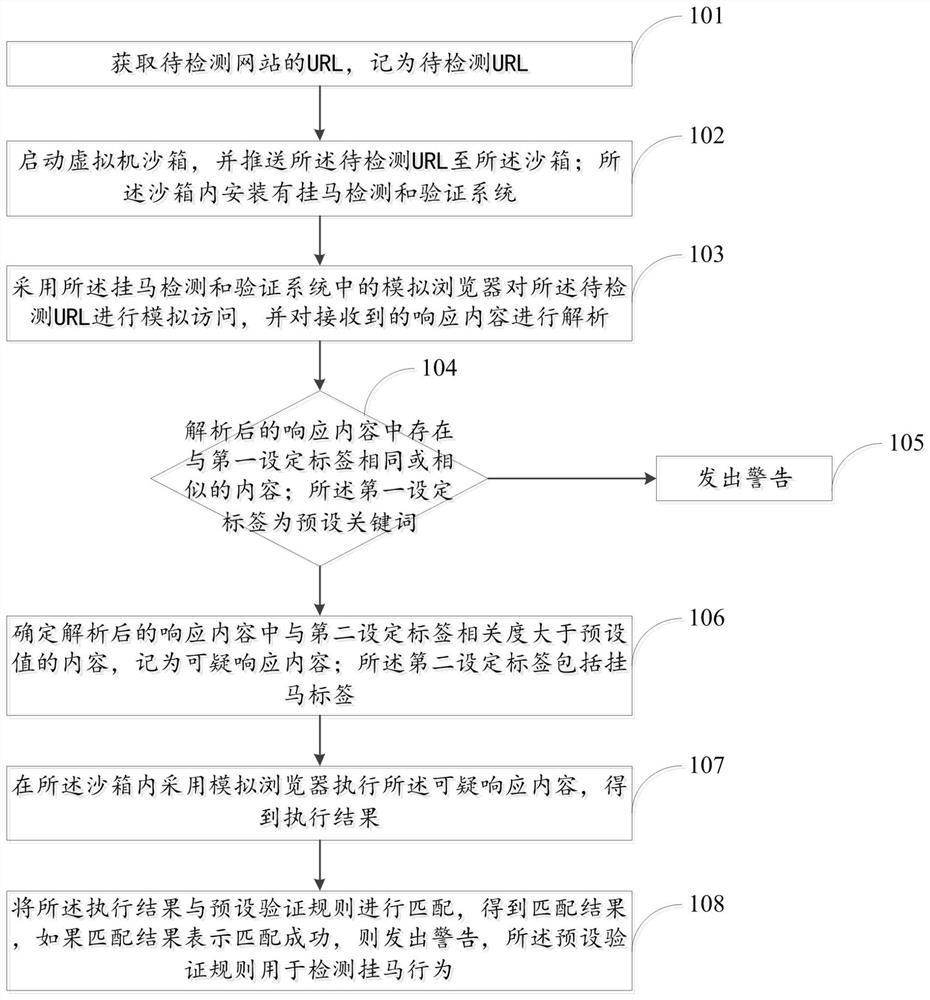

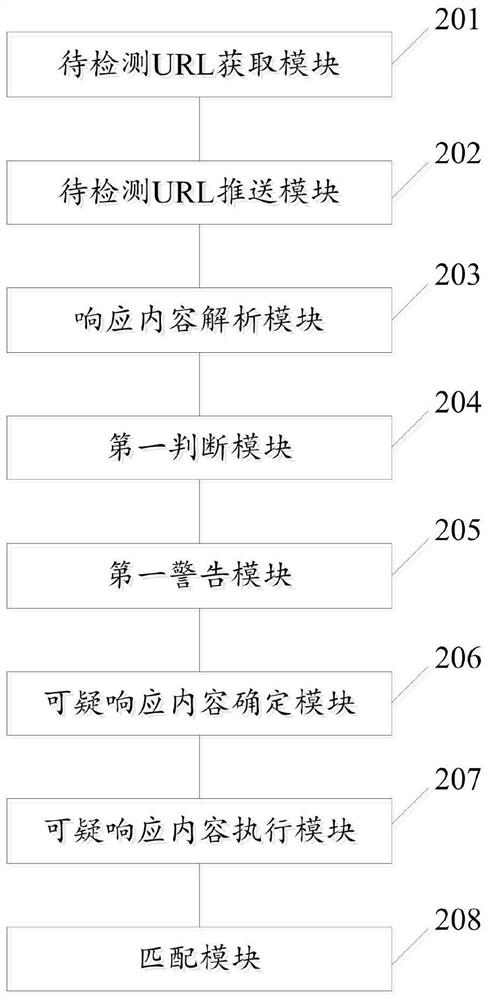

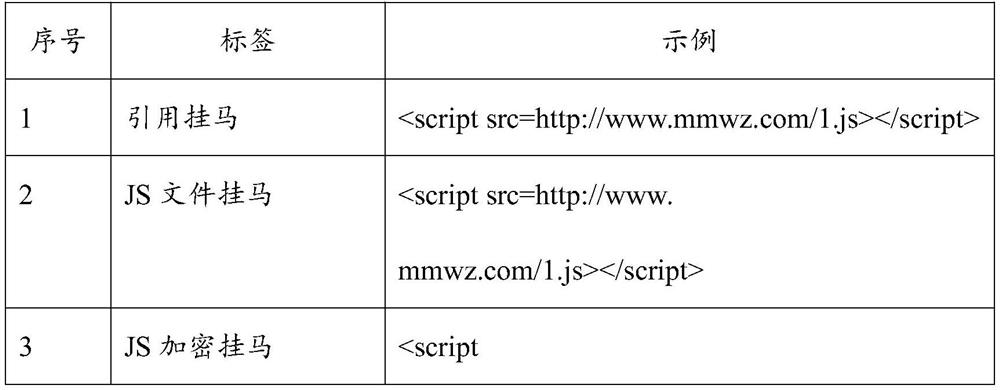

Webpage horse hanging identification method and system

ActiveCN111125704AQuick identificationImprove recognition efficiencyPlatform integrity maintainanceVerification systemComputer security

The invention discloses a webpage horse hanging identification method and system. The method comprises the steps of obtaining a URL of a to-be-detected website; pushing the URL to be detected to a virtual machine sandbox, wherein a horse hanging detection and verification system is arranged in the sand box; carrying out simulation access on the URL to be detected by adopting a simulation browser in the horse hanging detection and verification system, and analyzing the received response content; judging whether the analyzed response content has content which is the same as or similar to the first set label or not, wherein the first set label is a preset keyword; if so, giving an alarm; determining the content of which the relevancy with a second set label is greater than a preset value in the analyzed response content, and recording the content as suspicious response content, wherein the second set label comprises a horse hanging label; executing the suspicious response content in the sandbox by adopting a simulation browser; and matching the execution result with a preset verification rule for detecting the horse hanging behavior, and if matching succeeds, giving an alarm. The method has the advantage of high horse hanging identification efficiency.

Owner:BEIJING AN XIN TIAN XING TECH CO LTD

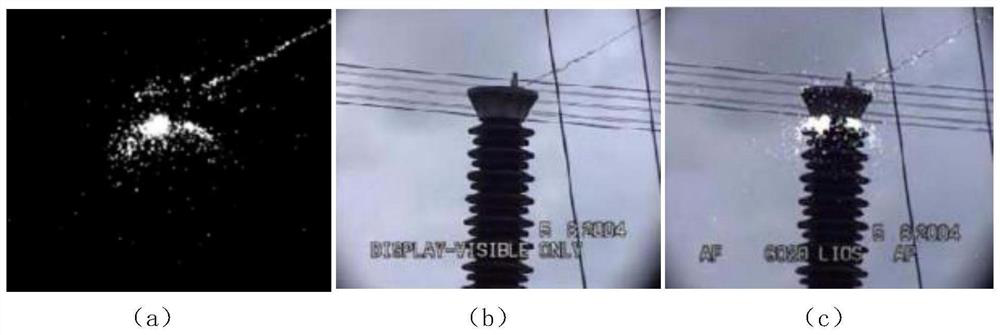

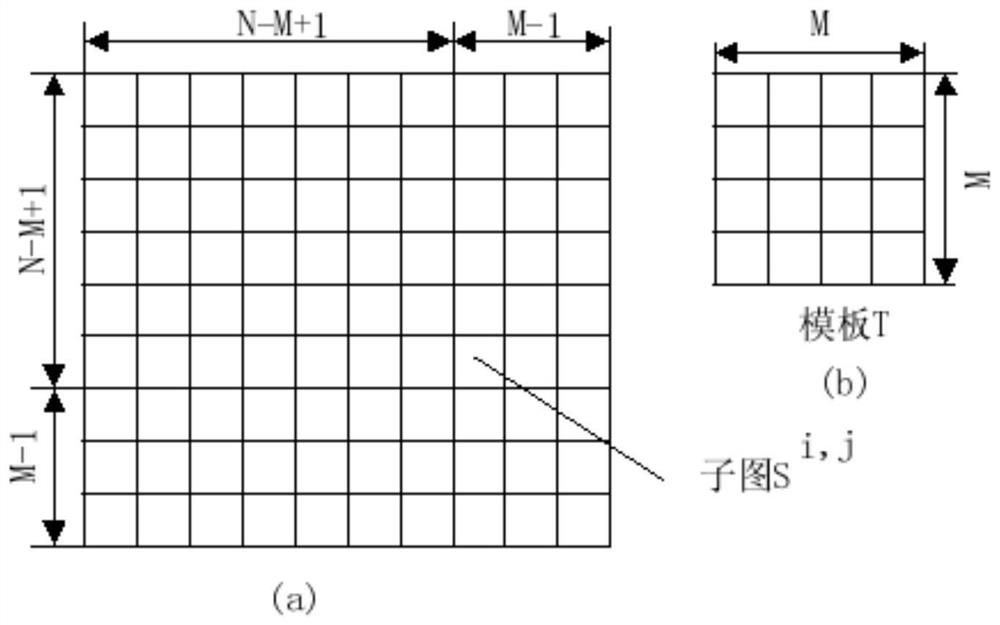

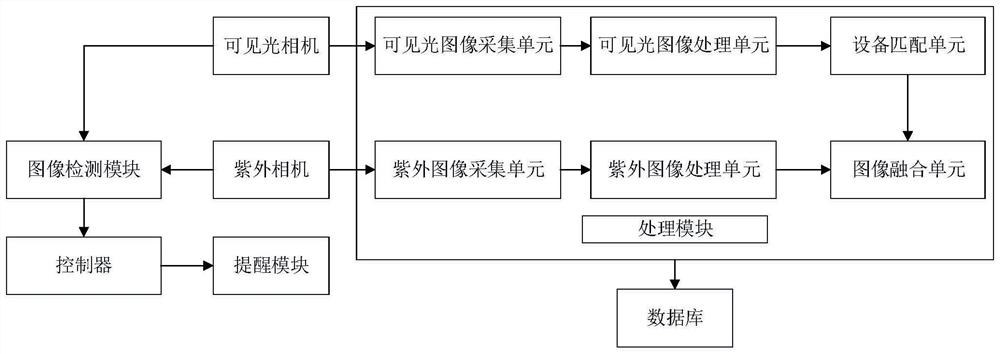

Ultraviolet image corona identification and positioning method and system based on image fusion

PendingCN113870174ASame resolutionReduce mistakesImage enhancementImage analysisImage resolutionMonitoring system

The invention relates to the technical field of image fusion, in particular to an ultraviolet image corona recognition and positioning method and system based on image fusion. According to the invention, when the visible light image and the ultraviolet image are collected, the resolution of the visible light image and the resolution of the ultraviolet image are ensured to be the same, so that the conditions are the same when enhancement and gray processing are carried out later, the system error is reduced, and the fusion precision is improved. According to the method, the equipment on the visible light image is matched with the equipment in the database, which equipment generates corona can be automatically identified without manual identification, and the method can be associated with a rear-end monitoring system to give a prompt about which equipment generates corona. Equipment templates in the database comprise insulation equipment image templates such as a transformer image template and an insulator image template.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD

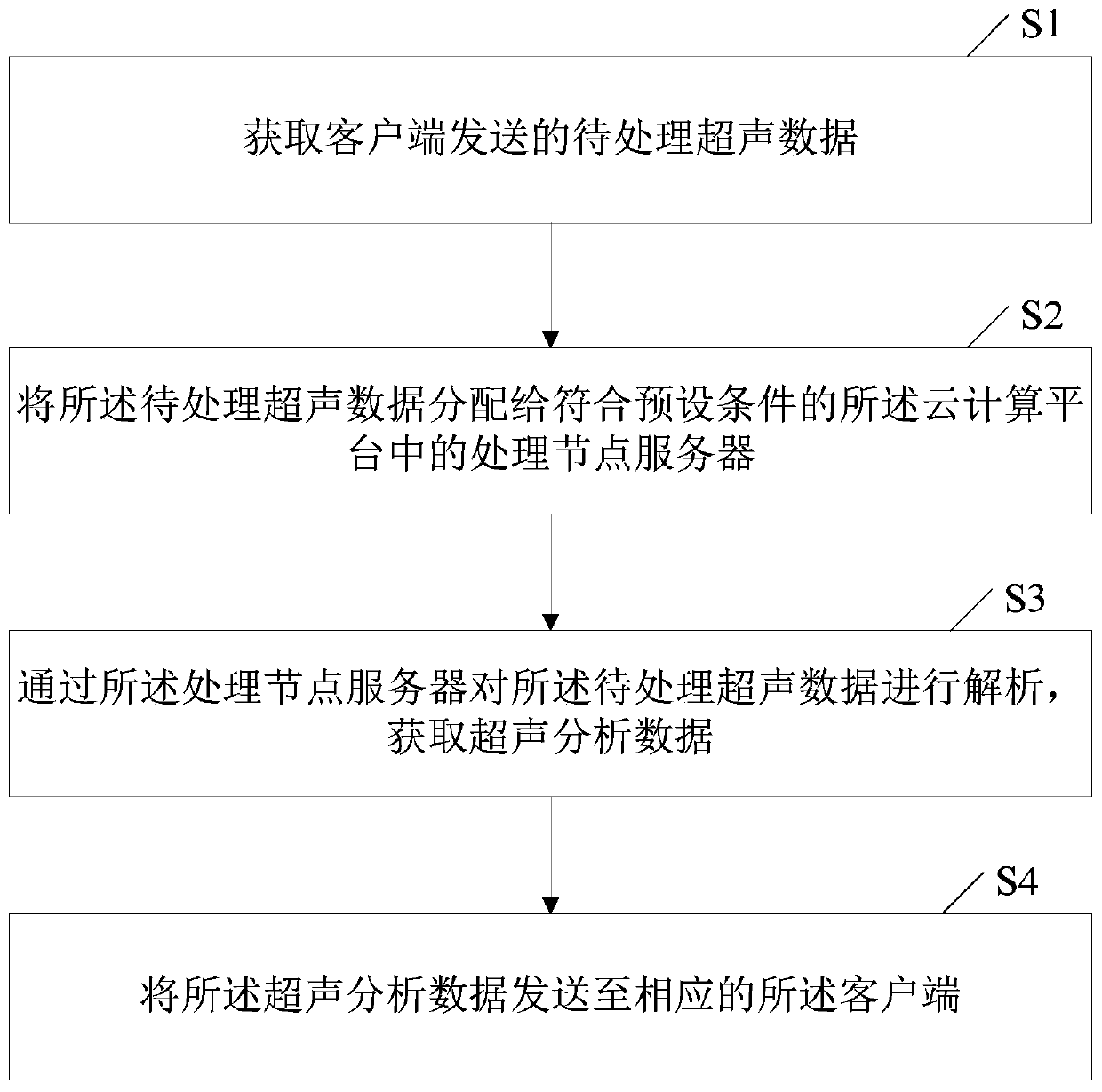

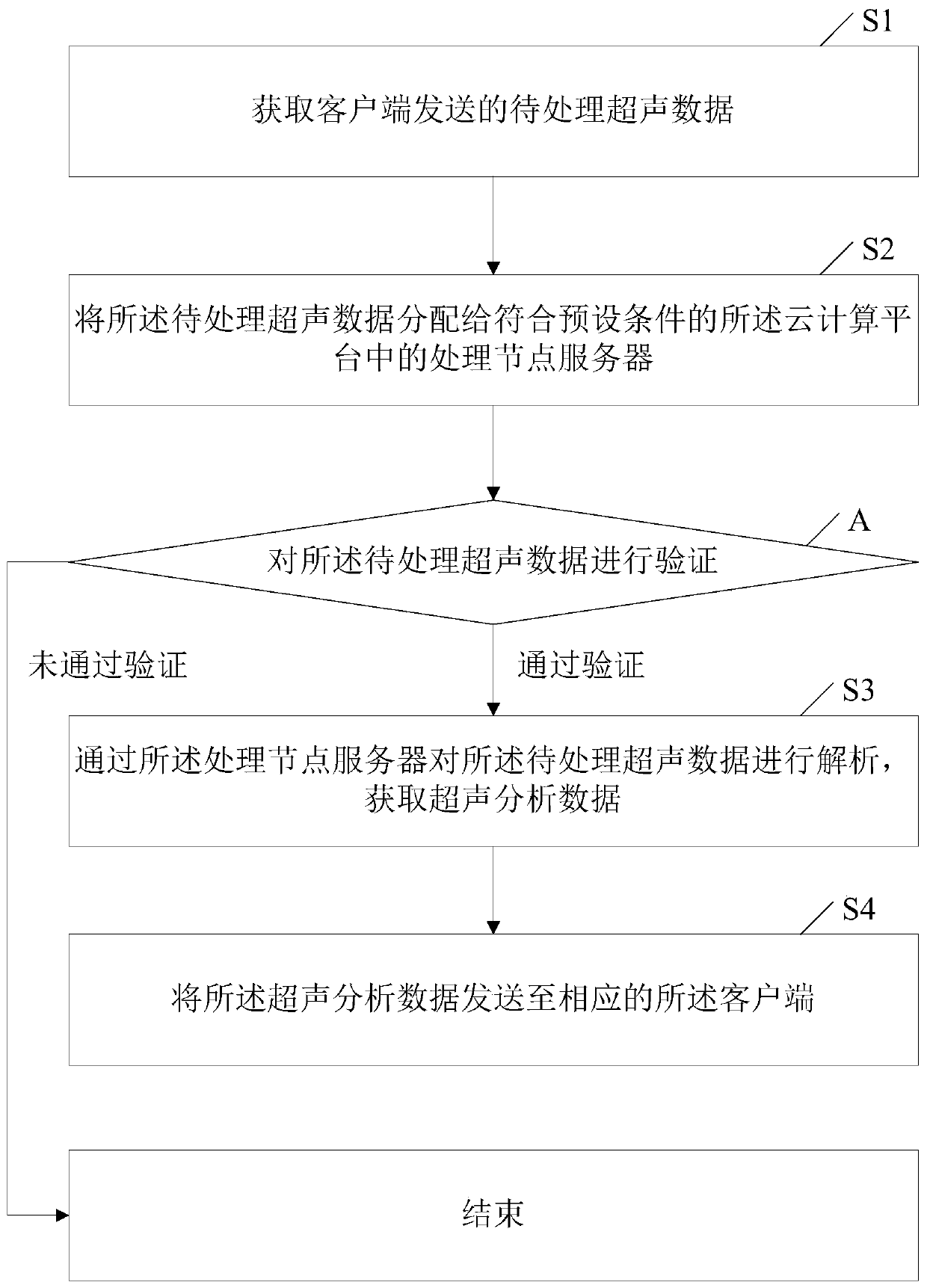

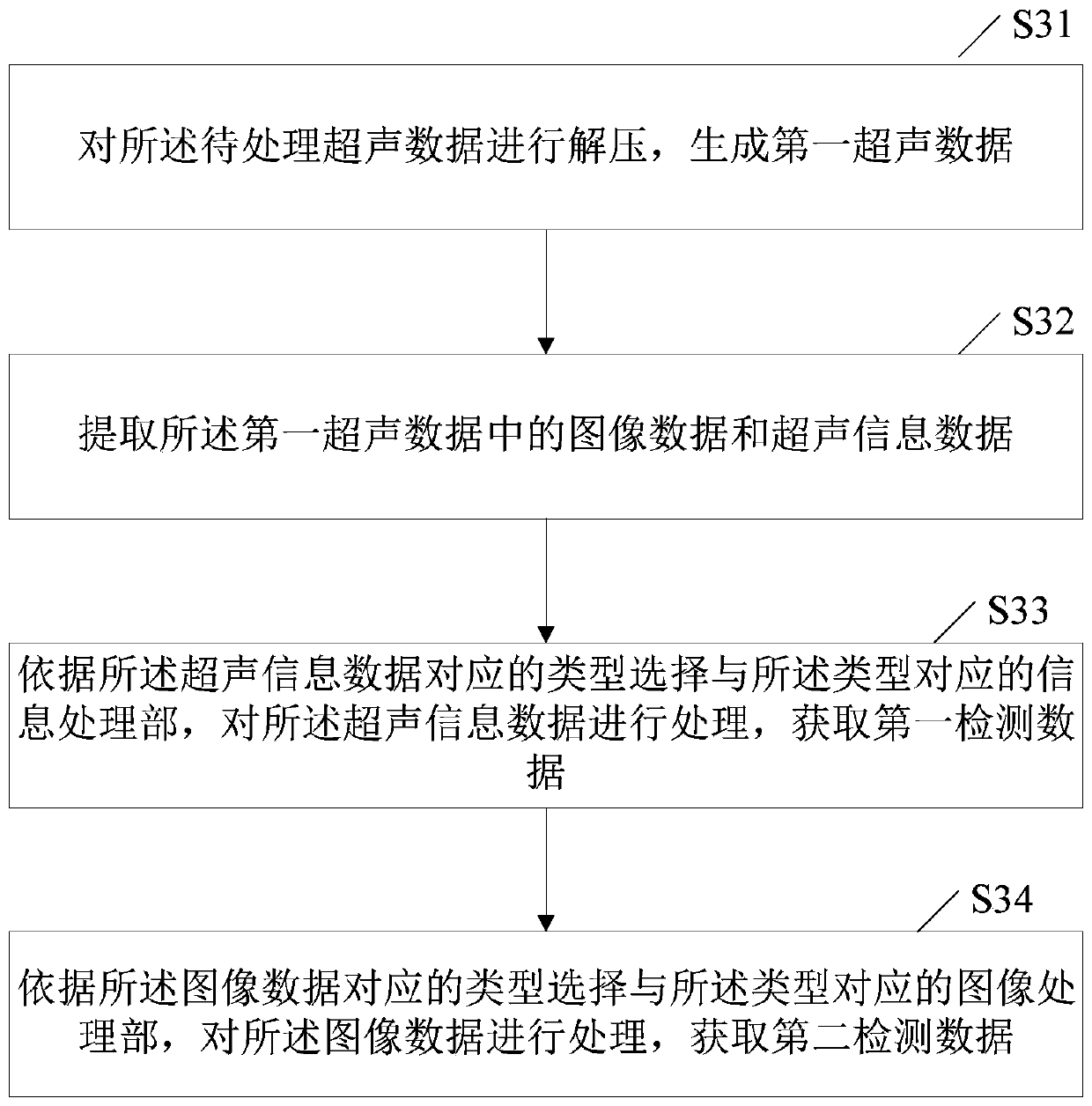

Ultrasonic image processing method and system

PendingCN111105863ARealize automatic identificationSmall amount of calculationMedical automated diagnosisMedical imagesComputer hardwareEngineering

The invention discloses an ultrasonic image processing method and system, and belongs to the field of data management. The ultrasonic image processing method comprises the following steps that to-be-processed ultrasonic data sent by a client is distributed to a processing node server in a cloud computing platform meeting a preset condition; the processing node server analyzes the to-be-processed ultrasonic data, obtains the ultrasonic analysis data and sends the ultrasonic analysis data to the corresponding client, so that the purpose of automatically identifying the ultrasonic data is achieved, manual identification is not needed, and the condition of missed diagnosis is avoided. Meanwhile, the cloud computing platform is adopted for ultrasonic data analysis, so that the calculated amountof local equipment (such as ultrasonic equipment, workstations or PACS of hospitals and the like) is reduced.

Owner:上海深至信息科技有限公司

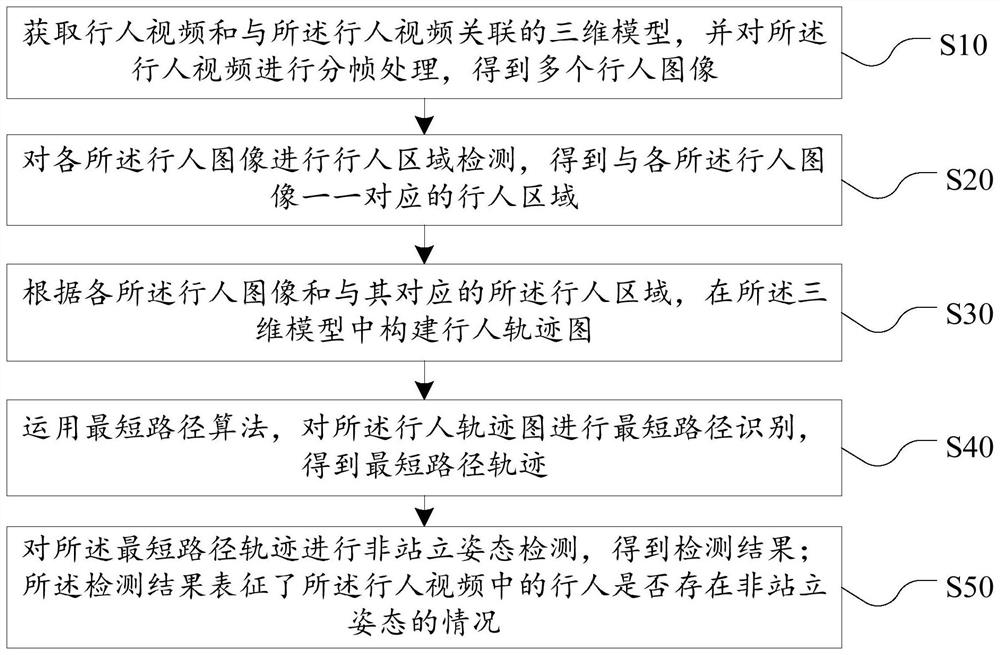

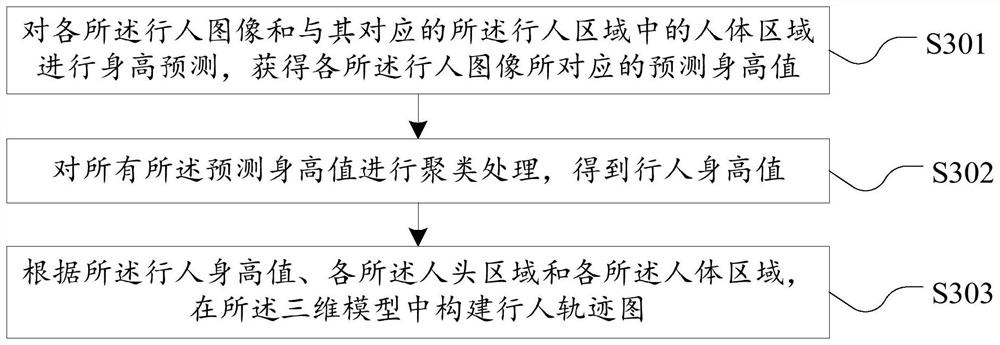

Non-standing posture detection method and device, computer equipment and storage medium

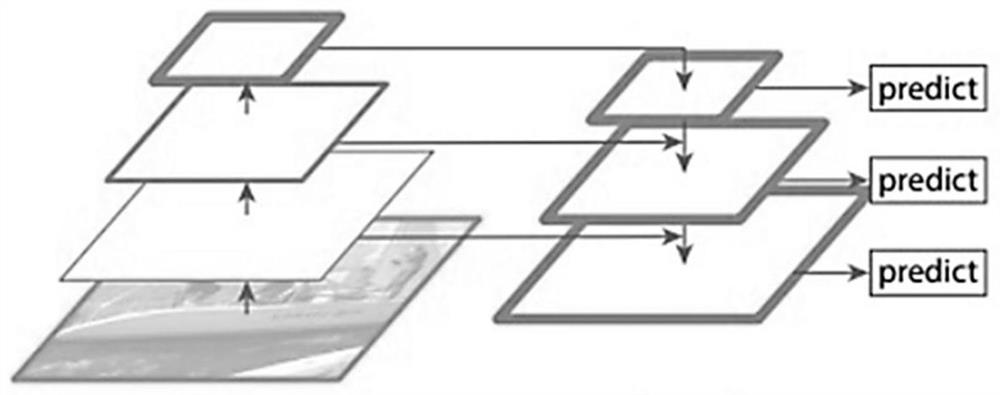

PendingCN114495266AAutomatic recognitionAccurate identificationCharacter and pattern recognitionNeural architecturesShort path algorithmComputer graphics (images)

The invention relates to the technical field of artificial intelligence, and discloses a non-standing posture detection method and device, computer equipment and a storage medium, and the method comprises the steps: obtaining a pedestrian video and a three-dimensional model associated with the pedestrian video, and carrying out the framing processing of the pedestrian video, and obtaining a plurality of pedestrian images; performing pedestrian area detection on each pedestrian image to obtain pedestrian areas in one-to-one correspondence with the pedestrian images; according to the pedestrian images and the pedestrian areas corresponding to the pedestrian images, constructing a pedestrian trajectory graph in the three-dimensional model; performing shortest path identification on the pedestrian trajectory graph by using a shortest path algorithm to obtain a shortest path trajectory; and performing non-standing posture detection on the shortest path track to obtain a detection result. Therefore, whether the pedestrian video has the non-standing posture segment or not is accurately, scientifically and automatically detected, and the accuracy and efficiency of non-standing posture detection are improved.

Owner:SHENZHEN INTELLIFUSION TECHNOLOGIES CO LTD

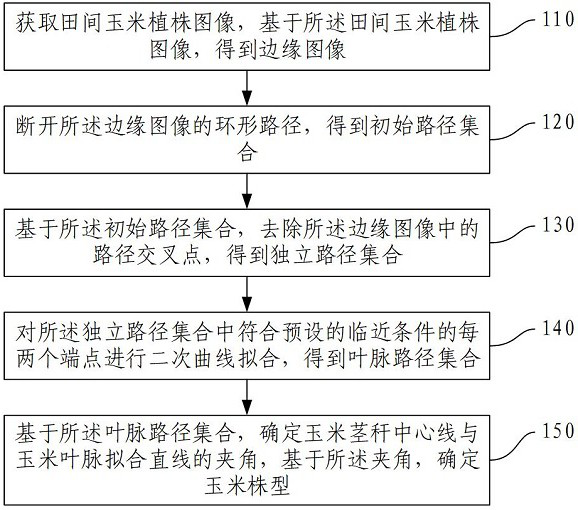

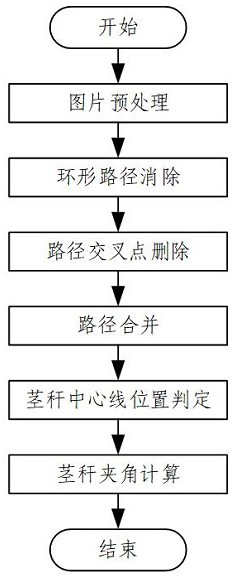

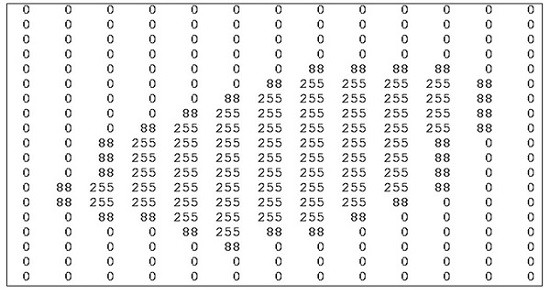

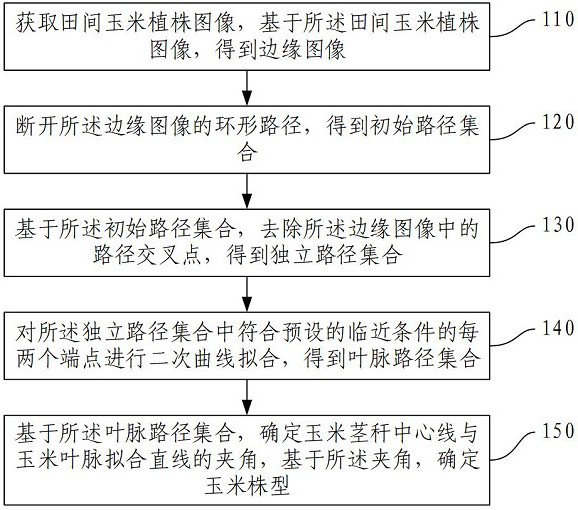

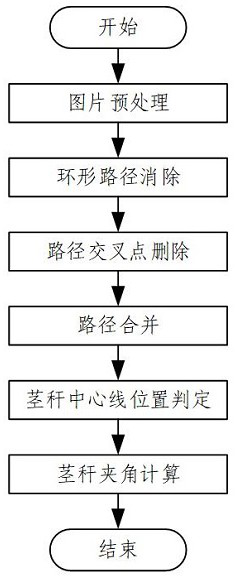

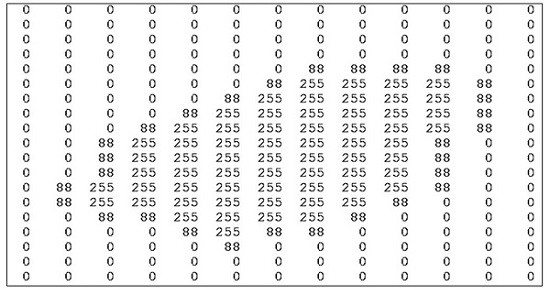

Corn plant type identification method and device, electronic equipment and storage medium

ActiveCN114332667AImproved ease of useImprove collection efficiencyCharacter and pattern recognitionAgricultural engineeringAgricultural science

The invention provides a corn plant type identification method and device, electronic equipment and a storage medium, and the method comprises the steps: obtaining a field corn plant image, and obtaining an edge image based on the field corn plant image; based on the edge image, disconnecting an annular path of the edge image to obtain an initial path set; removing multi-path connection points corresponding to the field corn plant image based on the initial path set to obtain a path endpoint set; performing quadratic curve fitting on every two endpoints in the path endpoint set in pairs to obtain a target path set; and based on the target path set, determining an included angle between the center line of the corn stalk and the corn vein fitting straight line, and based on the included angle, determining the corn plant type. According to the method provided by the invention, the corn plant type can be automatically judged through the field corn plant image, manual identification is not needed, the plant type data acquisition efficiency and the accuracy of corn plant type judgment are greatly improved, and a support is provided for variety evaluation automation and commercial breeding development.

Owner:北京市农林科学院信息技术研究中心

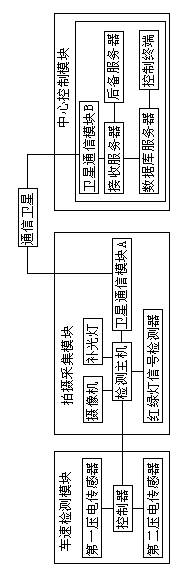

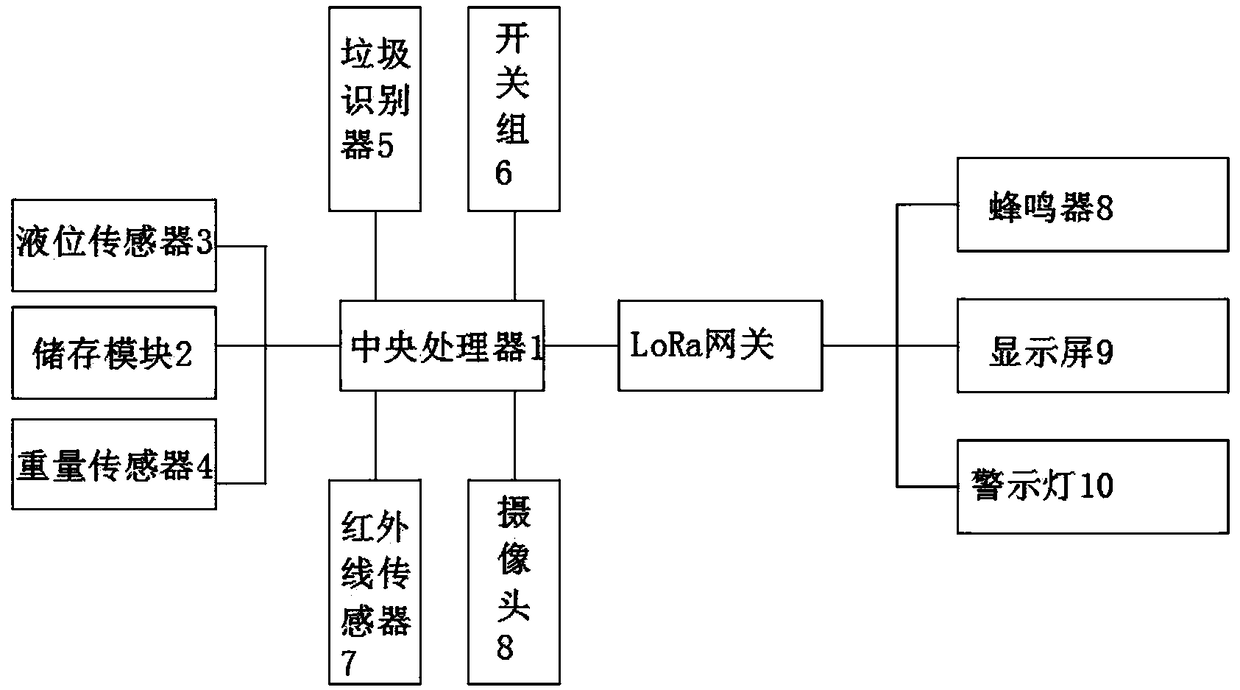

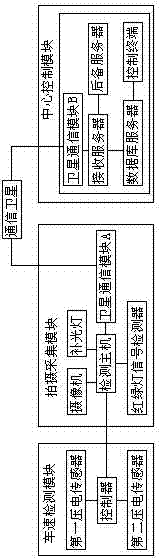

Park garbage monitoring system based on LoRa Wide Area Network (LoRaWAN)

InactiveCN109062123ANo need for manual identificationReasonable handlingProgramme controlComputer controlElectricityMonitoring system

The invention relates to a park garbage monitoring system based on a LoRa Wide Area Network (LoRaWAN). The system comprises a central processing unit (CPU), wherein the CPU is electrically connected with both a garbage monitoring system and an alarm system through a LoRa gateway; the garbage monitoring system comprises infrared sensors, cameras, a switch group and garbage identifiers, which are all electrically connected with the CPU; the switch group comprises switches which are respectively connected with recyclable garbage bins, snack garbage bins, harmful garbage bins and other garbage bins; and the alarm system comprises buzzers, display screens and alarm lights which are all electrically connected with the CPU. Therefore, the system provided by the invention has the advantages that garbage can be accurately treated, and the garbage amount can be more effectively monitored.

Owner:河南汇纳科技有限公司

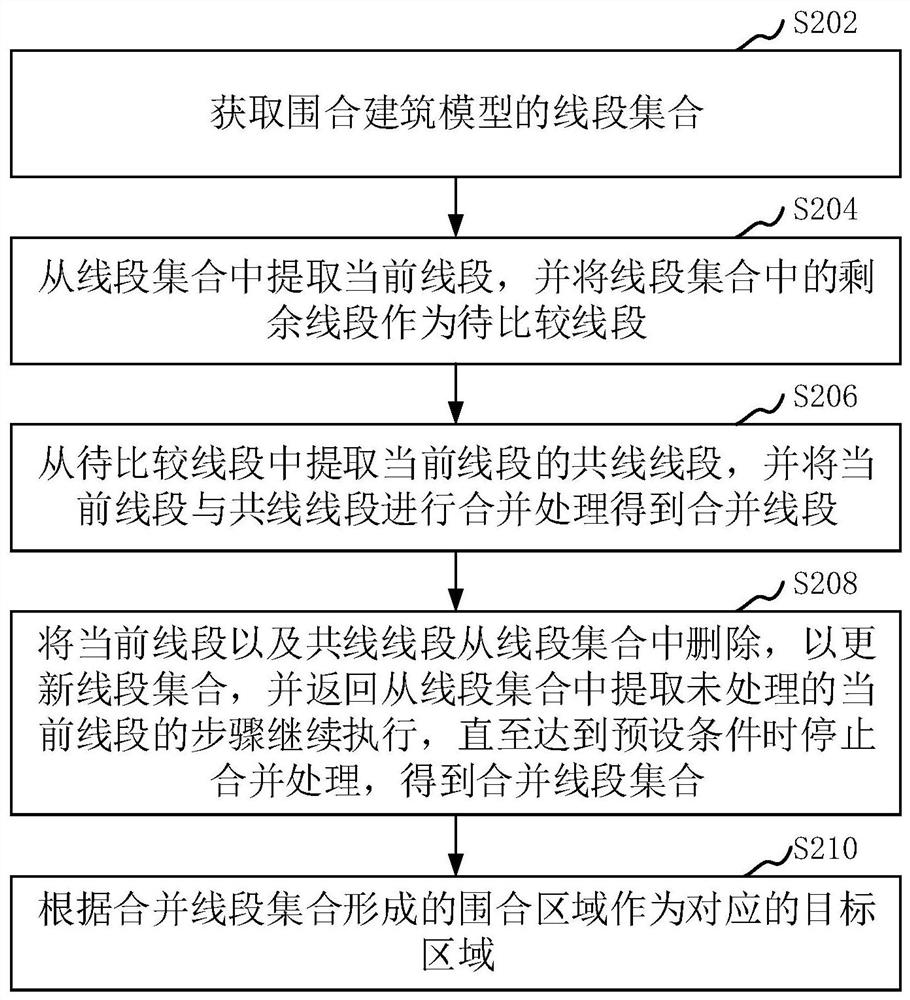

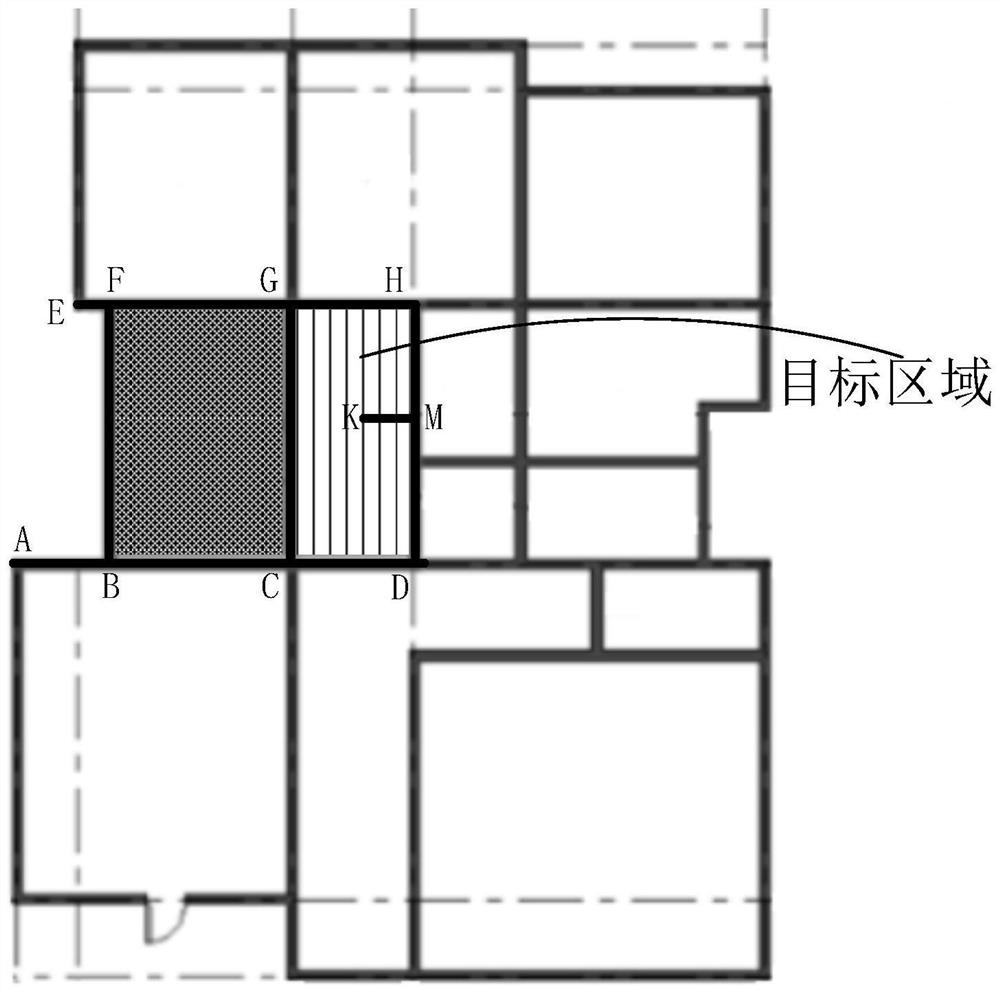

Method, device, computer equipment and storage medium for determining target area of building

ActiveCN112287429BImprove production efficiencyImprove processing efficiencyGeometric CADDrawing from basic elementsAlgorithmDatabase

The present application relates to a method, device, computer equipment and storage medium for determining a target area of a building. The method includes: obtaining a set of line segments enclosing the building model; extracting the current line segment from the set of line segments, and using the remaining line segments in the set of line segments as the line segments to be compared; extracting the collinear line segment of the current line segment from the line segments to be compared, and using the current line segment Merge with the collinear segment to obtain the merged segment; delete the current segment and the collinear segment from the segment set to update the segment set, and return to the step of extracting the unprocessed current segment from the line segment set to continue until the preset condition is met When the merging process is stopped, the merged line segment set is obtained; the enclosed area formed according to the merged line segment set is used as the corresponding target area. The method can improve the efficiency of determining the target area.

Owner:久瓴(江苏)数字智能科技有限公司

A method and device for automatically collecting malicious software

ActiveCN102609649BRealize automatic collectionNo need for manual identificationPlatform integrity maintainanceDependabilityMalware

The invention provides a method and a device for collecting malicious software automatically, wherein the method comprises the following steps: S1, scanning web pages through a simulative browser, identifying and capturing a malicious code of the scanned web pages; and S2, constructing a malicious code executing environment to capture the malicious code so as to obtain the malicious software. The method can realize to collect the malicious software automatically without manual identification; therefore, efficiency is increased greatly; in addition, the method starts to identify the malicious code so as to obtain the malicious software without a method of collecting the static characteristics of the malicious software; the malicious software including the malicious code can be collected no matter the malicious software uses deformation methods; and reliability and relevance ratio are improved greatly.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

Corn plant type identification method, device, electronic device and storage medium

ActiveCN114332667BEasy to operateConforms to the characteristics of natural bending and droopingCharacter and pattern recognitionEdge mapsAgricultural engineering

Owner:北京市农林科学院信息技术研究中心

A method and system for identifying Trojan horses on webpages

ActiveCN111125704BQuick identificationNo need for manual identificationPlatform integrity maintainanceWeb siteEngineering

The invention discloses a method and a system for identifying a webpage hanging horse. The method comprises: obtaining the URL of the website to be detected; and pushing the URL to be detected to a virtual machine sandbox; a hanging horse detection and verification system is installed in the sandbox; using a simulated browser in the hanging horse detection and verification system to detect the URL Simulate the access, and analyze the received response content; judge whether there is the same or similar content as the first setting label in the analyzed response content; wherein, the first setting label is a preset keyword; if it exists, Then issue a warning; determine that the content of the response content after parsing is more relevant than the preset value with the second setting tag, and record it as suspicious response content; wherein, the second setting tag includes the tag of hanging horse; in the sandbox, the simulated The browser executes suspicious response content; matches the execution result with the preset verification rules used to detect trolling behavior, and issues a warning if the match is successful. The invention has the advantage of high identification efficiency of hanging horses.

Owner:BEIJING AN XIN TIAN XING TECH CO LTD

Federated model training, customer profiling method, device, equipment and medium

ActiveCN113283185BShorten learning modeling cycleFast trainingCharacter and pattern recognitionDesign optimisation/simulationFeature extractionEngineering

The present invention relates to the technical field of user portraits, and provides a federated model training, customer portrait method, device, equipment, and medium. The method includes: obtaining a list of participants and an initial customer portrait federation model, and according to a preset screening plan, from the participants Select qualified participants from the list; send the initial customer portrait federation model to each qualified participant; receive the returned model parameters; use the MPI parallel method to extract abnormal features through the malicious parameter detection model, and output each model parameter according to the extracted abnormal features The identification results of the malicious parameters are filtered to obtain the final normal parameters; updates and federated learning are performed to obtain the global customer portrait federated model. The invention realizes the use of the MPI parallel method to extract abnormal features through the malicious parameter detection model, and filter the malicious parameters, automatically remove the malicious parameters provided by the malicious participants, and improve the efficiency and accuracy of federated learning modeling.

Owner:PING AN TECH (SHENZHEN) CO LTD

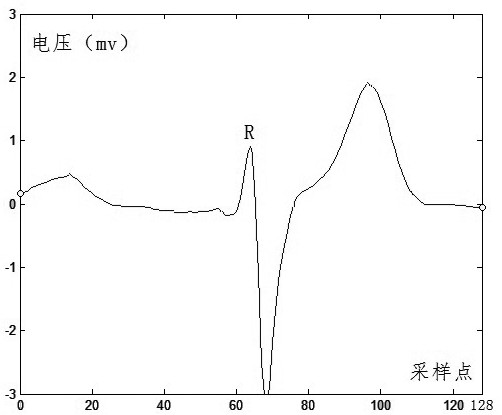

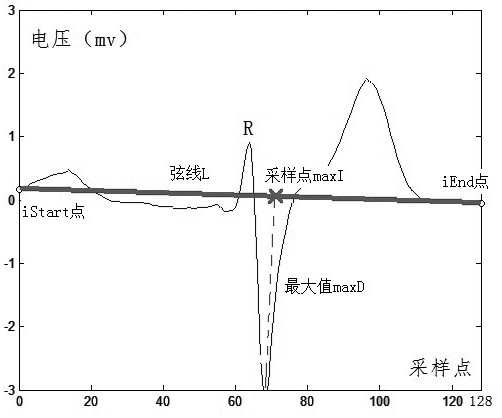

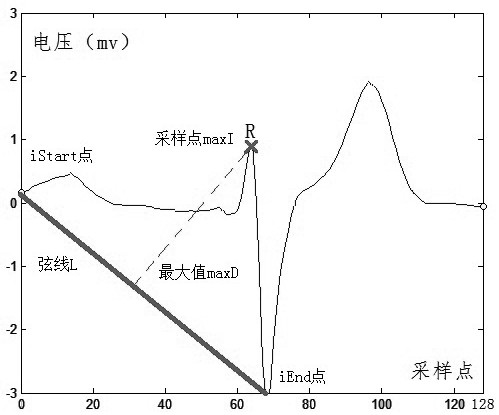

Electrocardiogram artifact analysis method based on optimal scoring strategy

PendingCN114847962ANo need for manual identificationImprove work efficiencyDiagnostic recording/measuringSensorsPattern recognitionEngineering

According to the electrocardiogram artifact analysis method based on the optimal scoring strategy, electrocardiogram artifacts with short duration caused by poor electrode contact, muscle vibration and movement interference introduced in activities can be automatically recognized, and the working efficiency of technicians is greatly improved. According to the technical scheme, the feature inflection points are found in the heart beat sample to be analyzed, the feature inflection points with the features of the Q point, the S point, the T starting point and the T ending point are found in all the feature inflection points, and the feature inflection points which do not conform to the QST combination position features are deleted. All feature inflection point combinations strictly conforming to the features between the Q point and the S point, the features between the S point and the T point and the features between the T starting point and the T ending point at the same time are found, and finally based on feature parameters such as the sharp incisura number of each combination, scoring is conducted through a scoring function, and the electrocardiograph artifacts are found.

Owner:无锡市中健科仪有限公司

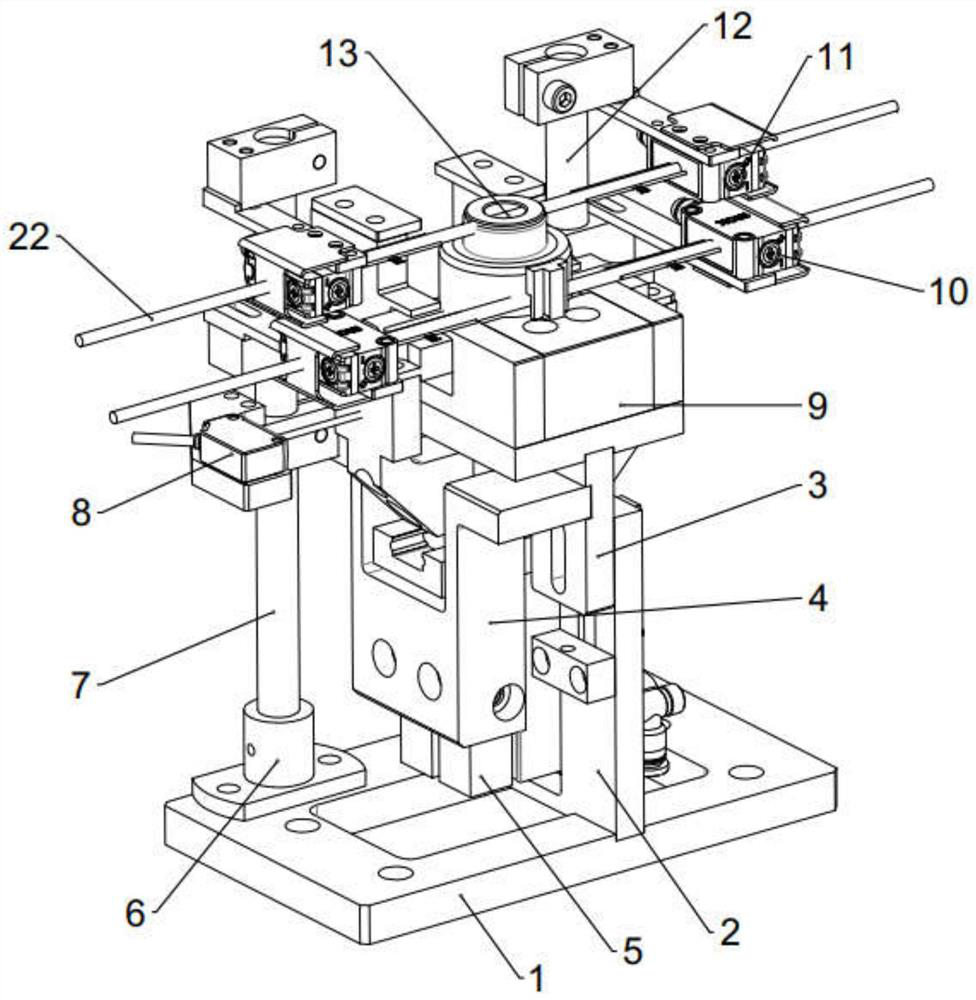

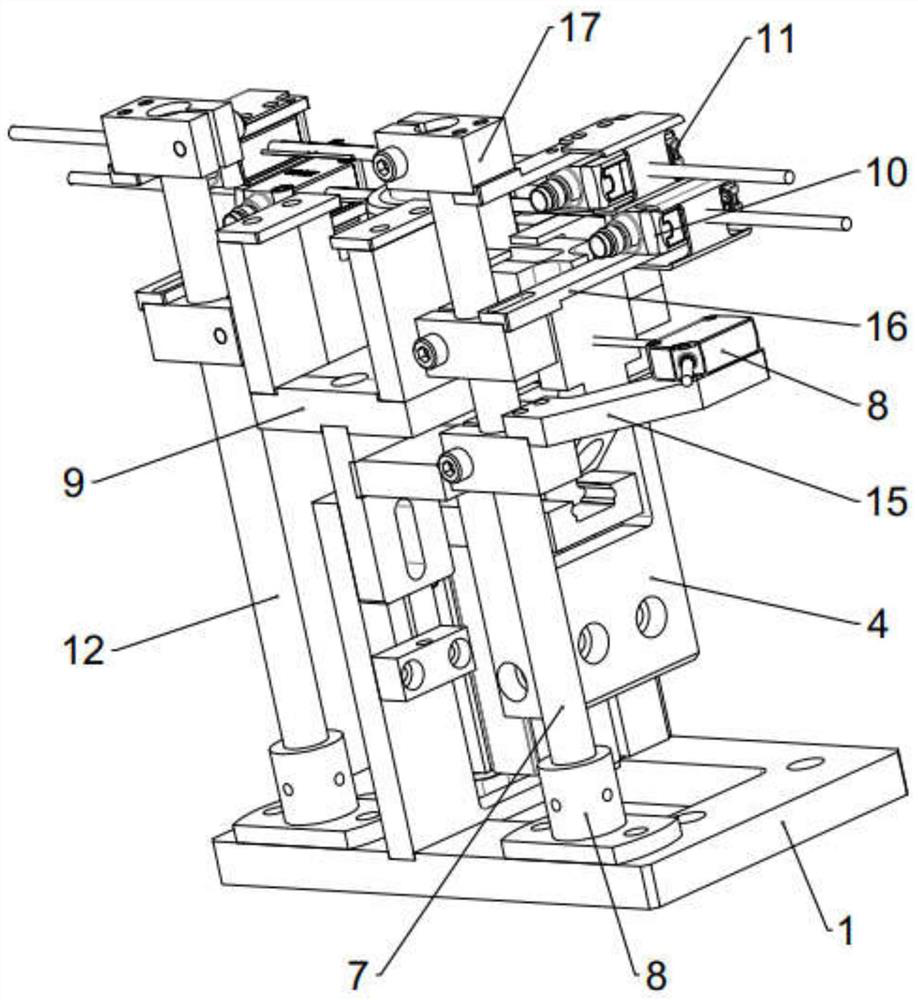

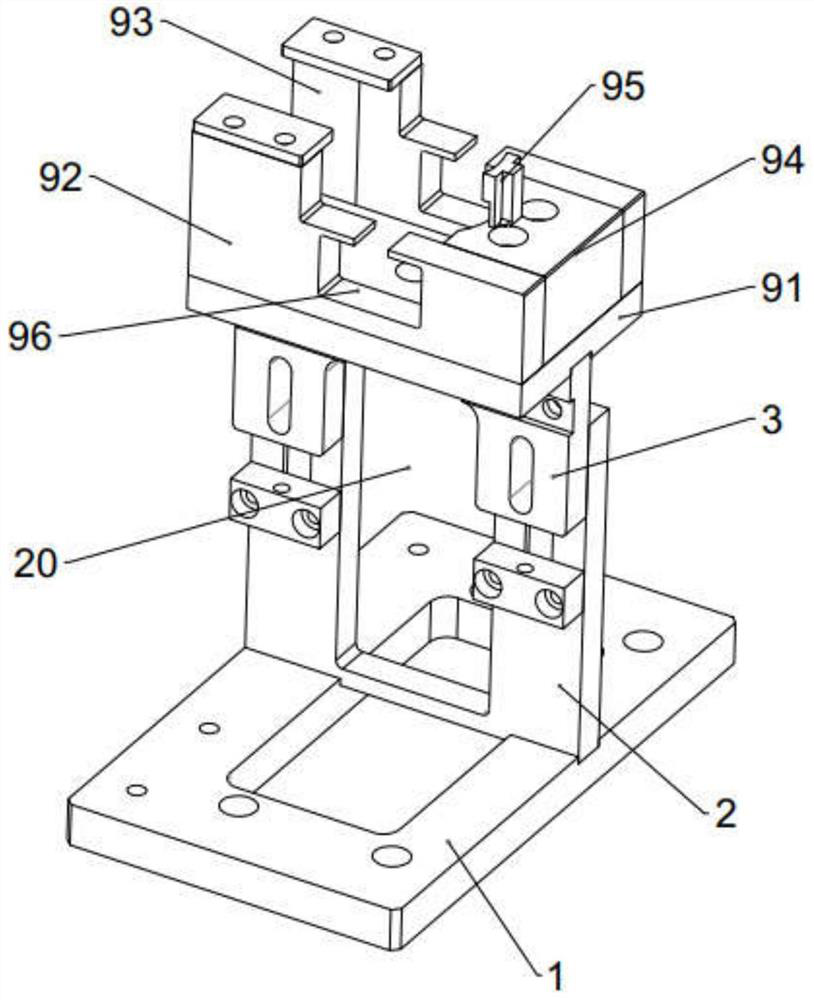

Bush identification device and identification method

PendingCN114812412AAvoid the problem of wrong materialsAutomatic size recognitionUsing optical meansMechanical measuring arrangementsLaser sensorIdentification device

The invention discloses a lining identification device and method. The lining identification device comprises a base, a supporting mechanism, a diameter detection mechanism and a height detection mechanism. The supporting mechanism is mounted on the base and is used for bearing a bushing to be detected; the diameter detection mechanism comprises a clamping jaw cylinder, a clamping jaw and a first laser sensor, the clamping jaw cylinder is used for driving the clamping jaw to clamp the outer surface of the bushing, and the first laser sensor is used for measuring the displacement of the clamping jaw to detect the diameter of the bushing; the height detection mechanism comprises a second laser sensor, and the second laser sensor is used for detecting the height of the bushing. Whether the linings meet the requirements of the work station or not can be automatically recognized, the problem of wrong feeding during manual feeding is avoided, manpower is saved, the production efficiency is improved, the structure is simple, the manufacturing cost is low, and practicability is high.

Owner:卓越(昆山)自动化技术有限公司

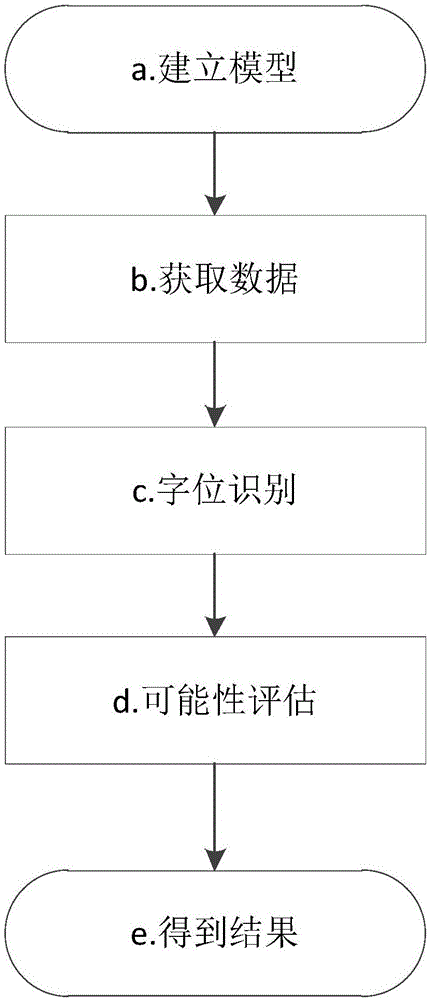

License plate number recognition method based on data model

InactiveCN106326897ANo need for manual identificationReduce labor costsCharacter and pattern recognitionPattern recognitionLicense

The invention provides a license plate number recognition method based on a data model. The license plate number recognition method comprises the following steps that a. a model is established; b. data are acquired; c. character bits are recognized; d. possibility assessment is performed; and e. the result is obtained. Using of license plate fixing nails of special material can be avoided to a great extent through the mode of color range screening, character bit recognition and possibility assessment with no requirement for artificial recognition so that labor cost can be greatly reduced.

Owner:王小兰

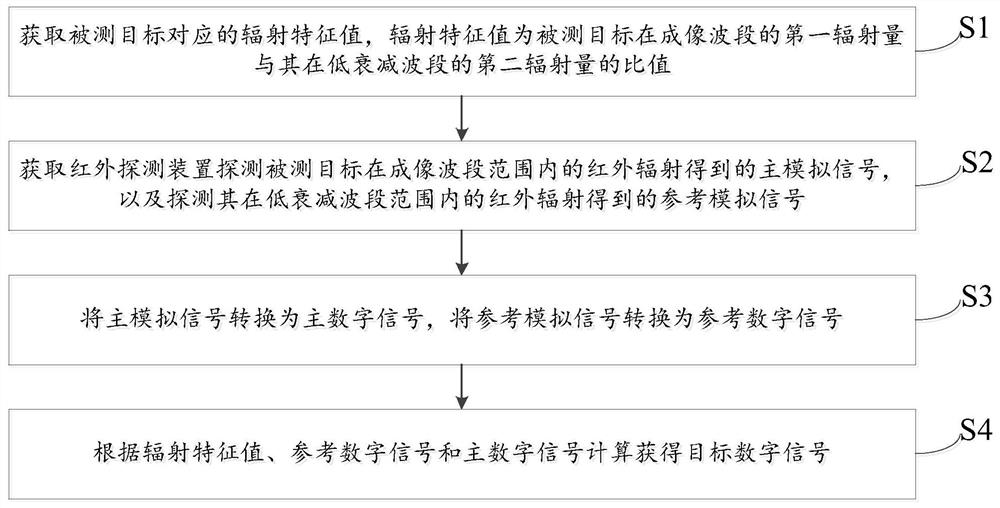

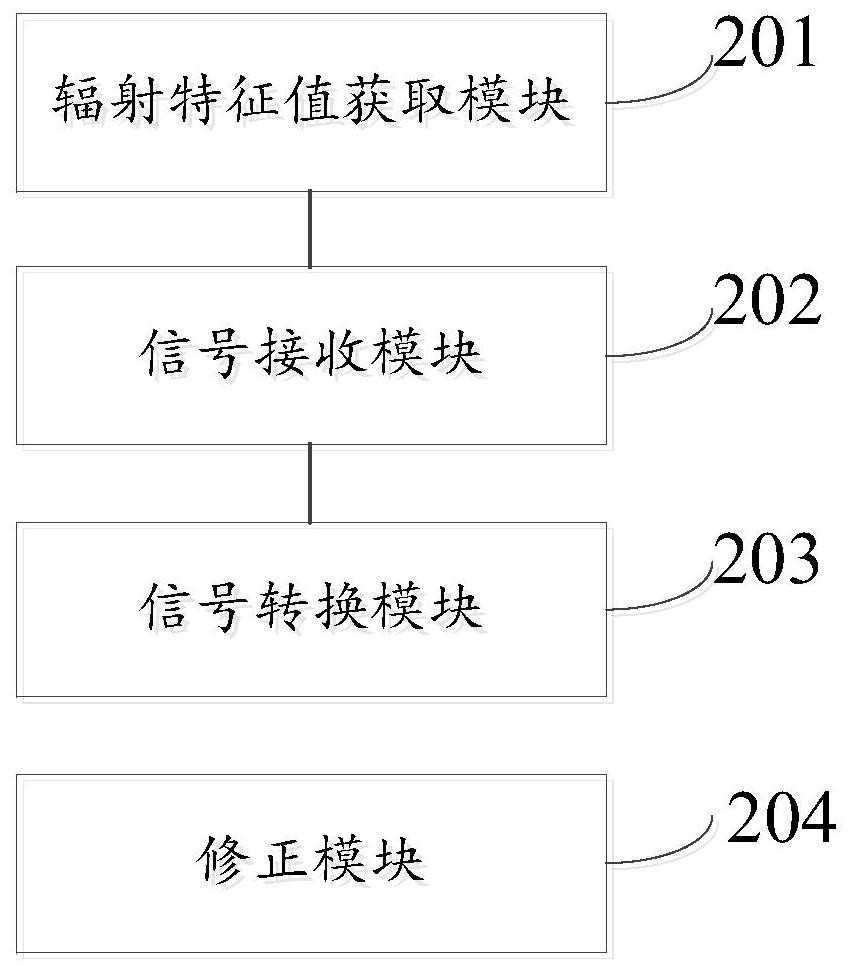

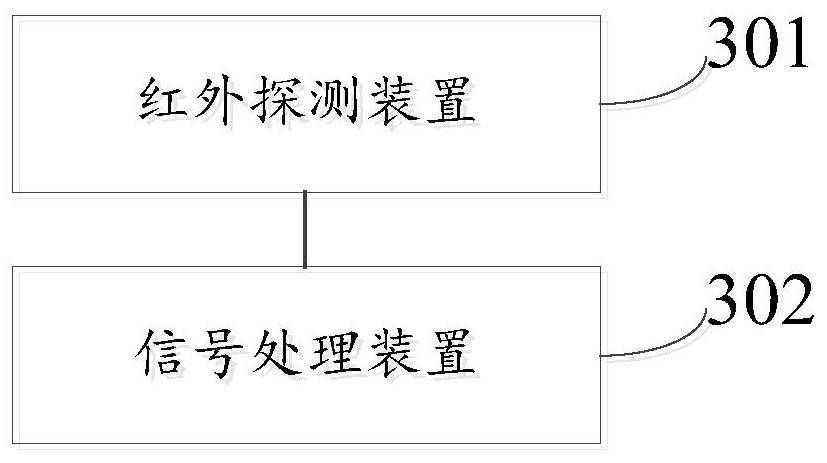

Signal processing method, device and electronic equipment for infrared temperature measurement

ActiveCN112629665BCompensation Error CaseImprove accuracyRadiation thermographyAnalog signalInfrared temperature measurement

The invention discloses a signal processing method, device and electronic equipment for infrared temperature measurement, belonging to the technical field of temperature measurement. The methods include: obtaining the radiation characteristic value corresponding to the measured target; obtaining the main analog signal obtained by detecting the infrared radiation of the measured target in the imaging band range by the infrared detection device, and obtaining the infrared radiation obtained by detecting its infrared radiation in the low attenuation band range The reference analog signal; the main analog signal is converted into the main digital signal, and the reference analog signal is converted into the reference digital signal; the target digital signal is obtained by calculating according to the radiation characteristic value, the reference digital signal and the main digital signal. The invention uses the radiation energy of the measured target in the low-attenuation band and the measured low-attenuation analog signal in the low-attenuation band to correct the actually measured digital signal, and compensates the error caused by the atmospheric attenuation correction caused by the different measured target materials.

Owner:IRAY TECH CO LTD

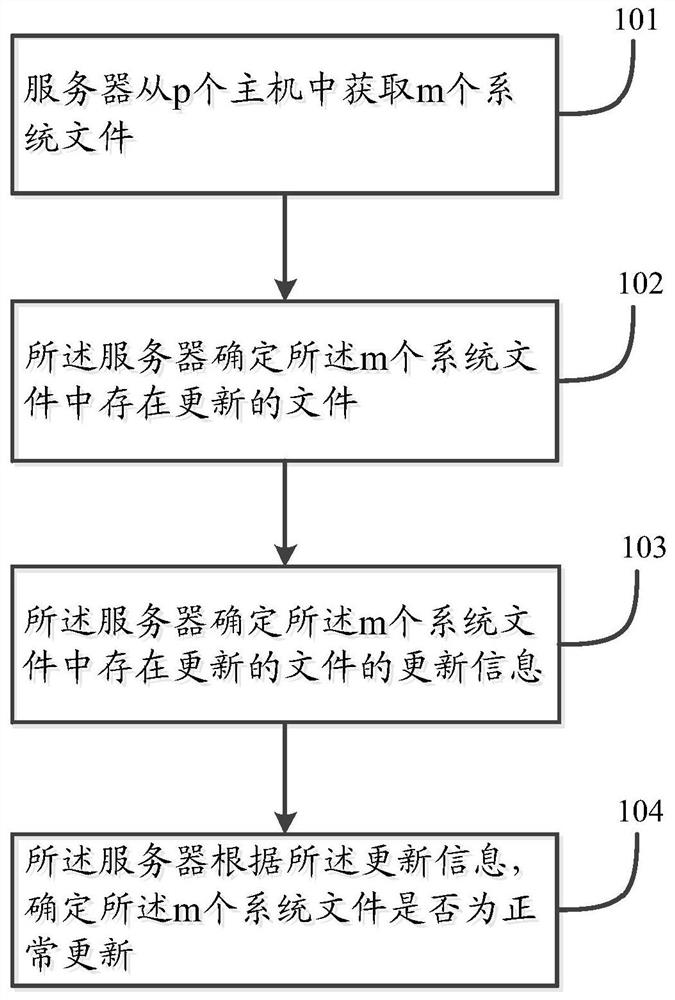

A file update identification method and device

ActiveCN109298970BReduce identification costsRecover in timeRedundant operation error correctionDatabaseServer

The invention discloses a file update identification method and device, which are used for automatically identifying whether a file update in a test environment is a normal update. The scene recognition method for file update includes: the server obtains m system files from p hosts; the server determines the update files of the m system files; the server determines the update information of the update files; the server According to the update information, it is determined whether the m system files are updated normally. This approach reduces the cost of scene recognition for file updates.

Owner:CHINA UNIONPAY

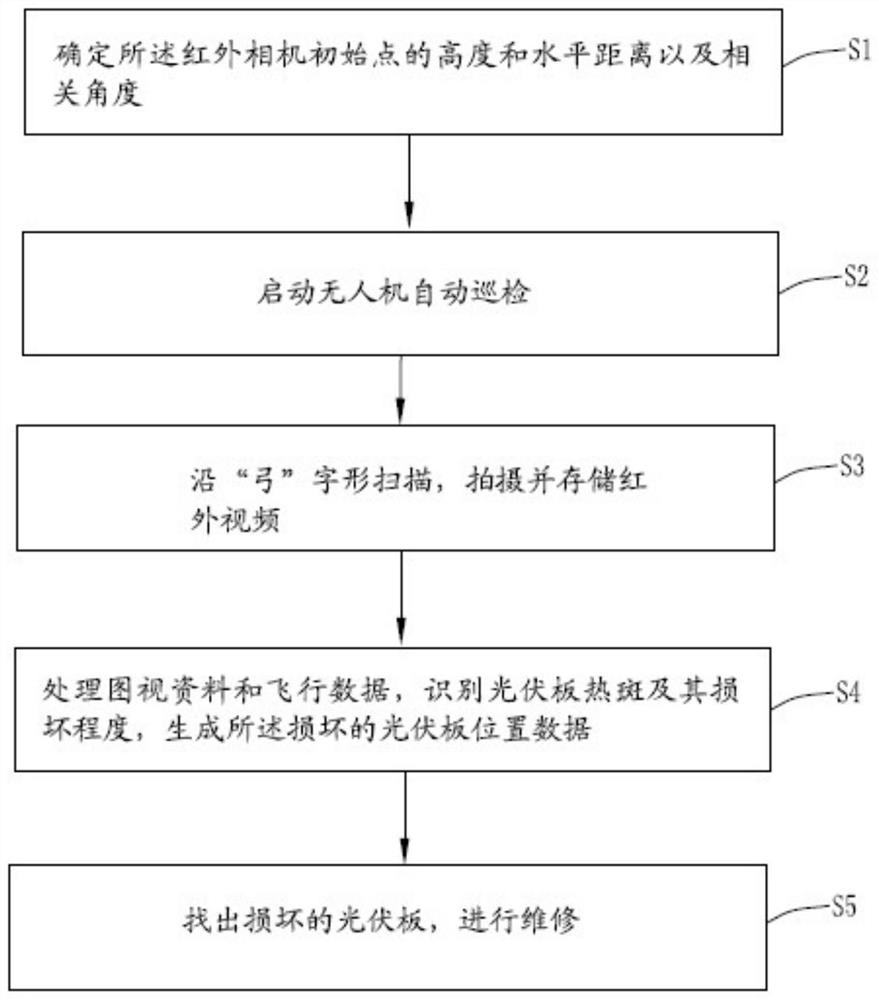

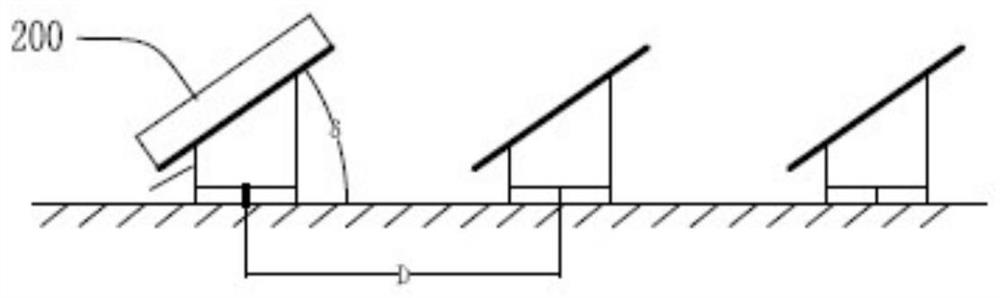

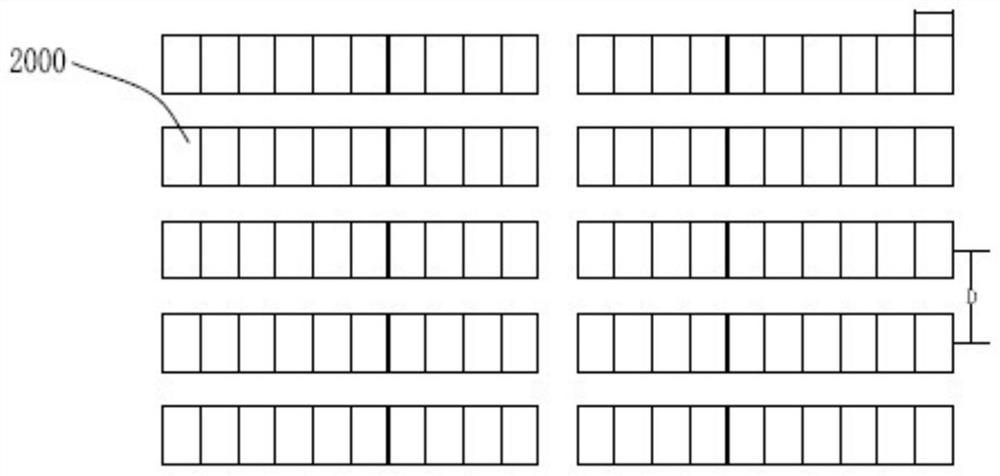

Photovoltaic inspection method based on drone

ActiveCN113031634BNo hot spotsHot spot phenomenon does not requireAttitude controlPosition/course control in three dimensionsEngineeringMaterials science

A photovoltaic inspection method based on an unmanned aerial vehicle of the present invention is characterized in that the method uses an unmanned aerial vehicle to carry an infrared camera for inspection, and the specific steps are as follows: step S1, when the photovoltaic power station generates electricity, determine the initial state of the infrared camera The height, horizontal distance and angle of the point; step S2, start the drone inspection; step S3, scan along the "bow" shape, shoot and store the infrared video; step S4, use the computer to process the image data in the storage medium and flight data, and generate the damaged photovoltaic panel position data; compared with related technologies, this method is more efficient and intelligent.

Owner:深圳市易飞方达科技有限公司

Laminated diode manufacturing process and chip sieve tray thereof

ActiveCN102881587BAvoid damageNo need for manual identificationSemiconductor/solid-state device manufacturingAcid washingElectroplating

The invention relates to a novel laminated diode manufacturing process and a chip sieve tray thereof. The novel laminated diode manufacturing process is characterized by comprising the following steps of forming a wide groove in the P surface or the N surface of a silicon wafer, wherein the groove is 70 to 250 mum in width and 60 to 100 mum in depth; scribing in the way that the center of the bottom of the wide groove serves as a boundary; after filling a lead and sieving a chip, welding and fixing the chip and the lead by using a welding material, and when the chip is sieved, matching a small surface formed by forming the wide groove with a profile hole of the chip sieve tray to identify the polarity of the P surface or the N surface; and sequentially performing acid washing, strip combing, sizing, glue curing, mould pressing, post curing, electroplating, testing, character printing, packaging and goods delivery. Due to the steps of forming the wide groove in the P surface or the N surface of the silicon wafer, scribing in the way that the center of the bottom of the wide groove serves as the boundary, matching the small surface formed by forming the wide groove with the profile hole of the chip sieve tray to automatically identify and adjust the polarity of the P surface or the N surface, manual identification is not required, the efficiency and the accuracy are effectively improved, and the damage to the chip caused by manual adjustment with a nipper is avoided.

Owner:RUGAO DACHANG ELECTRONICS

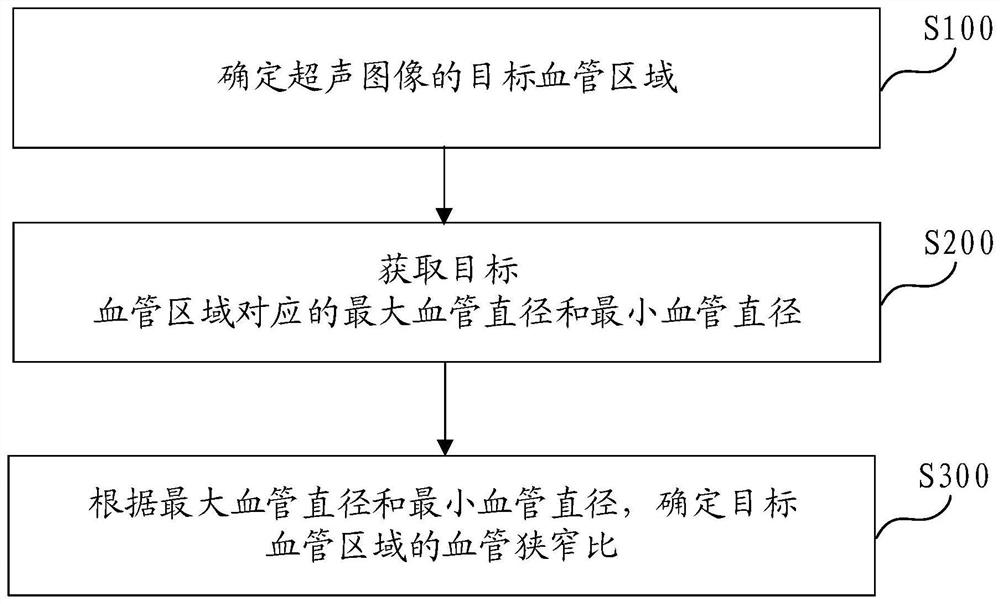

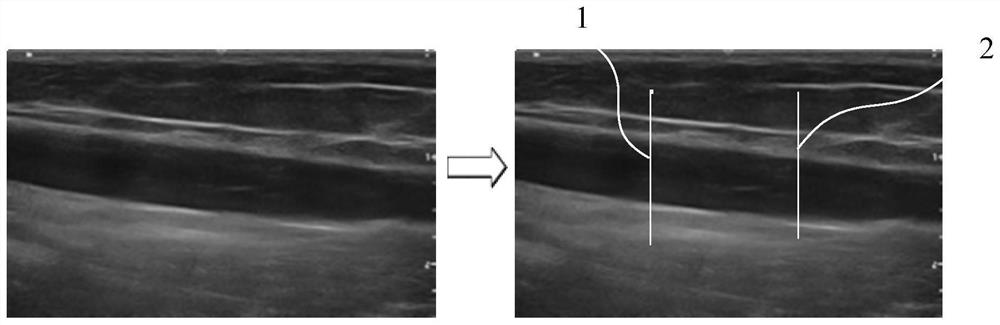

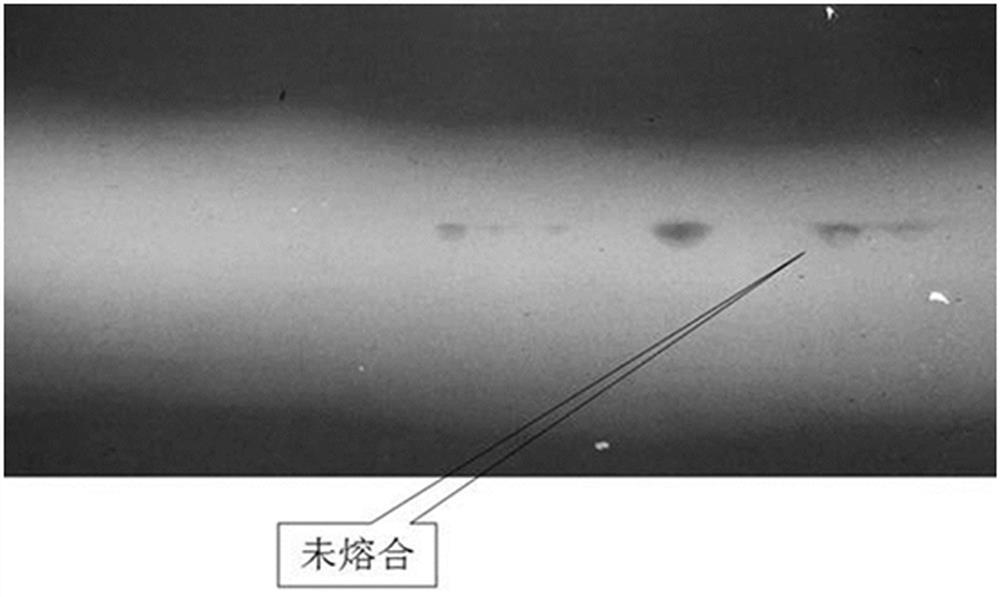

Blood vessel detection method, ultrasonic equipment, and computer-readable storage medium

PendingCN114078105ANo need for manual identificationImage enhancementImage analysisGreat Blood VesselVascular Stenosis

The invention discloses a blood vessel detection method, ultrasonic equipment, and a computer-readable storage medium. The blood vessel detection method comprises the following steps: determining a target blood vessel area of an ultrasonic image; obtaining a maximum blood vessel diameter and a minimum blood vessel diameter corresponding to the target blood vessel area; determining a blood vessel stenosis ratio of the target blood vessel area according to the maximum blood vessel diameter and the minimum blood vessel diameter. According to the blood vessel detection method provided by the invention, on one hand, blood vessel stenosis analysis can be automatically carried out on a target blood vessel area, manual identification of the blood vessel stenosis condition is not needed, and time and labor are saved; on the other hand, the blood vessel stenosis can be quantitatively analyzed, and the blood vessel stenosis condition can be more accurately judged.

Owner:EDAN INSTR

Non-destructive testing method for weld defects based on computer vision

ActiveCN113588692BNo need for manual identificationHigh degree of automationImage enhancementImage analysisEngineeringStructural engineering

The invention relates to a non-destructive detection method for weld defects based on computer vision, which includes the following contents: performing semantic segmentation on the X-ray film of the weld to obtain the edge of the weld, and performing connected domain analysis on the inner area of the edge of the weld to obtain the connectivity inside the weld domain; segment the edge of each connected domain to obtain the outer edge near the base metal side and the inner edge near the center of the weld; respectively obtain the recognition, blackness and straightness of the inner edge and outer edge; Use the recognition and blackness to obtain the definition of the inner edge and the outer edge; get the unfused rate of the connected domain according to the definition difference and flatness difference between the inner edge and the outer edge; set the threshold, and connect the threshold and the connection The unfused rate corresponding to the domain is compared, and the connected domain is marked according to the comparison result of the threshold value and the unfused rate corresponding to the connected domain. According to the technical means proposed by the present invention, the non-fusion defect of the weld can be accurately identified, and the identification of easily confused types of the weld defect is more accurate.

Owner:南通皋亚钢结构有限公司

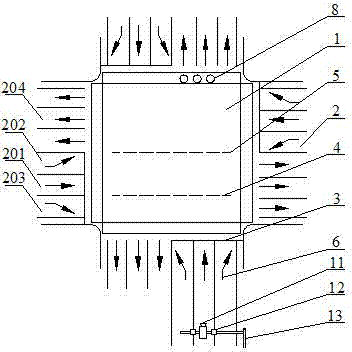

Hair blowing device for cloth

InactiveCN110835836ABlow evenlyHair dryer is easy to achieveMechanical cleaningPressure cleaningEngineeringWorkbench

The invention discloses a hair blowing device for cloth. The hair blowing device comprises a workbench, a vertical plate is arranged on each of left and right sides of the workbench, a sliding block which slides is arranged at the upper end of each vertical plate, an air blowing adjustment box is arranged between the two sliders, comprises an air distribution cavity positioned at an air inlet andan air feeding cavity positioned at an air outlet and blows air to the cloth on the workbench, and a lower guide groove is formed in the lower end of each sliding block and slides along the corresponding vertical plate. Moving of the air blowing adjustment box is realized through the sliding blocks sliding along the vertical plates, and whole-size air blowing of the cloth on the workbench is realized through the air blowing adjustment box; the air distribution cavity and the air feeding cavity are communicated through a connection air groove; through the opposite arc-shaped structure of an inverted ventilation cover and an upper cover plate, uniform air distribution is realized, and the problem that uniform air outgoing cannot be realized due to excessive transverse length is solved thoroughly. Air can be blown to the cloth conveniently, and manual thread end recognition is not needed.

Owner:天津汇来制衣有限公司

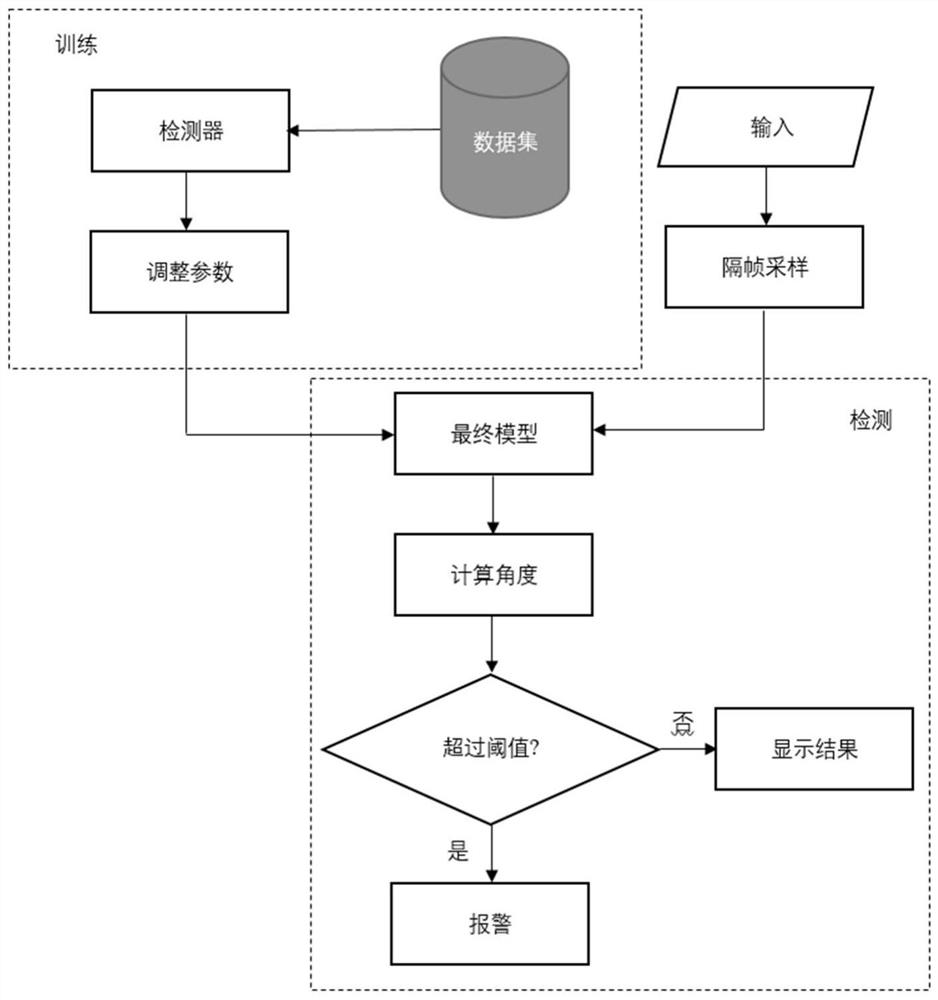

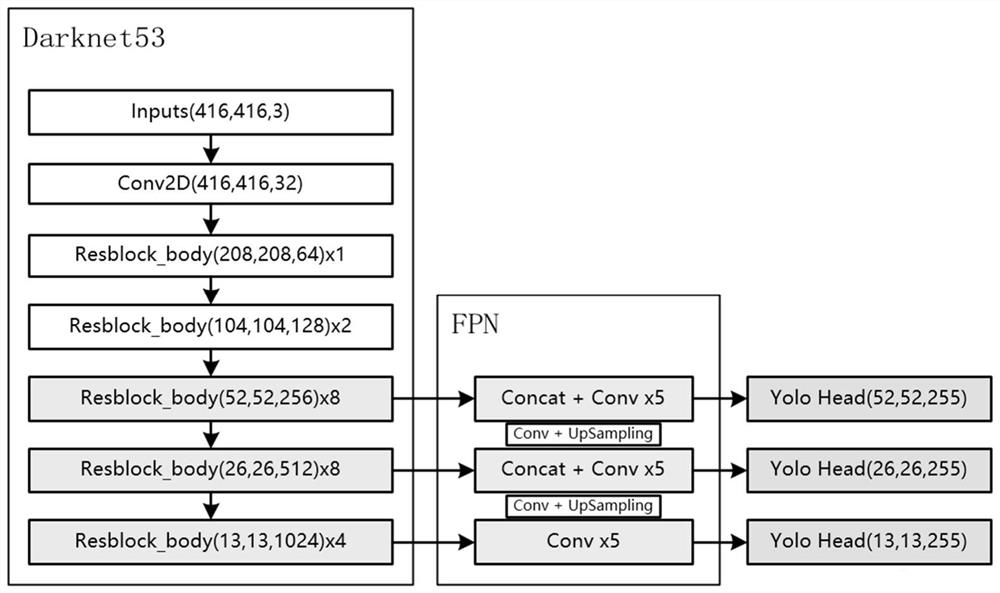

Method for detecting inclined pulling and inclined hoisting of portal crane based on YOLOV3 algorithm

PendingCN114429598ARobustComprehensive test resultsCharacter and pattern recognitionNeural architecturesData setAlgorithm

The invention discloses a method for detecting inclined pulling and inclined hoisting of a portal crane based on a YOLOV3 algorithm, and belongs to the field of image target detection. The method comprises the following steps: respectively constructing data sets of a portal crane lifting hook and a lifted object, marking samples of the data sets, constructing a deep learning network architecture based on a YOLOV3 algorithm, training the data sets based on a YOLOV3 network, performing parameter adjustment on the network architecture according to a training result, and putting a video frame to be detected into the network for detection and judgment after adjustment is completed. Finally identifying and determining the poses of the lifting hook and the lifting object, automatically calculating the inclined pulling and inclined lifting angle of the portal crane according to a defined inclination formula, and comparing the inclined pulling and inclined lifting angle with a threshold angle to decide whether to give an alarm or not. According to the method, the poses of the lifting hook and the lifting object of the portal crane can be quickly positioned from the monitoring video, priori information such as the position of the portal crane does not need to be obtained, meanwhile, the characteristics of the lifting hook and the lifting object are fully learned through a YOLOV3 network structure, and the influence of complex outdoor environment factors on inclined pulling and inclined lifting detection of the portal crane can be solved; and meanwhile, the requirements of real-time performance and accuracy can be met.

Owner:ZHEJIANG PROVINCIAL SPECIAL EQUIP INSPECTION & RES INST +1

Method and device for monitoring motor vehicle in case of regulation violation for running red light

InactiveCN103021182BEffective filteringReduce useless dataRoad vehicles traffic controlGreen-lightComputer science

The invention discloses a method for monitoring a motor vehicle in case of regulation violation for running the red light. The method includes the following steps: A. a red light signal time range is obtained, and detection of running against guiding arrows beyond the red light signal time range is conducted; B. running speed V of the vehicle in front of a stop line in the red light signal time range is detected, and if the running speed is larger than a preset value Vy, a first evidence picture of the vehicle is shot; C. whether the vehicle is pressed on the strop line is detected, and if the vehicle is pressed on the stop line, a second evidence picture is shot, a step D is conducted, otherwise, detection stops; and D. a regulation violation type of the vehicle is judged, and a third evidence picture is shot. The invention further discloses a device for monitoring the motor vehicle in case of the regulation violation for running the red light. The method and device has the advantages of being high in collecting accuracy, small in data redundancy, low in cost and capable of further determining a detailed regulation violation type and monitoring regulation violation behaviors of the vehicle running against the indicating signs during the green light.

Owner:CHENGDU LINHAI ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com