Chip extra-low in standby power consumption

A standby power consumption, chip technology, applied in the field of microelectronics, can solve the problems of low standby power consumption, large power consumption, power consumption, etc., and achieve the effect of low standby power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Below in conjunction with accompanying drawing, the present invention will be further described.

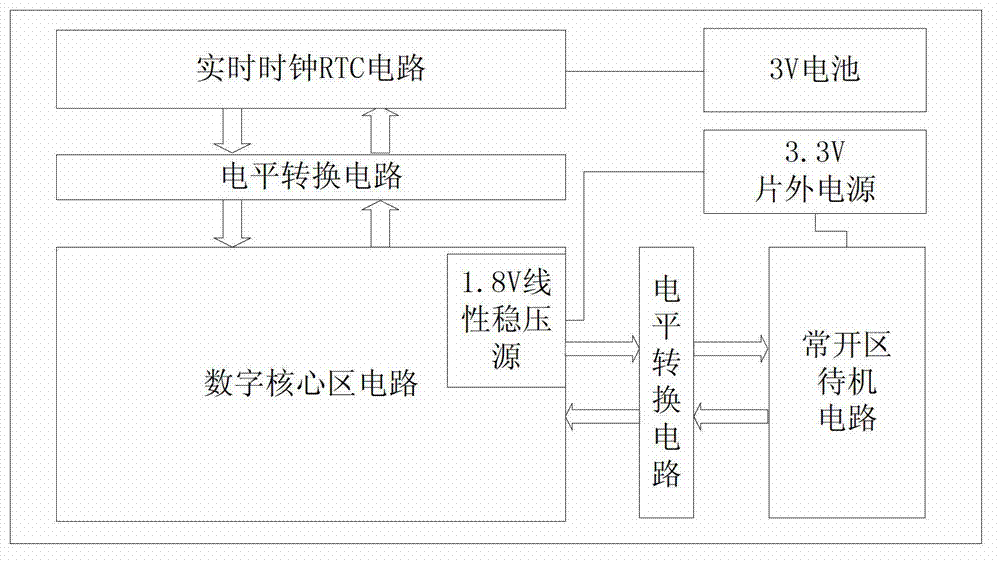

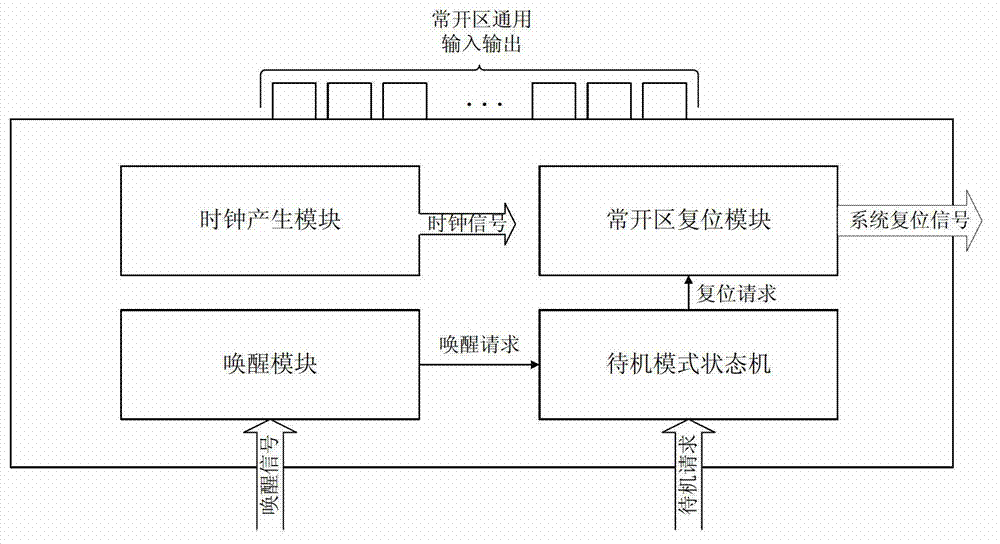

[0029] The core idea of the present invention is to divide the standby circuit in the normally open area from the digital core area, and supply power to this part of the circuit through an off-chip power supply. Since the power supply of the digital core area does not supply power in standby mode, the linear voltage regulator can be turned off directly, and the digital core area does not consume any power consumption, thus obtaining extremely low standby power consumption. Applying the low power consumption architecture to an already designed chip, the obtained standby power consumption is less than 2.6uA, which can illustrate the advantages and remarkable effects of the invention.

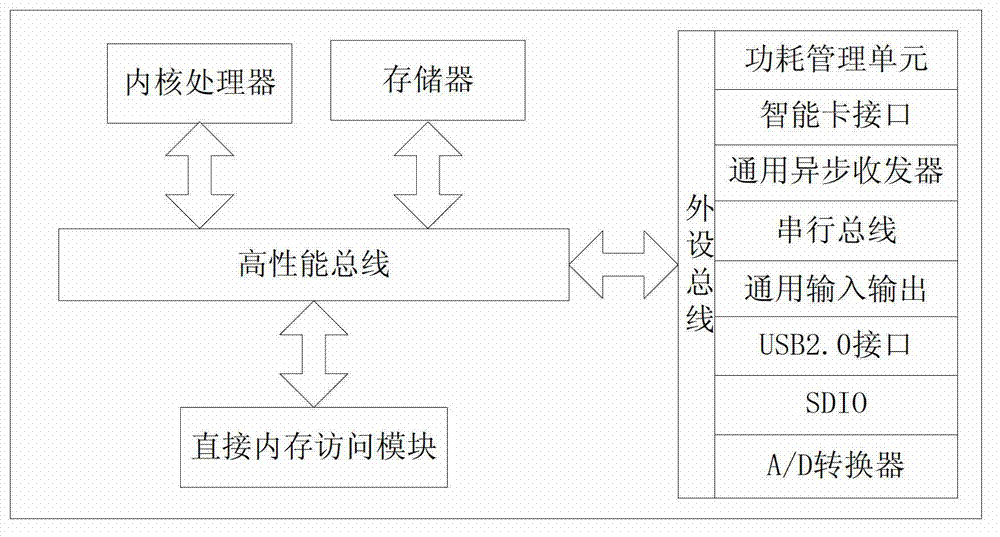

[0030] The chip with extremely low standby power consumption provided by the present invention includes a standby normally open circuit, a digital core circuit, a real-time clock circuit, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com