Method and device for tracking fault

A fault tracking and fault technology, applied in the direction of instruments, electrical digital data processing, hardware monitoring, etc., can solve problems such as failure to obtain fault information, and achieve the effect of complete detection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

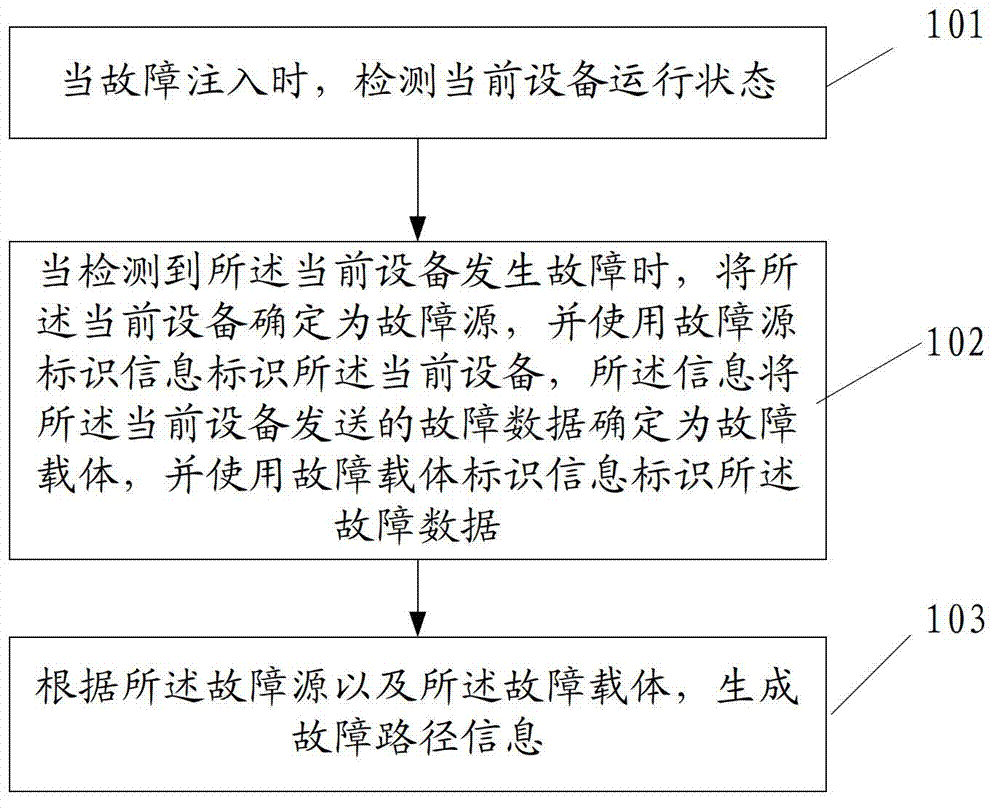

[0028] The embodiment of the present invention provides a method for fault tracking, such as figure 1 As shown, the method includes:

[0029] 101. When a fault is injected, detect the current running state of the device.

[0030] Wherein, the faults include processor faults, storage faults, routing faults, link faults and other types. Wherein, the processor type failure may include processor unit failure, processor execution unit failure, processor register failure, etc.; the storage type failure may include memory unit failure, memory address generation error, etc.; the routing type failure may Including routing errors, routing failures, routing duplication, etc.; the link failures may include link interruption between routers, link interruption between routers and processing units, link congestion, data loss, and the like. For example, routing error fault can add a random number to the correct routing forwarding port in the routing module or set the wrong routing forwardin...

Embodiment 2

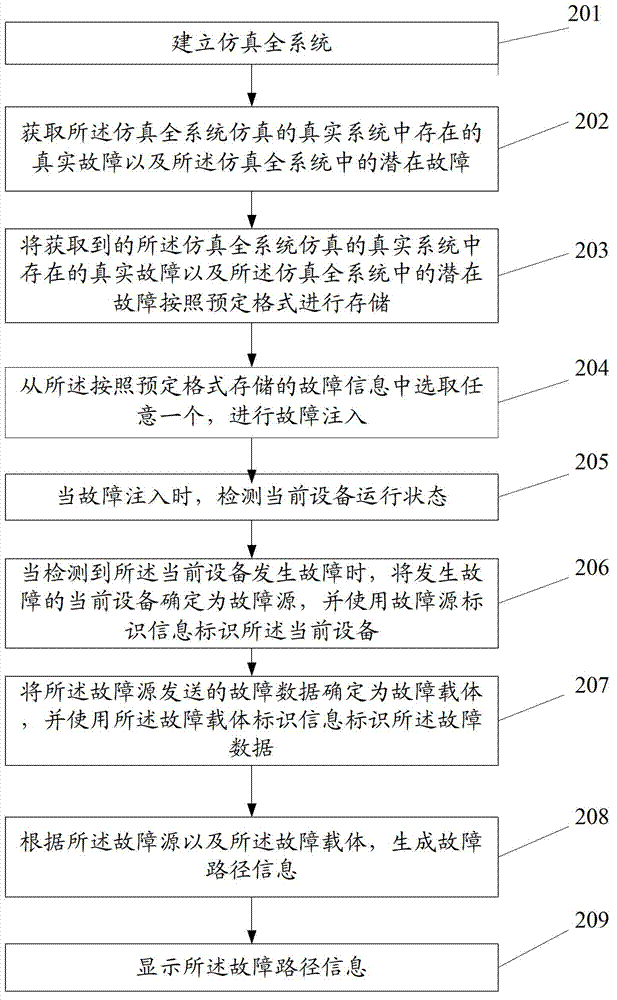

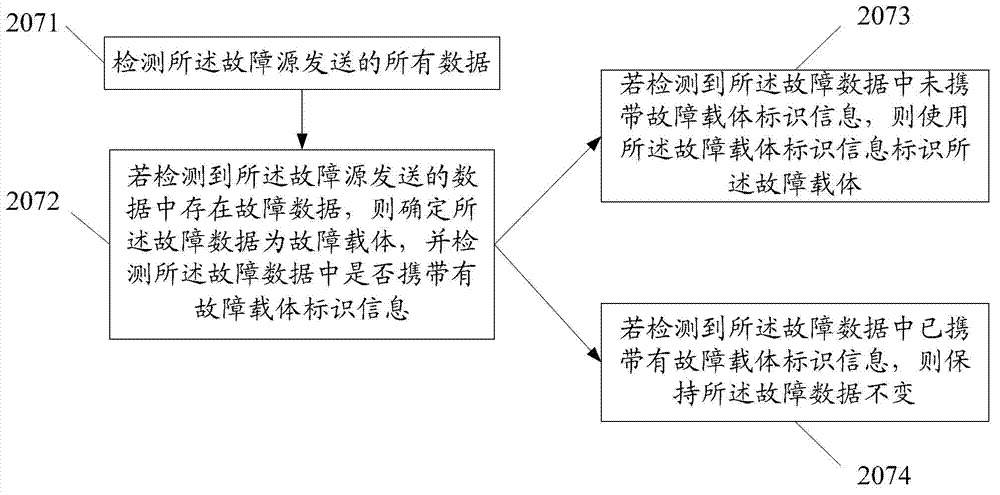

[0044] The embodiment of the present invention provides a method for fault tracking, such as figure 2 As shown, the method includes:

[0045] 201. Establish a simulation system.

[0046] Wherein, the whole system of simulation is used to simulate the real system.

[0047] It is worth noting that to build a simulated whole system, you can use existing open source simulators, or existing commercial simulators, or you can develop your own full system simulator or some modules of the simulator for the target system.

[0048] The constructed simulator can simulate and realize the main structural characteristics and functions of the target system, and follow the following three requirements:

[0049] The first requirement: the simulation accuracy is cycle-accurate, that is, the simulation can be accurate to each cycle, that is, the processing done in a cycle and the time it takes are known.

[0050] The second requirement: a full system emulation capability that can run real ope...

Embodiment 3

[0115] The embodiment of the present invention provides a device for fault tracking, such as Figure 5 As shown, the device includes: a first detection unit 41 , an identification unit 42 , and a generation unit 43 .

[0116] The first detection unit 41 is configured to detect the current operating state of the equipment when a fault is injected.

[0117] An identification unit 42, configured to determine the current device as a source of failure when the first detection unit 41 detects that the current device is faulty, and use fault source identification information to identify the current device, and identify the current device as the source of the fault. The faulty data sent by the device is determined as a faulty carrier, and the faulty data is identified by using the faulty carrier identification information.

[0118] The generation unit 43 is configured to generate fault path information according to the fault source and the fault carrier determined by the identificati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More