System for realizing digital-analog hybrid checking of filter

A digital-analog hybrid and filter technology, applied in the electronic field, can solve problems such as inability to converge, complex system-level verification, and long time, and achieve the effects of ensuring completeness, improving verification efficiency, and accelerating convergence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] specific implementation plan

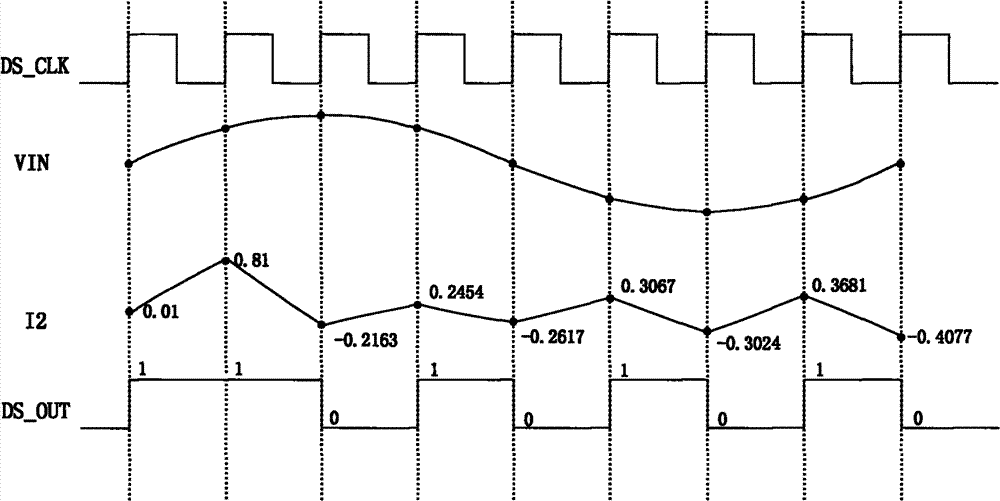

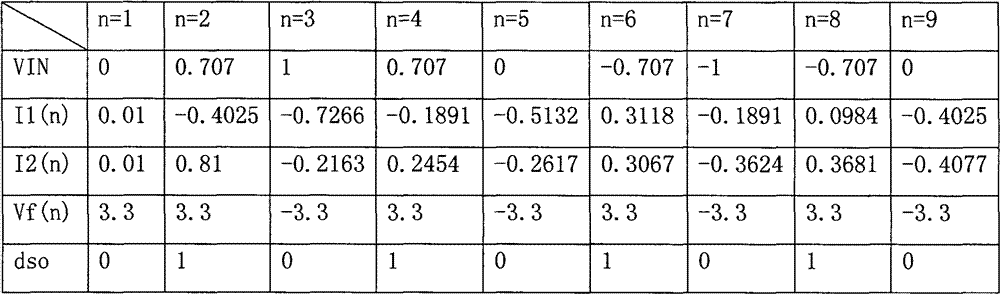

[0020] The core of the present invention is to use the real data (floating point data) of the verification language System Verilog to replace the analog signal, construct the analog component model, and realize the system level mixed signal verification of the Delat-Sigma filter. Compared with complete digital signal simulation, the invention has higher accuracy and faster system-level simulation speed. At the same time, verification methods such as System Verilog constrained random excitation, coverage statistics and assertion description can be applied.

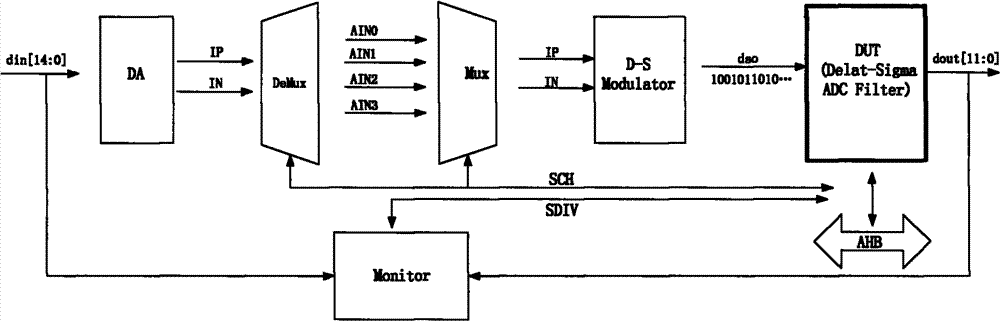

[0021] The specific realization of the method of the present invention is as follows figure 1 As shown, specifically:

[0022] By verifying the floating-point data of the language System Verilog instead of analog or electrical simulation quantities, construct analog components digital-to-analog conversion module DA, channel selection module DeMux, de-channel signal selection module Mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More