Nonvolatile memory IP core test and verify exploitation system

A non-volatile, development system technology, applied in static memory, instruments, etc., can solve problems such as inconsistent functions, inconsistent FLASH chip interfaces, and inability to provide NVMIP cores, etc., to speed up development, save time and cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

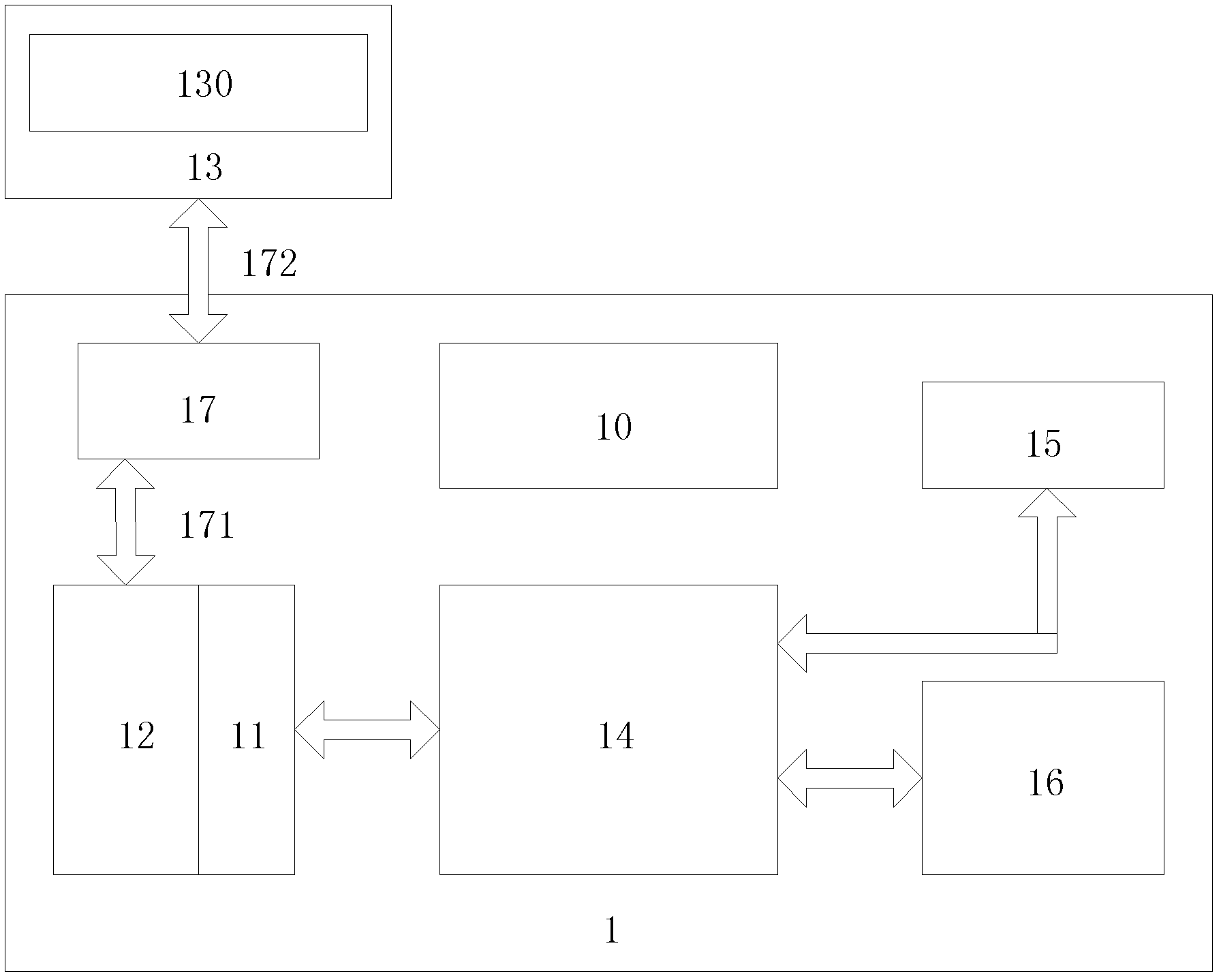

[0033] An embodiment of the test and verification development system of the NVM IP core of the present invention is as figure 1 shown, including:

[0034] Power supply module 10, provides power supply for each module in this system;

[0035] NVM IP core 11 is the object to be tested, developed and verified;

[0036] BIST circuit 12, is connected with described NVM IP core 11, is used for testing described NVM IP core 11;

[0037] Host computer 13, wherein has test software 130, and this software 130 controls BIST circuit 12 to carry out various test operations to NVM IP core 11;

[0038] FPGA chip 14, is connected with described NVM IP core 11, is used for developing described NVM IP core 11;

[0039] The FPGA configuration circuit 15 is connected with the FPGA chip 14, and the digital circuit logic for carrying out various developments and designs to the NVM IP core 11 can be downloaded in the FPGA configuration circuit 15 by compiling, synthesizing, laying out and wiring,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More