a memory architecture

A memory and memory bar technology, applied in the protection of internal/peripheral computer components, generation of response errors, error detection of redundant codes, etc., can solve the problem of write loss, slow read and write speed of phase change memory and STT-RAM and other issues to achieve the effect of low write loss, fast read and write speed, and strong data security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

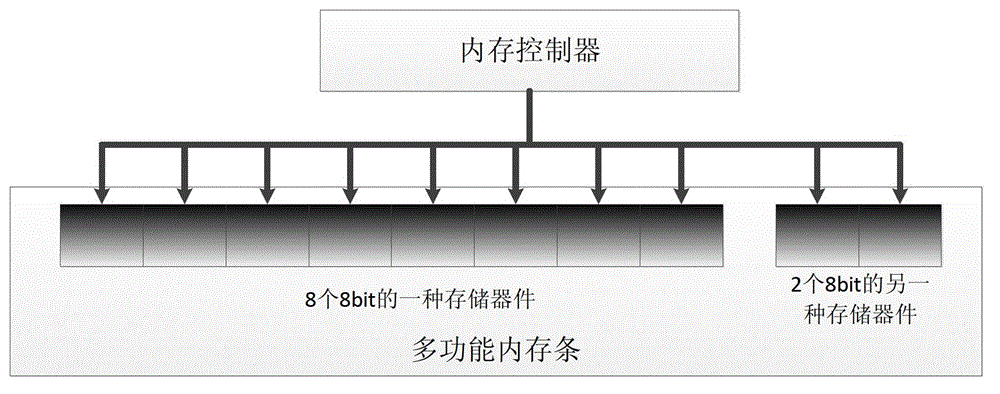

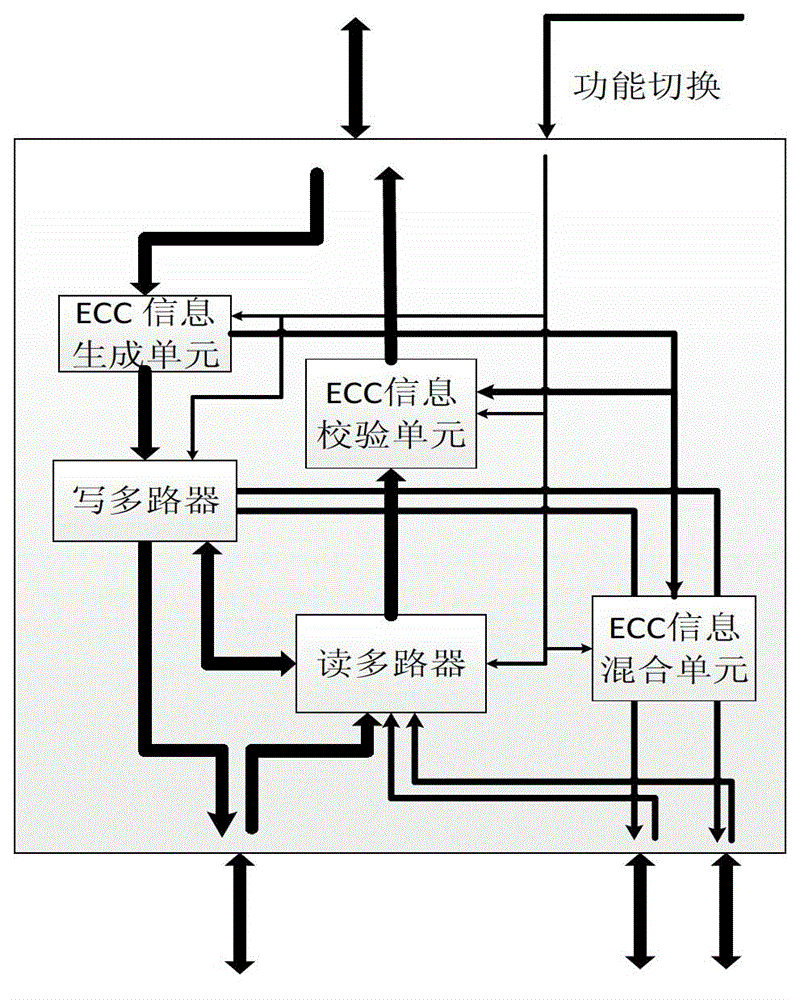

[0025] A memory architecture according to an embodiment of the present invention, the multifunctional memory architecture is composed of a memory stick and a memory controller, the memory stick is composed of storage devices, and the memory controller supports multiple storage devices and multiple functions.

[0026] The storage devices are heterogeneous or homogeneous storage devices, and the structures of the storage devices are non-hierarchical or hierarchical. The memory device includes a nonvolatile memory device chip and a volatile memory device chip.

[0027] The number of memory chips of the storage device is greater than the number of memory chips of the non-ECC ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com