Flat multichip packaging piece with stamping frame with square groove and production method of flat multichip packaging piece

A technology of multi-chip packaging and square grooves, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as performance degradation, product defects, failures, etc., to reduce the possibility of delamination, Improve product reliability and solve the effect of high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

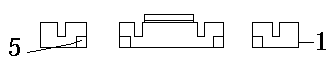

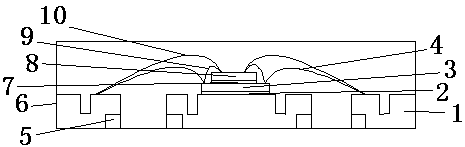

[0015] As shown in the figure, a flat multi-chip package with a stamping frame with a square groove is mainly composed of a lead frame 1, a square groove 5, a lower chip 3, an upper chip 8, a lower adhesive 2, an upper adhesive Glue 7, lower bonding wire 4, middle bonding wire 9, upper bonding wire 10, and plastic package 6; the lead frame 1 has a square groove 5, and the lead frame 1 is connected with the lower adhesive sheet glue 2 The lower chip 3 is bonded, the lower chip 3 is bonded to the upper chip 8 through the upper chip glue 7, the lower bonding wire 4 is connected to the lead frame 1 and the lower chip 3, and the middle bonding wire 9 is connected to the lower bonding wire 9. Sheet adhesive 2 and upper adhesive sheet adhesive 7, the upper bonding wire 10 connects the upper adhesive sheet adhesive 7 and the lead frame 1, and the plastic package 6 surrounds the lead frame 1, the lower chip 3, the upper chip 8, and the lower adhesive sheet adhesive 2. Upper adhesive 7,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More