Satellite navigation receiver FPGA (Field Programmable Gate Array) rapid loading method

A satellite navigation and receiver technology, applied in program loading/starting, satellite radio beacon positioning system, measuring device, etc., can solve the difficulty of connecting the JTAG port of the FPGA chip to the external connector, affecting the normal operation of the receiver, and slow speed, etc. Problems, to achieve the effect of easy external program upgrade, not easy to electromagnetic interference, and cost reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

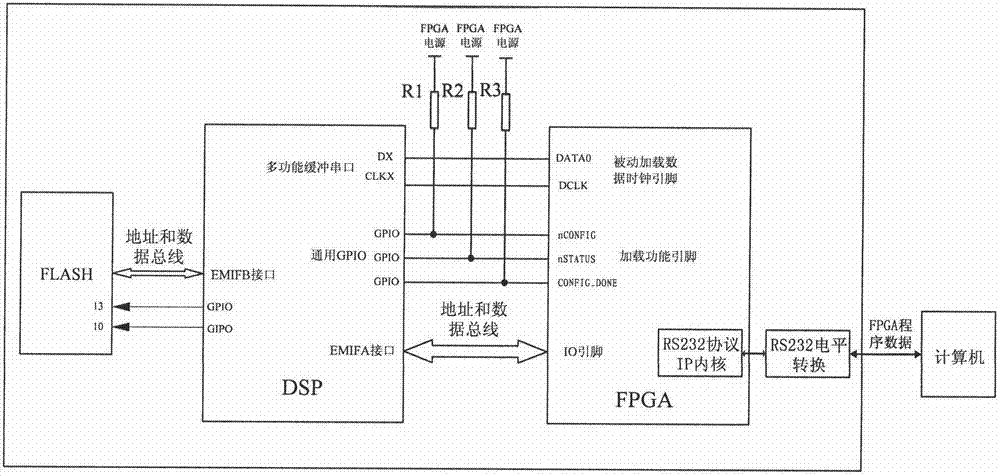

[0042] Such as figure 1 Shown is the hardware connection block diagram of FPGA fast loading system of the present invention, the FPGA fast loading system that satellite navigation receiver FPGA fast loading method of the present invention adopts comprises DSP chip, FLASH chip, RS232 level conversion chip, the first fixed resistor R1, The second fixed resistor R2, the third fixed resistor R3 and the FPGA chip. The DSP chip can be TMS32C64 series, TMS32C621 series or TMS32C671 series processors.

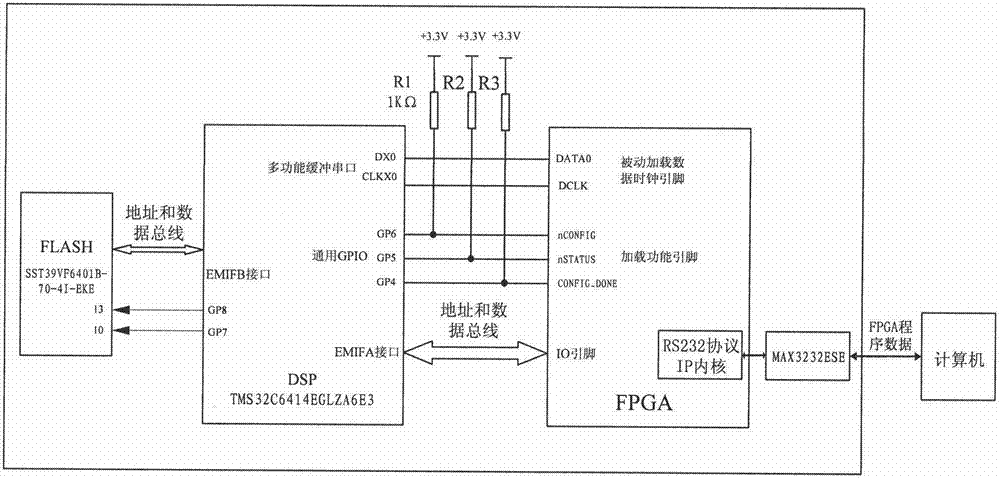

[0043] Such as figure 2 Shown is FPGA fast loading system hardware connection block diagram in the embodiment of the present invention, in the present embodiment, DSP chip (model TMS32C6414EGLZA6E3), FLASH chip (model SST39VF6401B-70-4I-EKE), RS232 level conversion chip (model MAX3232ESE), The first fixed resistor R1 (resistance value is 1KΩ), the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More