Method and system for debugging double data rate synchronous dynamic random access memory (DDR SDRAM)

A debugging method and a technology for debugging a system, which are applied in the detection of faulty computer hardware, function inspection, etc., can solve problems such as crashes, errors, and data loss, and achieve the effect of avoiding errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

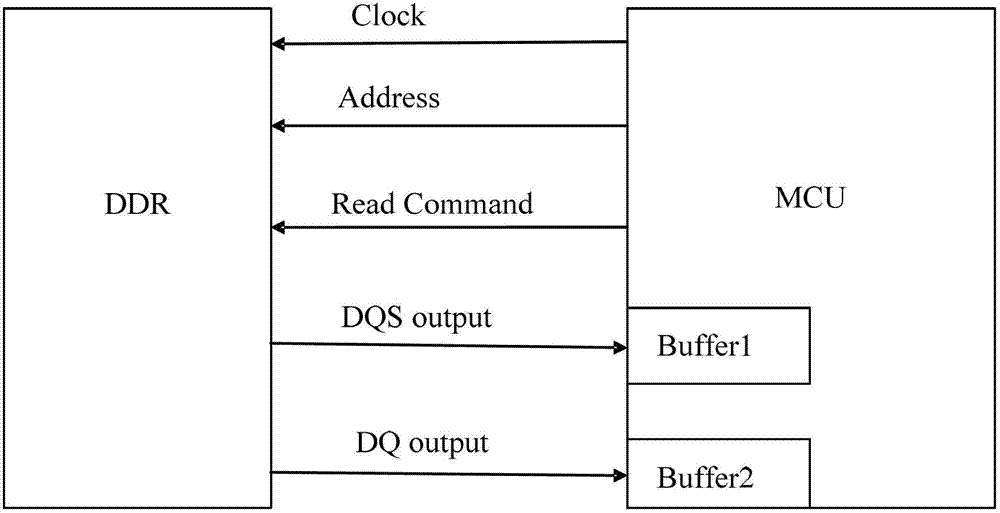

[0024] Such as figure 1 and figure 2 As shown, MCU (Micro Control Unit, micro control unit) includes Buffer 1 (buffer register 1) and Buffer 2 (buffer register 2), and MCU realizes DDR (Double Data Rate Synchronous Dynamic Random Access Memory, Double Data Rate Synchronous Dynamic Random Access Memory, double-rate synchronous dynamic random access memory) read and write operations. The MCU adjusts the phase of DQS (Data Strobe, data gate) by adjusting the value of Buffer 1, and the DQS is used to control data read and write operations. The MCU adjusts the phase of DQ (Data, data) by adjusting the value of Buffer 2.

[0025] Such as image 3 Shown is a functional block diagram of a preferred embodiment of the DDR debugging system of the present invention. The DDR debugging system 10 runs in the MCU, and the DDR d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com