Stacking-type semiconductor package structure

A packaging structure and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., to achieve the effects of increasing qualification, enhancing heat dissipation, and avoiding interference with other effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] The terms "first", "second" and "third" mentioned below are used to distinguish the referred elements, not to sort or limit the difference of the referred elements, and are not used to limit the scope of the invention. The term "circuit board" mentioned below at least includes a single-layer or multi-layer substrate and at least one conductive circuit. Conductive traces are formed on the outer surface of the substrate and / or the surface of the inner interlayer. Furthermore, the conductive lines can penetrate through one or more layers of the substrate to form electrical connections between different surfaces of the substrate.

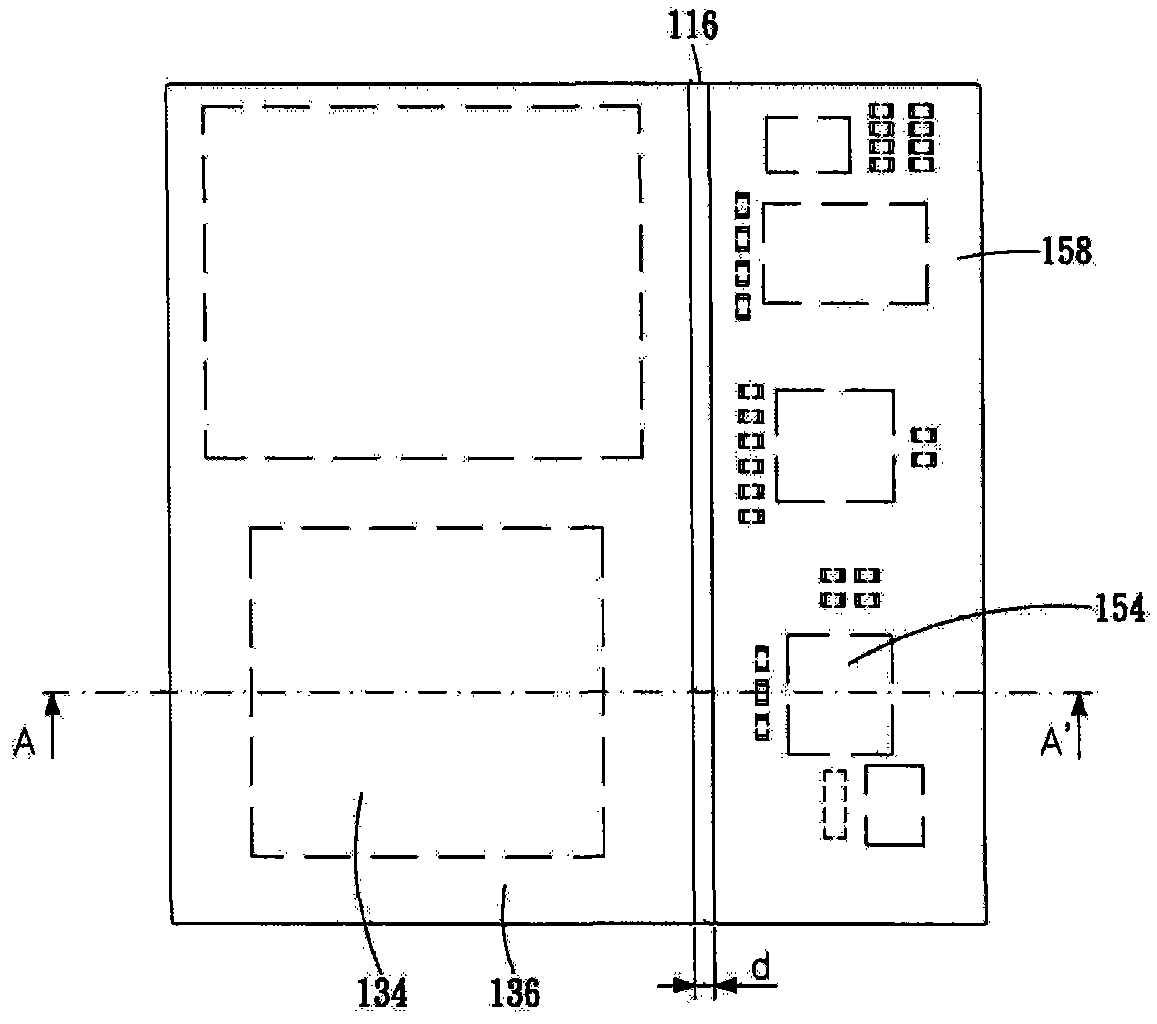

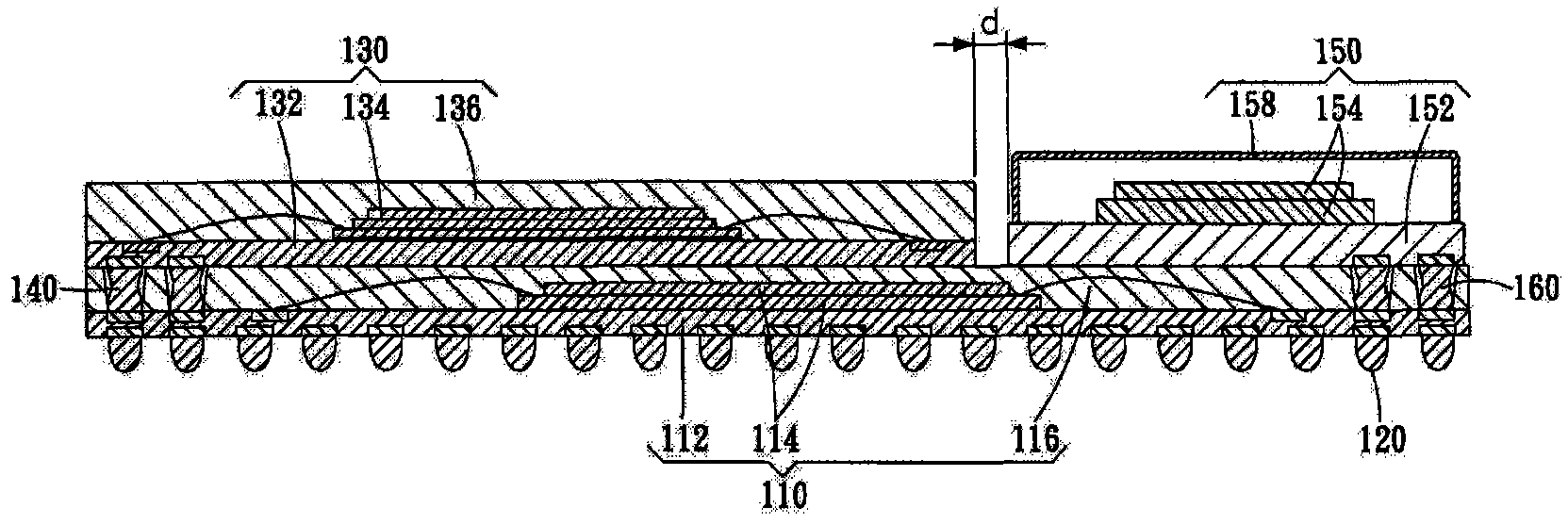

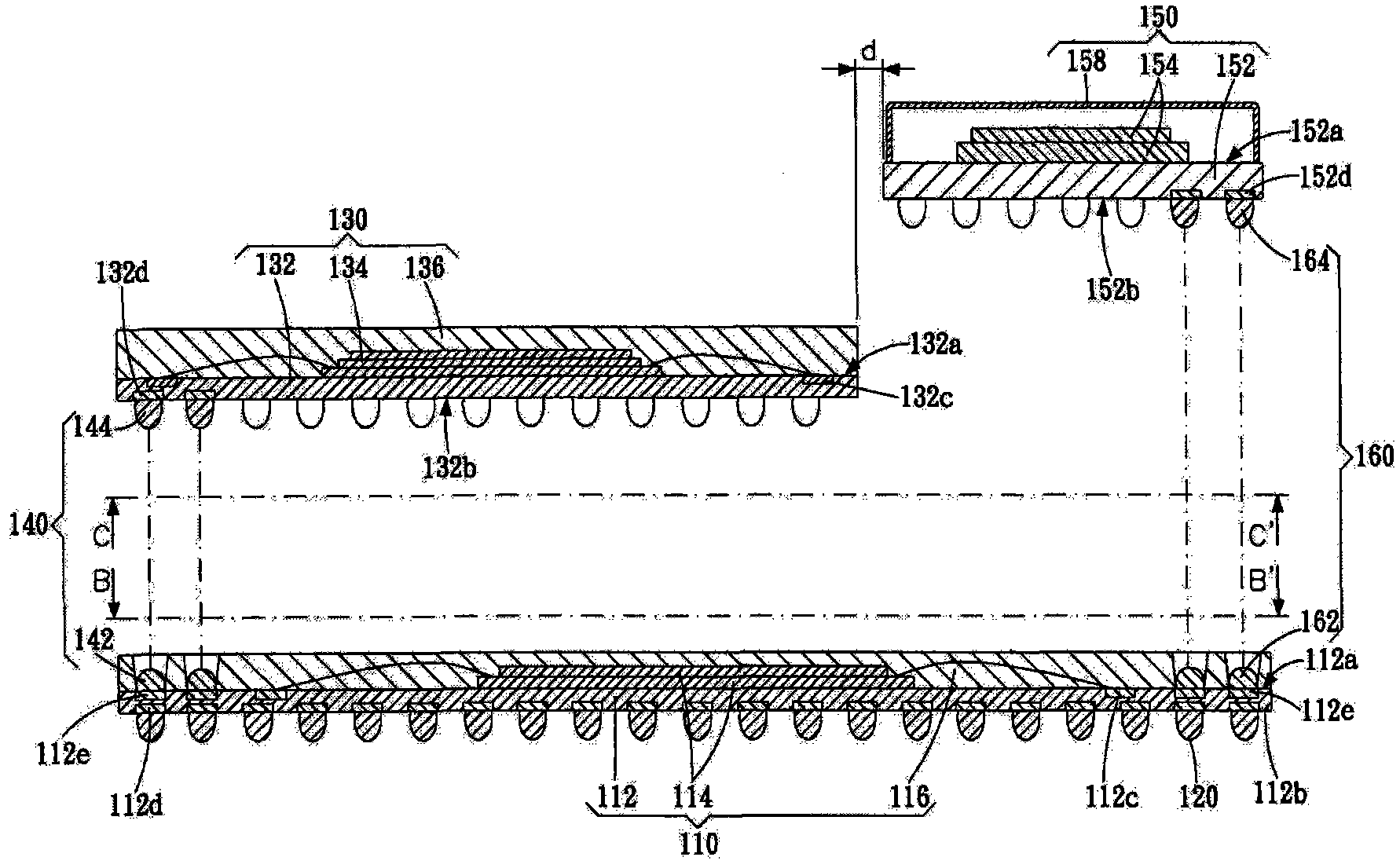

[0057] figure 1 It is a top view of a stacked semiconductor package structure according to an embodiment of the present invention, figure 2 yes figure 1 A schematic diagram of the cross-sectional structure of an embodiment along the tangent line A-A', and image 3 yes figure 2 An exploded view of an embodiment of the cross-sectional struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More