Grid structure of multi-layer film and manufacturing method of grid structure

A manufacturing method and gate structure technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of non-disclosure and achieve the effect of reducing the depression

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

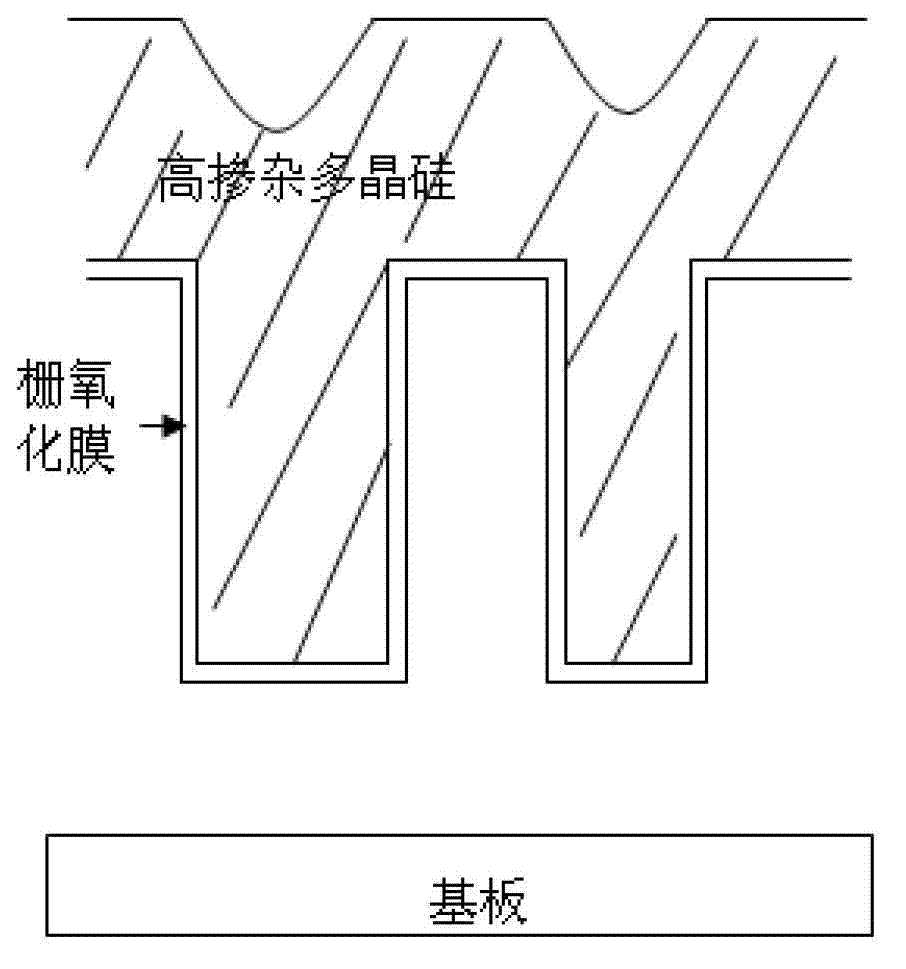

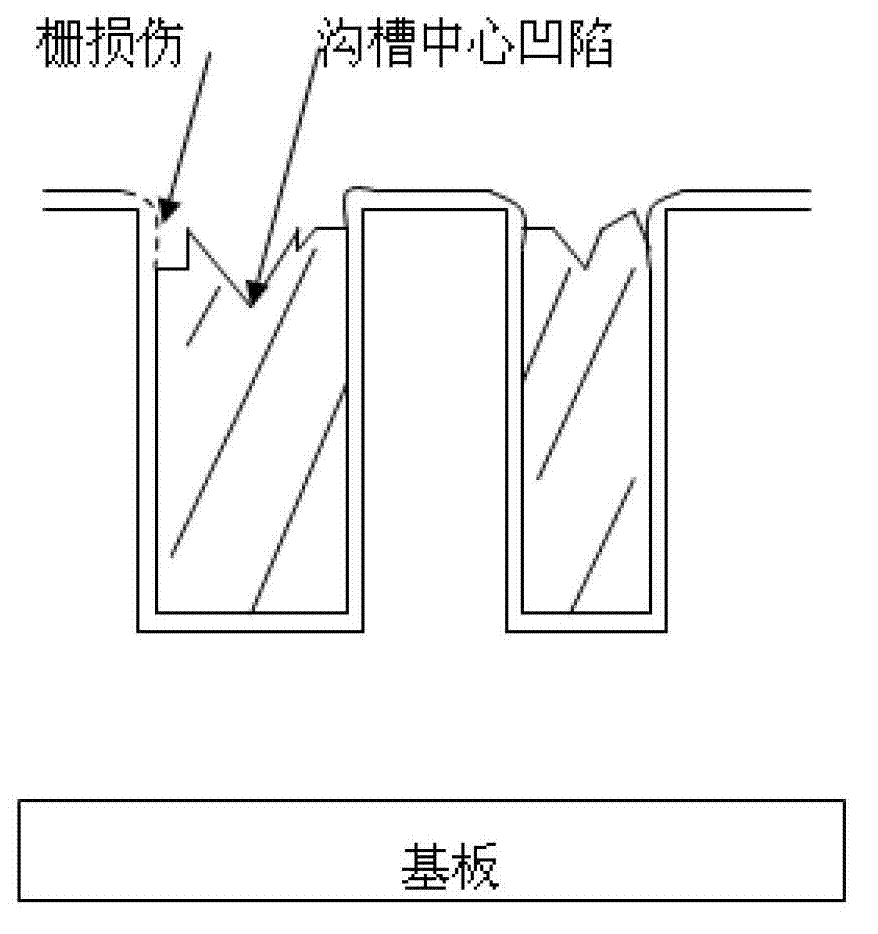

Problems solved by technology

Method used

Image

Examples

Embodiment 1

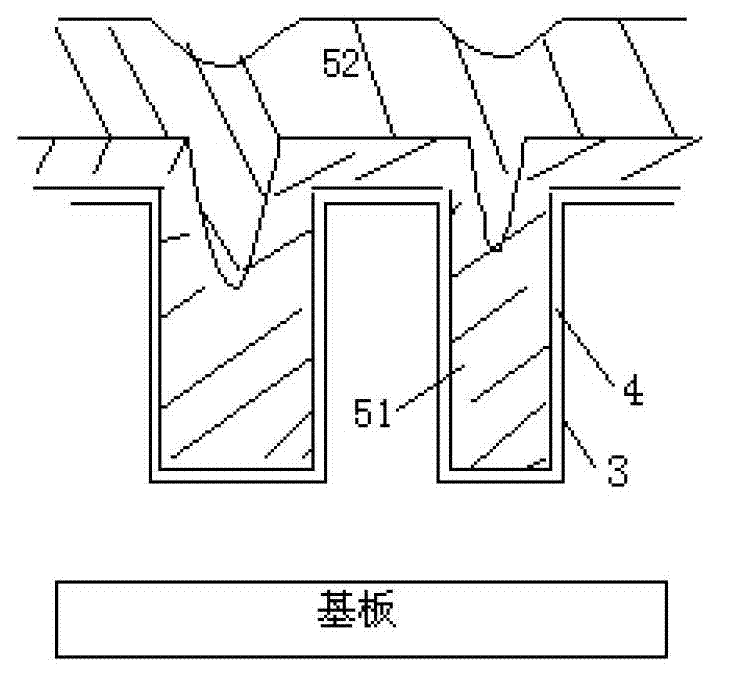

[0028] see image 3 , 4 As shown, the gate structure of the multilayer film includes: a gate oxide 4 formed in the trench 3; a first layer of polysilicon or amorphous silicon 51 with a high phosphorus doping concentration on the gate oxide 4, the first layer The phosphorus doping concentration of layer polysilicon or amorphous silicon 51 is 1E20-10E20atm / cm 3 , with a thickness of 3,000 angstroms to 10,000 angstroms; on the first layer of polysilicon or amorphous silicon 51, a second layer of polysilicon or amorphous silicon 52 with low phosphorous doping concentration, the second layer of polysilicon or amorphous silicon 52 The phosphorus doping concentration of the first layer of amorphous silicon or polysilicon 51 is less than or equal to 1 / 2 times of the phosphorus doping concentration of the first layer of amorphous silicon or polysilicon 51 .

[0029] The manufacturing method of the gate structure of the above-mentioned multilayer film, its processing step comprises: ...

Embodiment 2

[0035] see Figure 5 , the difference between this embodiment and Embodiment 1 is that after step 3 is completed, when the upper end surface of the second layer of polysilicon or amorphous silicon 52 is the lowest (see Figure 5 The dotted line at "C" in ) is higher than the gate oxide 4 on both ends of the trench 3 (see Figure 5 When the dotted line at "D" in the above), the third layer of polysilicon or amorphous silicon 53 with lower phosphorus doping concentration or no phosphorus doping is filled; then, dry etching is used to remove the polysilicon on the surface of the silicon wafer Or the amorphous silicon is completely etched away to obtain a gate structure filled with polysilicon or amorphous silicon in the trench (see Figure 6 ).

Embodiment 3

[0037] see Figure 7 , the difference between this embodiment and Embodiment 1 is that after step 2 is completed, when the upper end surface of the first layer of polysilicon or amorphous silicon 51 is the lowest (see Figure 7 The dotted line at "E" in ) is higher than the gate oxide 4 line on both ends of trench 3 (see Figure 7"F" in the dotted line), and then deposit the second layer of polysilicon or amorphous silicon 52.

[0038] In the above three embodiments, the polysilicon or amorphous silicon at the top position of the edge of the trench 3 may have a recess 61 after etching back, which will damage the gate oxide at the edge of the trench 3, so it can be etched back when necessary. After the completion, at least one gate oxide repair is performed, usually at a temperature higher than 1000°C. Diffusion process, rapid oxidation or annealing process can be used; the damage of gate oxide 4 exposed at the top of the edge of trench 3 can be repaired, thereby improving the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More