Serial Peripheral Interface (SPI) controller and communication method

A controller and control register technology, applied in the field of serial communication, can solve the problems of increasing the burden of software designers, increasing software overhead and CPU resource occupation, and achieving the effect of reducing software control and improving utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] The present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

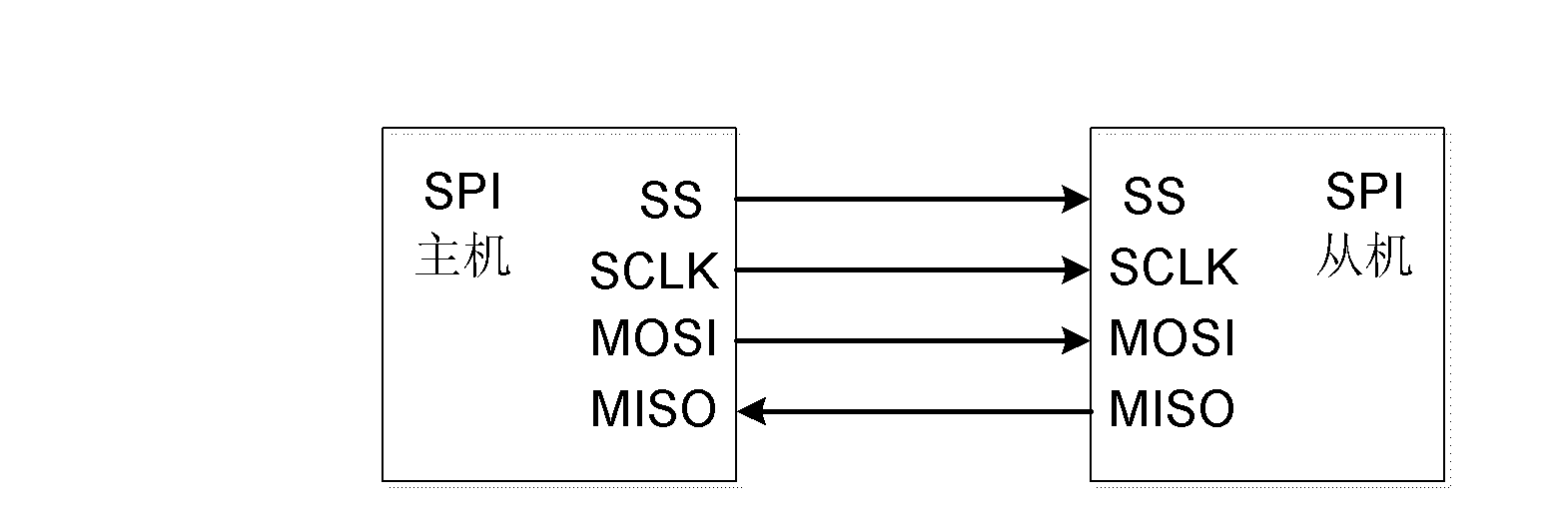

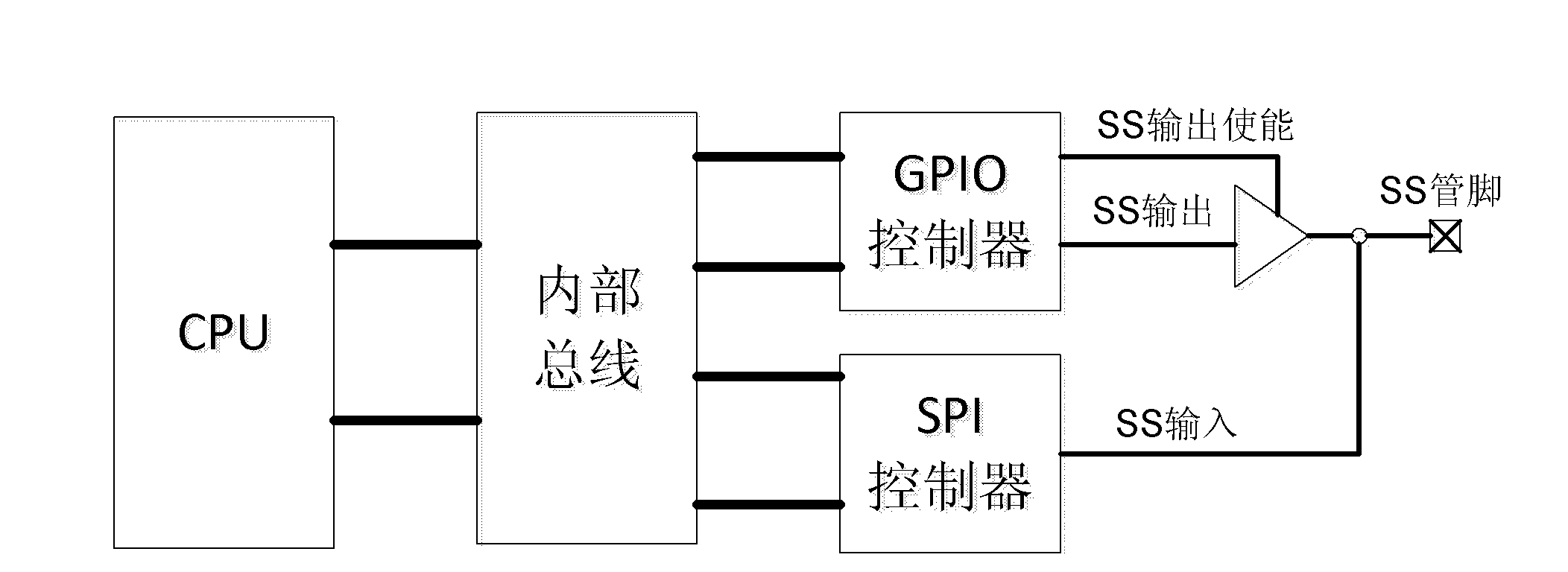

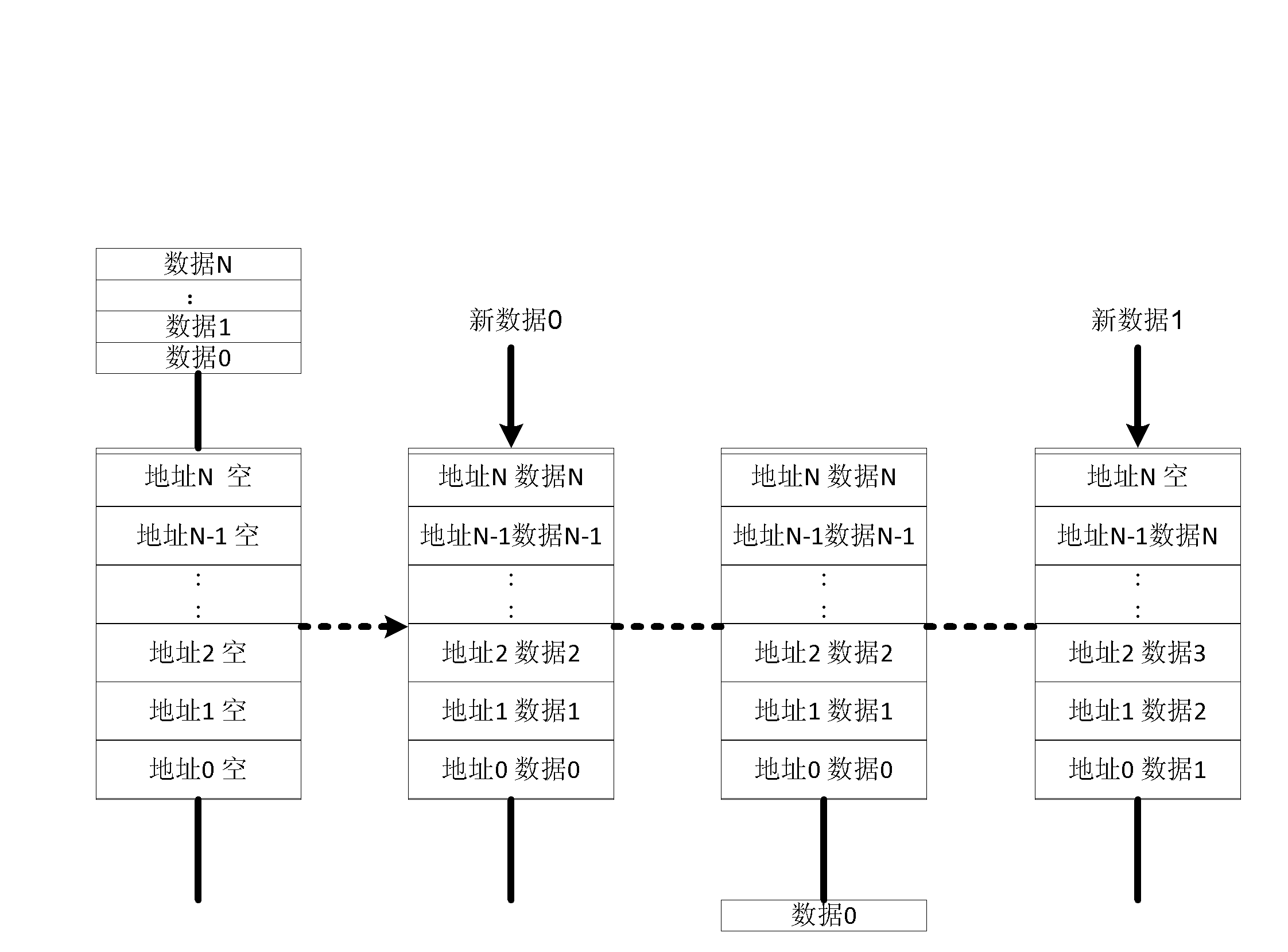

[0063] The present invention provides an SPI controller, such as Figure 4 As shown, it includes an internal bus interface module, which is used to realize the CPU operation of the SPI controller and the register module through the internal bus, and receives the configuration of the SPI controller from the CPU transmitted through the internal bus interface module, and a data conversion module for outputting data in parallel The conversion and input data serial-to-parallel conversion, state and interrupt control module is used to report the state of the SPI controller and generate interrupts, and it is characterized in that it also includes a finite state machine, which is used for according to the SPI transmission parameters registered by the control register in the register module and The SCLK baud rate parameter registered in the baud...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More