Automatic optimal integrated circuit generator from algorithms and specification

An integrated circuit, automatic generation technology, applied in CAD circuit design, instrument, calculation, etc., to achieve the effect of alleviating the problem of chip design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

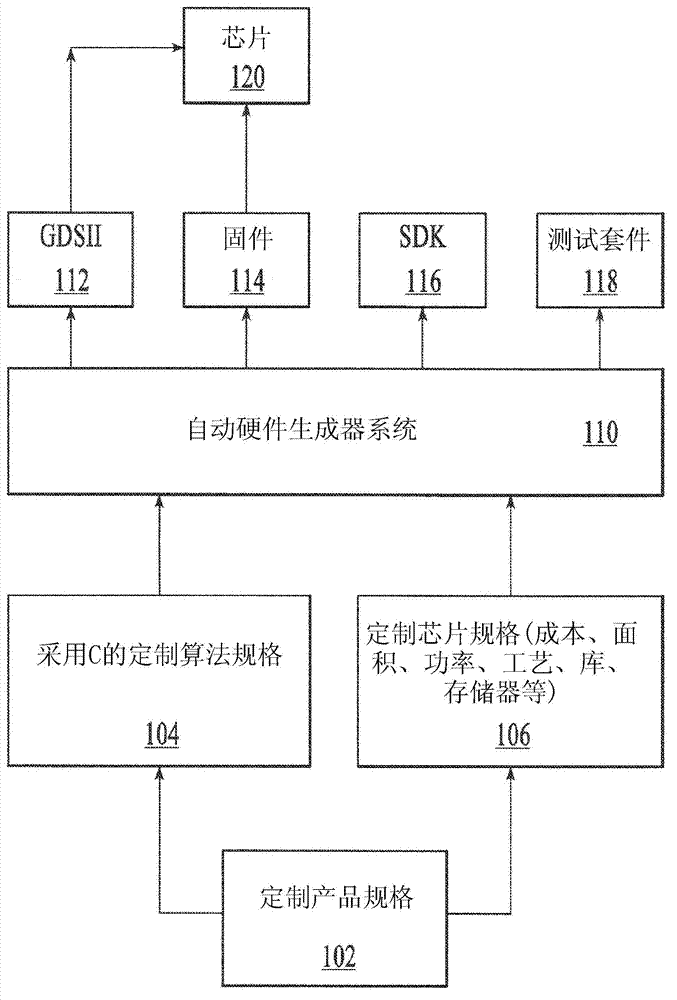

[0026] figure 1 An example system for automatically generating custom ICs is shown. figure 1 The system supports the automatic generation of the optimal custom integrated circuit solution for the selected target application. The specification of the target application is typically implemented by an algorithm expressed as computer readable code in a high-level language such as C, Matlab, SystemC, Fortran, Ada, or any other language. The specification includes a description of the target application and also includes one or more constraints such as desired cost, area, power, speed, performance, and other attributes of the hardware solution.

[0027] exist figure 1 , a custom IC generates a product specification 102 . Typically, there are initial product specifications that capture all major functions of the desired product. Based on the product, the algorithm expert identifies the computer readable code or algorithm required for the product. Some of these algorithms can be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More