Bias voltage generating circuit and memory of line decoder

A bias voltage, row decoder technology, applied in the field of memory, can solve the problem of large memory power loss, and achieve the effects of reducing power loss, reducing peak current, and small pull-down current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

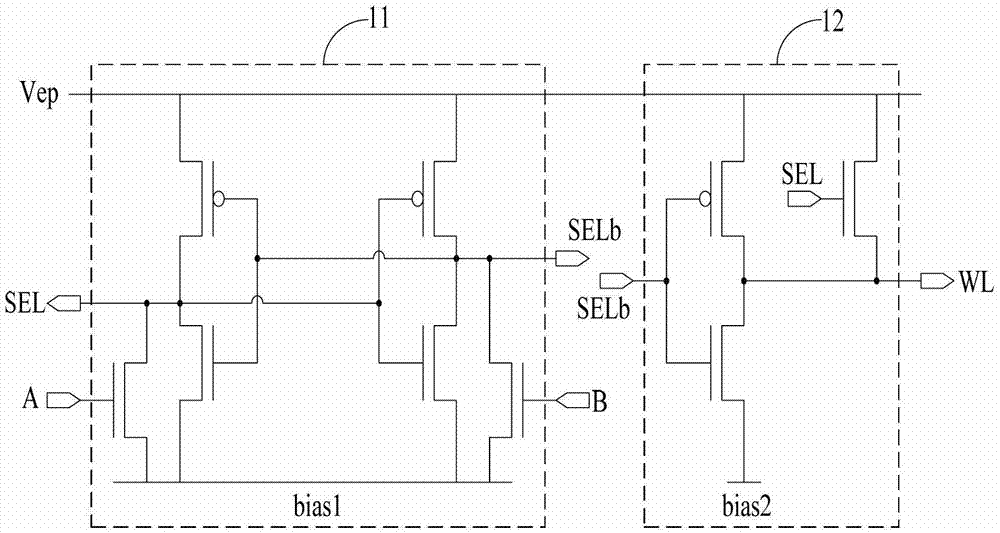

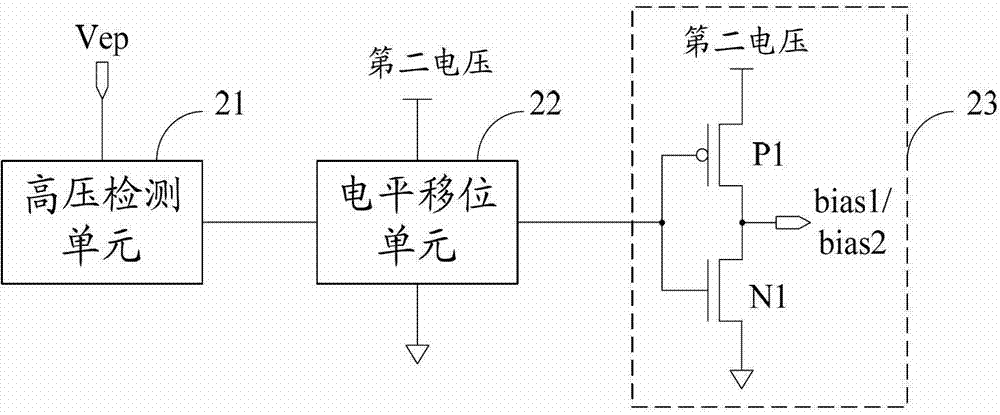

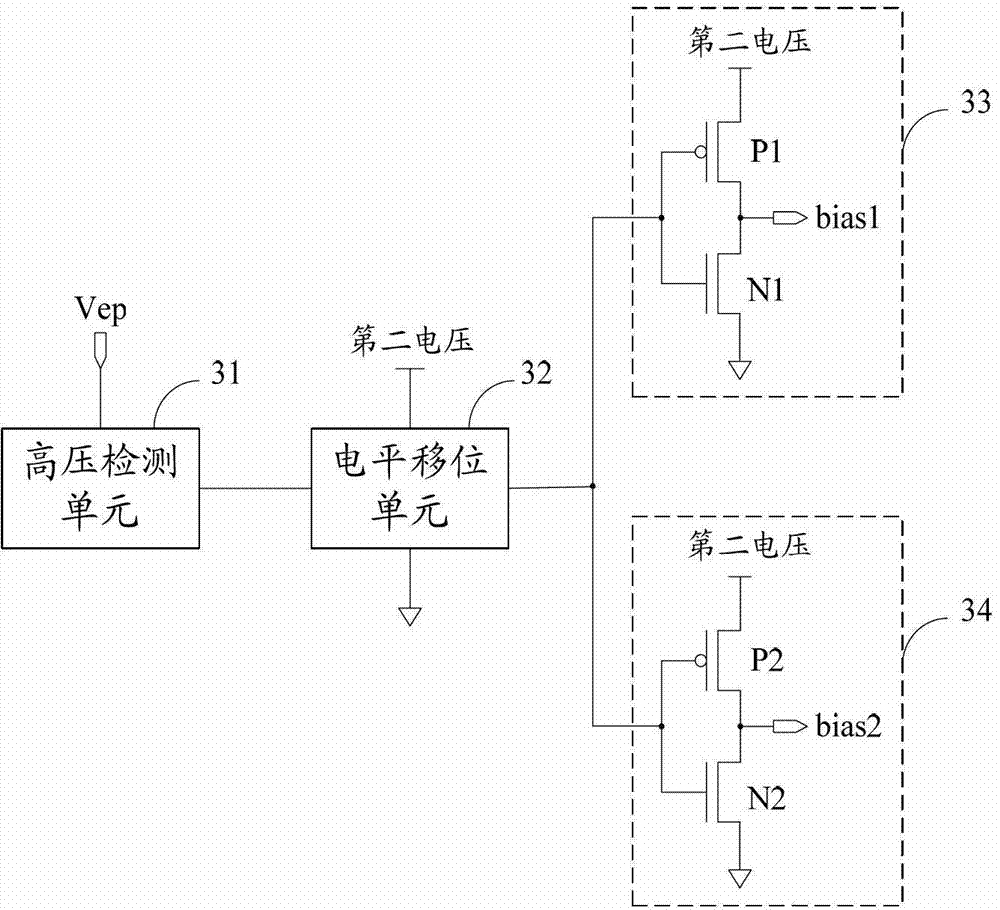

[0026] As described in the background technology, when the memory is performing an erase operation, figure 1 The first bias voltage bias1 and the second bias voltage bias2 required by the shown row decoder are provided by the same driving unit. After the erasing operation on the memory is completed, the first bias voltage bias1 and the second bias voltage bias2 will drop from the second voltage to the ground voltage. If the first bias voltage bias1 drops slowly, figure 1 The control signal generating unit 11 shown may output wrong third control signal SEL and fourth control signal SELb, causing logic confusion of memory erasing operation. therefore, figure 2The NMOS transistor N1 in the driving unit 23 shown must use a transistor with strong driving capability, so as to discharge quickly after the memory erasing operation, so that the first bias voltage bias1 drops rapidly. However, the rapid discharge results in a large peak current flowing into the ground, which increases...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More