Array substrate, manufacture method of array substrate and display device

A technology for array substrates and substrates, which is used in semiconductor/solid-state device manufacturing, electrical components, and electrical solid-state devices, etc., and can solve the problems of high production cost and low yield rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

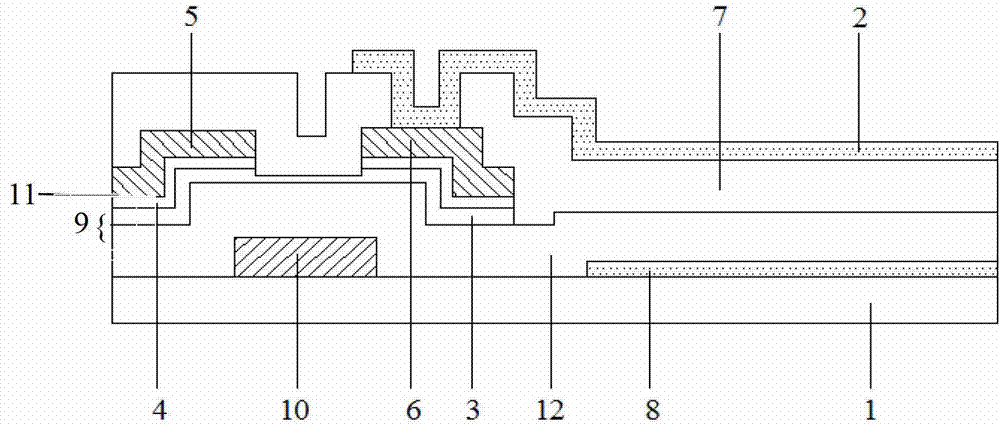

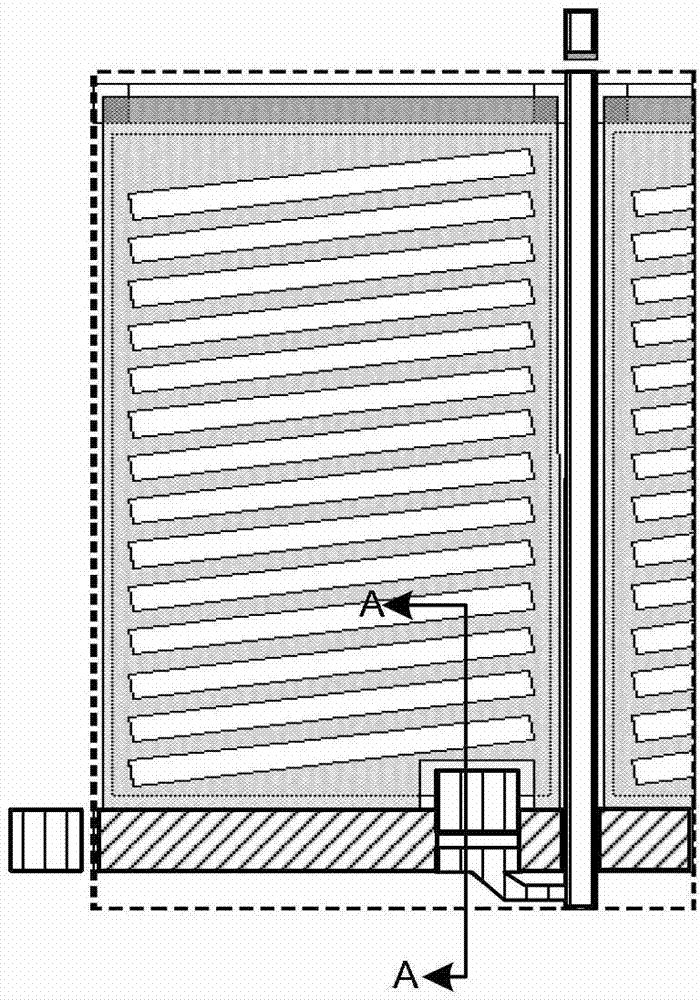

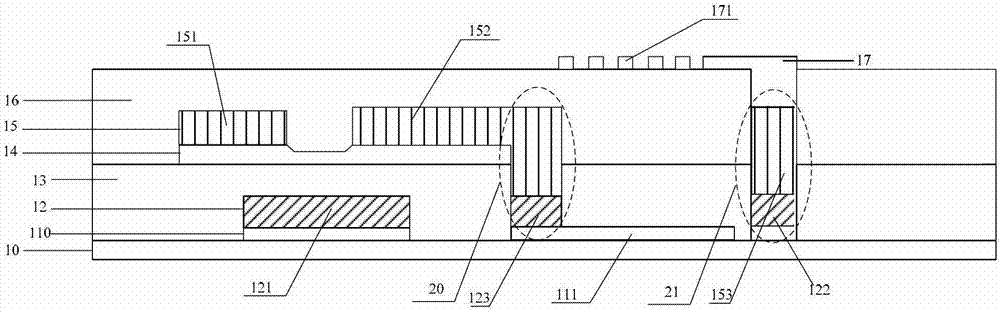

[0102] An embodiment of the present invention provides an array substrate. As shown in FIGS. , the source electrode 151, the drain electrode 152 and the insulating protection layer 16, the pixel electrode 111 and the common electrode 171 are also arranged on the substrate 10, and the first lead hole 20 connecting the pixel electrode 111 and the drain electrode 152 and connecting the common electrode 171 and the common The second lead hole 21 of the electrode line 122, wherein, the pixel electrode 111 is arranged on the substrate 10, the grid 121 is directly arranged on the transparent conductive layer arranged on the same layer as the pixel electrode 111; the pixel electrode 111 is arranged through the first lead hole The first metal connection layer 123 in 20 is connected to the drain electrode 152 , and the first metal connection layer 123 and the gate 121 are arranged on the same layer.

[0103] Preferably, the common electrode line 122 and the gate electrode 121 in this em...

Embodiment 2

[0124] An embodiment of the present invention also provides a display device, which includes any one of the array substrates described in Embodiment 1. The display device may be any product or component with a display function such as a liquid crystal panel, an electronic paper, an OLED panel, a mobile phone, a tablet computer, a television, a monitor, a notebook computer, a digital photo frame, a navigator, and the like.

[0125] In the display device provided by the embodiments of the present invention, the number of patterning processes used in the preparation process of the array substrate used is reduced, thereby effectively reducing the manufacturing cost and improving the yield rate.

Embodiment 3

[0127] The embodiment of the present invention also provides a method for manufacturing an array substrate, such as Figure 6 shown, including:

[0128] 101. Form a pixel electrode, a gate, a first metal connection layer, a common electrode line, a gate insulating layer, an active layer, a first lead hole 20 and a second lead hole 21 through the first patterning process;

[0129] As shown in Fig. 7(a) and (b), a transparent conductive film and a gate metal film are deposited on the substrate 10, and then a multi-level masking process is performed for sub-regional exposure and sub-regional etching to form the pixel electrode layer 11. Pattern (comprising pixel electrode 111) and the pattern of gate metal layer 12, the pattern of gate metal layer 12 comprises gate 121, gate line, the first metal connection layer 123 that is positioned at the first lead hole 20, and common electrode line 122 , the common electrode line partially extends to a position corresponding to the second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More