Design method of clock tree structure based on soc chip

A design method and tree structure technology, applied in the direction of generating/distributing signals, etc., can solve the problems of consuming circuit routing resources, etc., and achieve the effects of saving clock circuit resources, reducing area loss, and increasing the operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

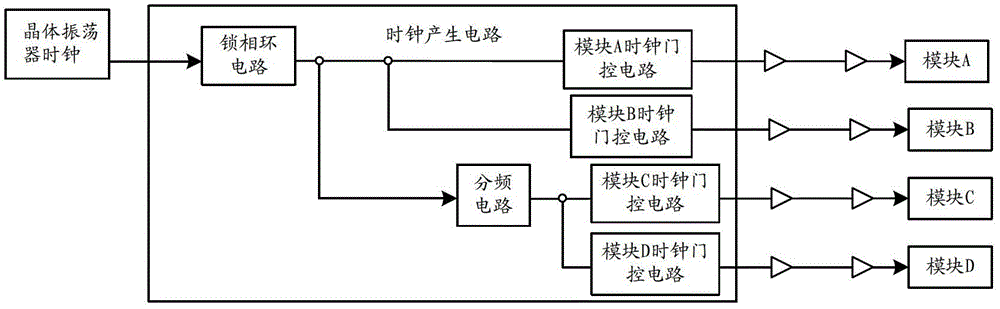

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

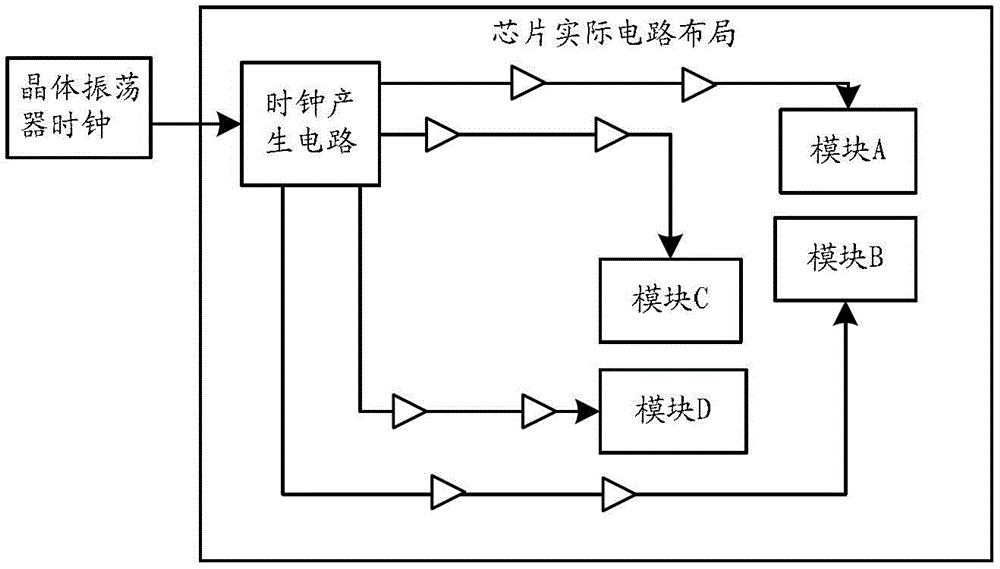

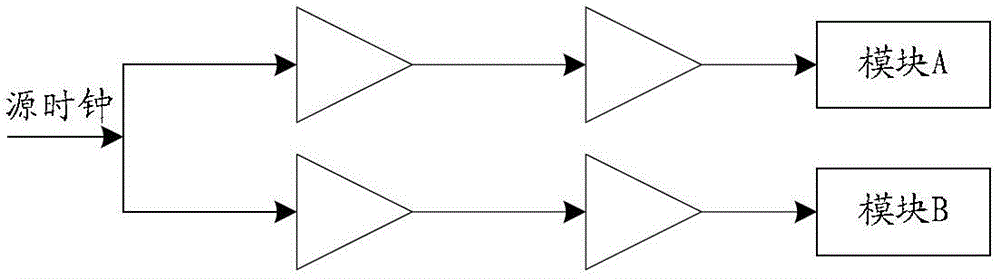

[0024] by image 3 and Figure 4 In contrast, the triangle in the figure is a buffer in the clock circuit, which is used to enhance the clock driving capability and control the clock delay, and the figure mainly indicates the delay length of the clock.

[0025] Module A and Module B use synchronous clocks. Assuming that the chip requires a performance of 500MHz, and each clock needs 2ns, if the source clock reaches the clock of module A and the clock of module B is exactly the same without any phase deviation, then each module has a margin of 2ns for functional timing. However, in the actual circuit, the two clocks need to be routed separately. Due to the reasons described above, the clock that finally reaches module A and the clock of module B cannot be completely consistent. When designing the module circuit, the clock routing difference needs to be deducted. For example, the module In the worst case, the clock of A and the clock of module B will differ by 0.5ns, so only a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More