Device for achieving multipath serial ADC synchronization by adopting FPGA

A single-channel, analog circuit technology, applied in the field of ADC synchronization devices, can solve the problems of reducing the ADC rate, simplicity, and tight pin allocation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0032] Below in conjunction with accompanying drawing, the present invention is described in detail.

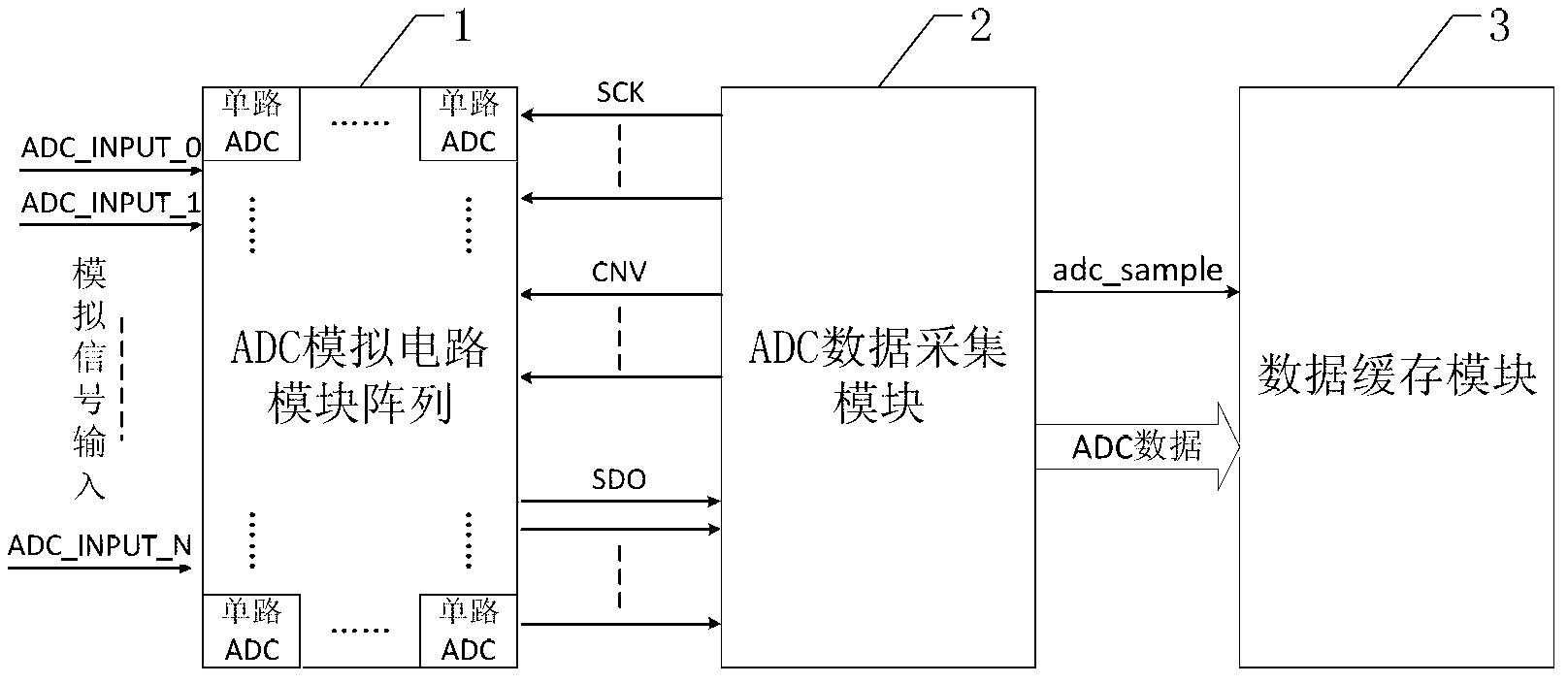

[0033] From image 3 We can see that this design is mainly composed of programmable logic modules (2 and 3 in the figure are programmed by programmable logic modules) and an array composed of AD analog-to-digital conversion modules (1 in the figure is an array composed of AD analog-to-digital conversion modules , the array is composed of multiple single-channel ADCs) composed of two parts, the interface between the FPGA as the control chip and the ADC array is completely digital signal, the inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More