NAND flash memory

A flash memory and storage unit technology, applied in the field of NAND flash memory, can solve the problems of high packaging and chip costs, complex operation, etc., and achieve the effect of improving data transmission speed, simple operation, and saving the number of I/O

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

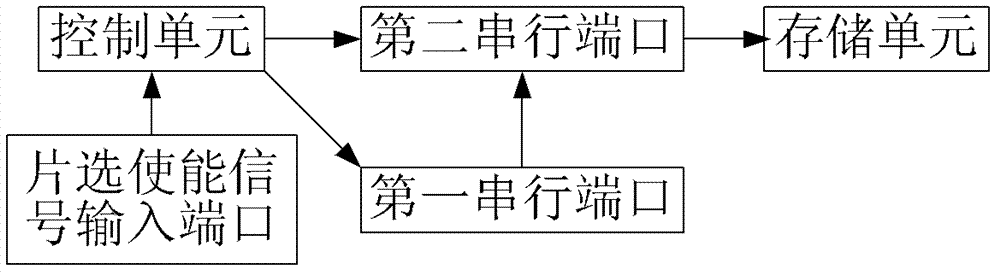

[0034] Embodiment one, a kind of NAND flash memory, such as figure 2 shown, including: storage unit;

[0035] a serial interface, including a first serial port and a second serial port;

[0036] The chip select enable signal input port is used to receive the chip select enable signal;

[0037] The control unit is used to indicate that the first serial port receives input data (including command signals, address signals, and sometimes empty bytes, etc.) when the chip select enable signal is low; after receiving the input data, Instructing the second serial port to output the data of the storage unit corresponding to the address.

[0038] In this embodiment, the NAND memory may further include a clock signal input port for receiving a clock signal for use by other devices in the NAND memory.

[0039] In this embodiment, the NAND memory may further include a buffer for saving the input data received by the first serial port for use when the second serial port outputs it.

[...

Embodiment 2

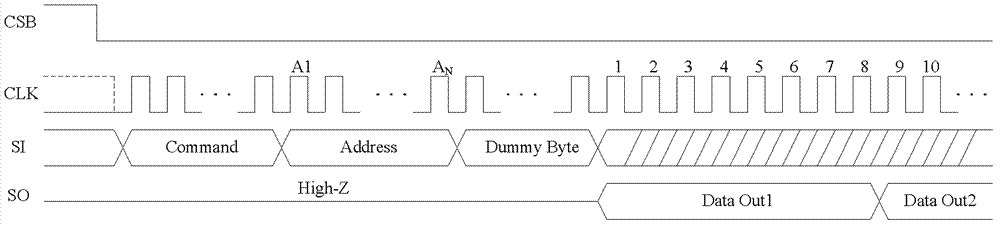

[0042] Embodiment 2, a NAND flash memory, has the same structure as Embodiment 1, and may also include the clock signal input port and buffer.

[0043] In this embodiment, the second serial port includes a first serial output port and a second serial output port, that is, a dual output (Dual Output) port is used.

[0044] In this embodiment, the control unit instructing the second serial port to output data corresponding to the address to the storage unit refers to:

[0045] The control unit instructs the first serial output port and the second serial output port to simultaneously output the data of the storage unit corresponding to the address.

[0046] Compared with the previous embodiment, this embodiment only needs half the clock time to transmit the same data, that is, the output data transmission speed is doubled.

[0047] Figure 4It is a timing diagram of this embodiment, and SO1 and SO2 are the data output to the storage unit by the first and second serial output po...

Embodiment 3

[0048] Embodiment 3, a NAND flash memory, has the same structure as Embodiment 1, and may also include the clock signal input port and buffer.

[0049] In this embodiment, the second serial port includes a first serial output port, a second serial output port, a third serial output port and a fourth serial output port, that is, a quad output (Quad Output) port.

[0050] In this embodiment, the control unit instructing the second serial port to output data corresponding to the address to the storage unit refers to:

[0051] The control unit instructs the first serial output port, the second serial output port, the third serial output port and the fourth serial output port to simultaneously output the data of the storage unit corresponding to the address.

[0052] In this embodiment, the output data is jointly transmitted by four ports, which can increase the output data transmission speed by four times.

[0053] Figure 5 It is a timing diagram of this embodiment, and SO1, S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More