Non-volatile memory reading speed test circuit

A non-volatile, read-speed technology, applied in static memory, instruments, etc., to achieve accurate testing, high measurement accuracy, and easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

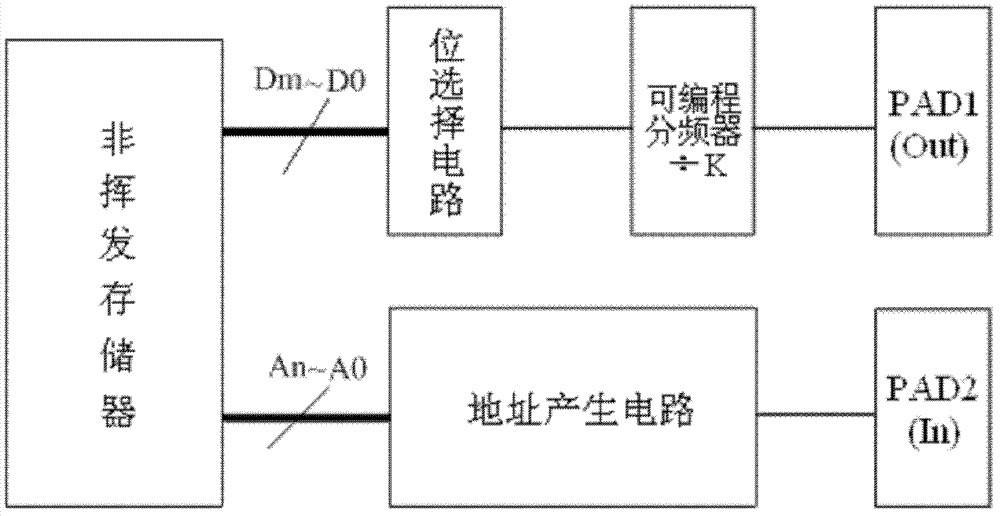

[0016] to combine figure 2 As shown, in an embodiment of the present invention, a FLASH whose output data bit width is 16 bits is taken as an example for description. The non-volatile memory reading speed test circuit includes: an address generation circuit, a bit selection circuit, and a programmable frequency divider. In the non-volatile memory, the data is pre-stored in a format in which every other address data is the same and adjacent address data is bit-inverse, and the data signals Dm-D0 are output according to the address jump of the address scanning signal. For example, address 0 stores 0xAAAA, address 1 stores 0x5555, and so on.

[0017] The address generating circuit generates an address scanning signal of the non-volatile memory under the drive of the external input clock (clock) input by the input pin PAD2, and continuously reads the non-volatile memory. For example, address scanning is realized by simply adding 1 to the address.

[0018] The data signals Dm-D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More