Formation method of fin field effect transistor

A technology of fin field effect transistors and fins, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve device performance problems and other problems, and achieve the effects of good performance, inaccessibility, and small volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

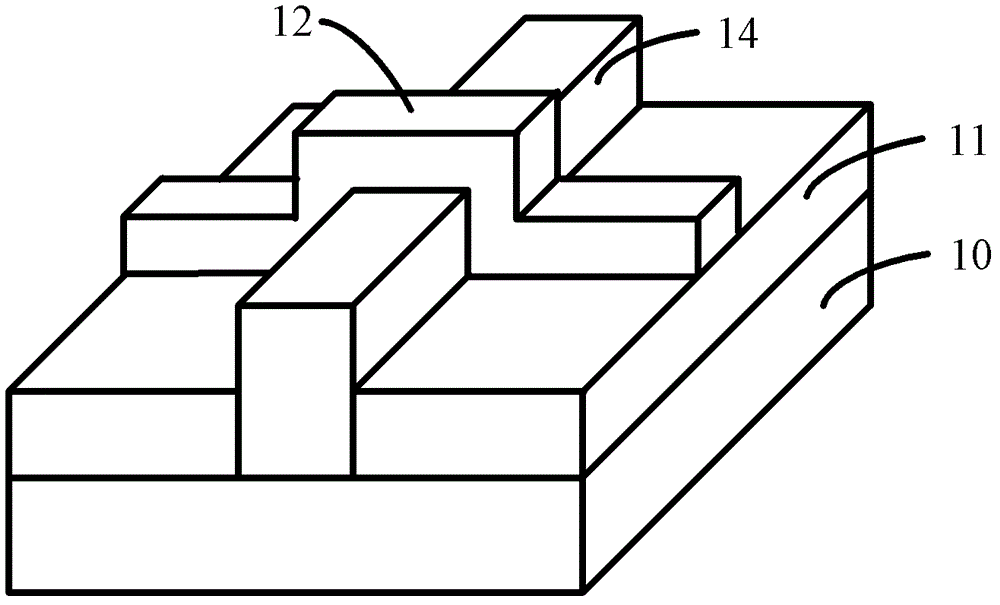

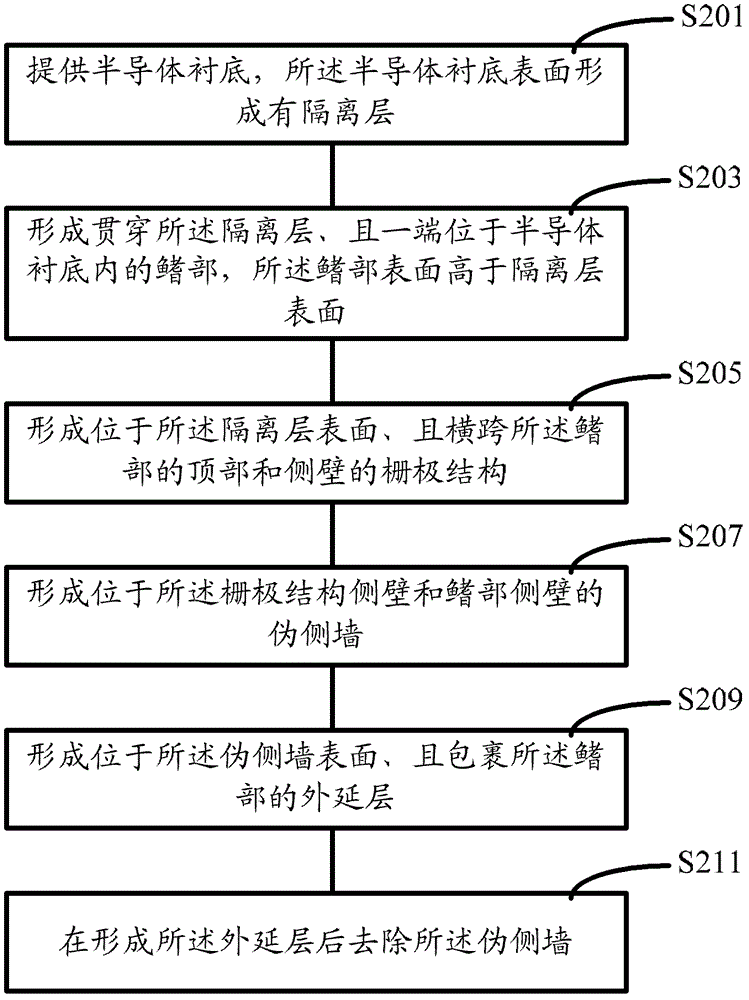

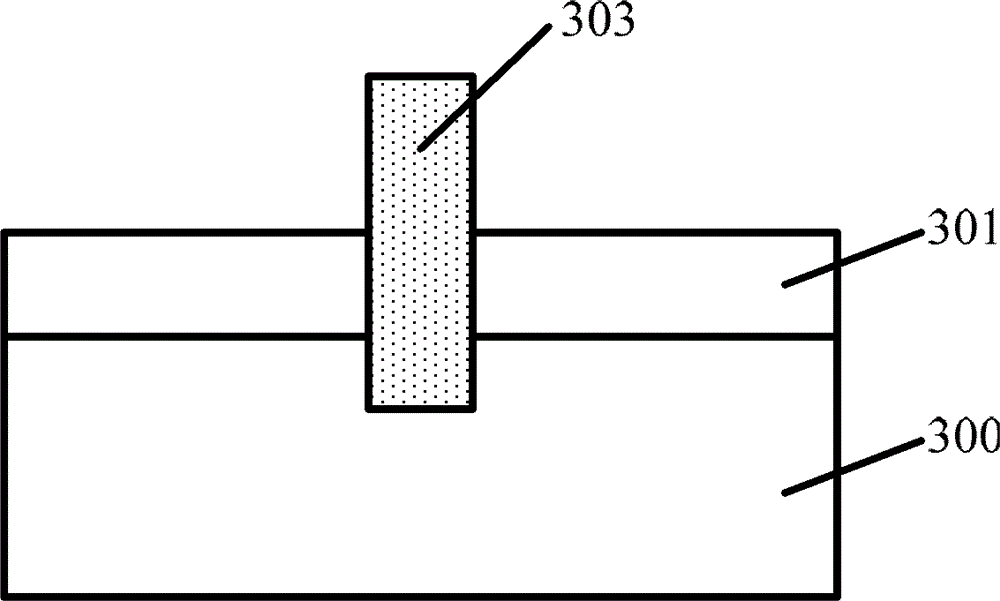

[0041] As mentioned in the background, in the prior art, as the process node is further reduced, the performance stability of the formed fin field effect transistor needs to be improved.

[0042] After research, the inventors found that with the further reduction of the process node, the distance between two adjacent fins is further reduced. After forming the gate structure, when the epitaxial layer wrapping the fins is formed, the The distance between the epitaxial layers of the two fins is difficult to control, and the formed epitaxial layers of the two adjacent fins are very easy to contact, which affects the subsequent process and seriously affects the performance of the FinFET.

[0043] Furthermore, the inventors found that before forming the epitaxial layer wrapping the fin, if dummy sidewalls are formed on the sidewalls of the fins, under the protection of the dummy sidewalls, the epitaxial layer is only formed on the undummy sidewalls. The surface of the fin covered by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More