System and method for testing off-chip driver impedance

A technology for testing circuits and drivers, which is applied in the direction of measuring resistance/reactance/impedance, measuring electrical variables, instruments, etc., and can solve problems such as difficulty in detecting through silicon vias 118

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

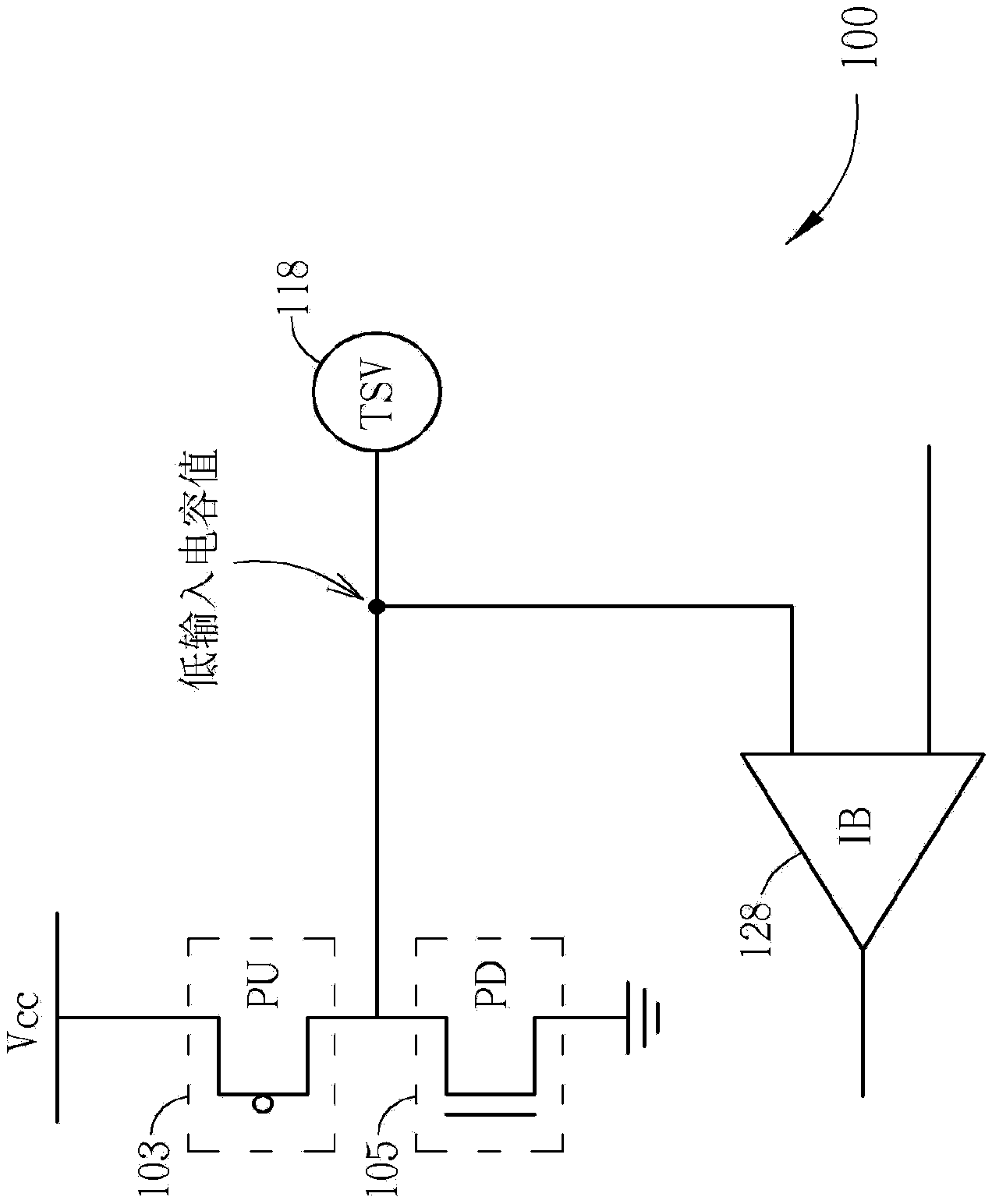

[0026] The invention discloses a test circuit and a test method, which can bring a relatively small capacitance value to the system when measuring the impedance of an off-chip driver coupled to a through-silicon via. In some embodiments, an OCD comparison test uses input buffers instead of directly connecting test pads to TSVs. In some cases, very little circuitry is added to the off-chip driver circuit in order to perform the off-chip driver comparison test or measure multiple off-chip drivers simultaneously.

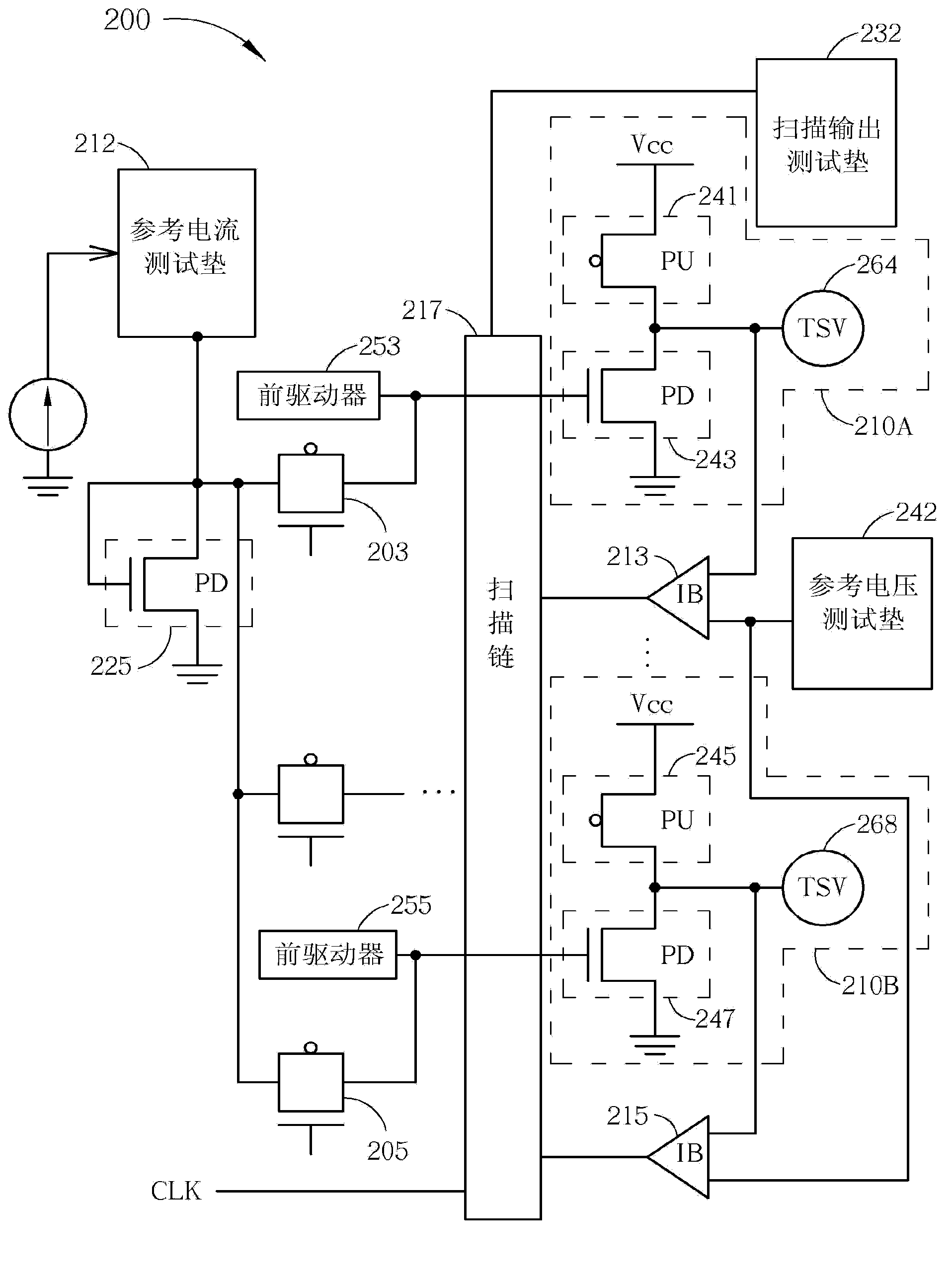

[0027] figure 2 is a schematic diagram of an embodiment of the test circuit 200 of the present invention. In the illustrated embodiment, the test circuit 200 includes a plurality of off-chip drivers 210A and 210B. The first off-chip driver 210A includes a first pull-up driver (in the present invention, interchangeable with a P-channel field effect transistor) 241 and a first pull-down driver (in the present invention, interchangeable with an N-channel field-effect t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More