Digital hardware circuit logical error diagnosis mechanism

A hardware circuit, logic error technology, applied in the field of formal verification, can solve the problems of inaccuracy, compromise between accuracy and processing capacity, limited processing capacity, etc., to achieve the effect of improving stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

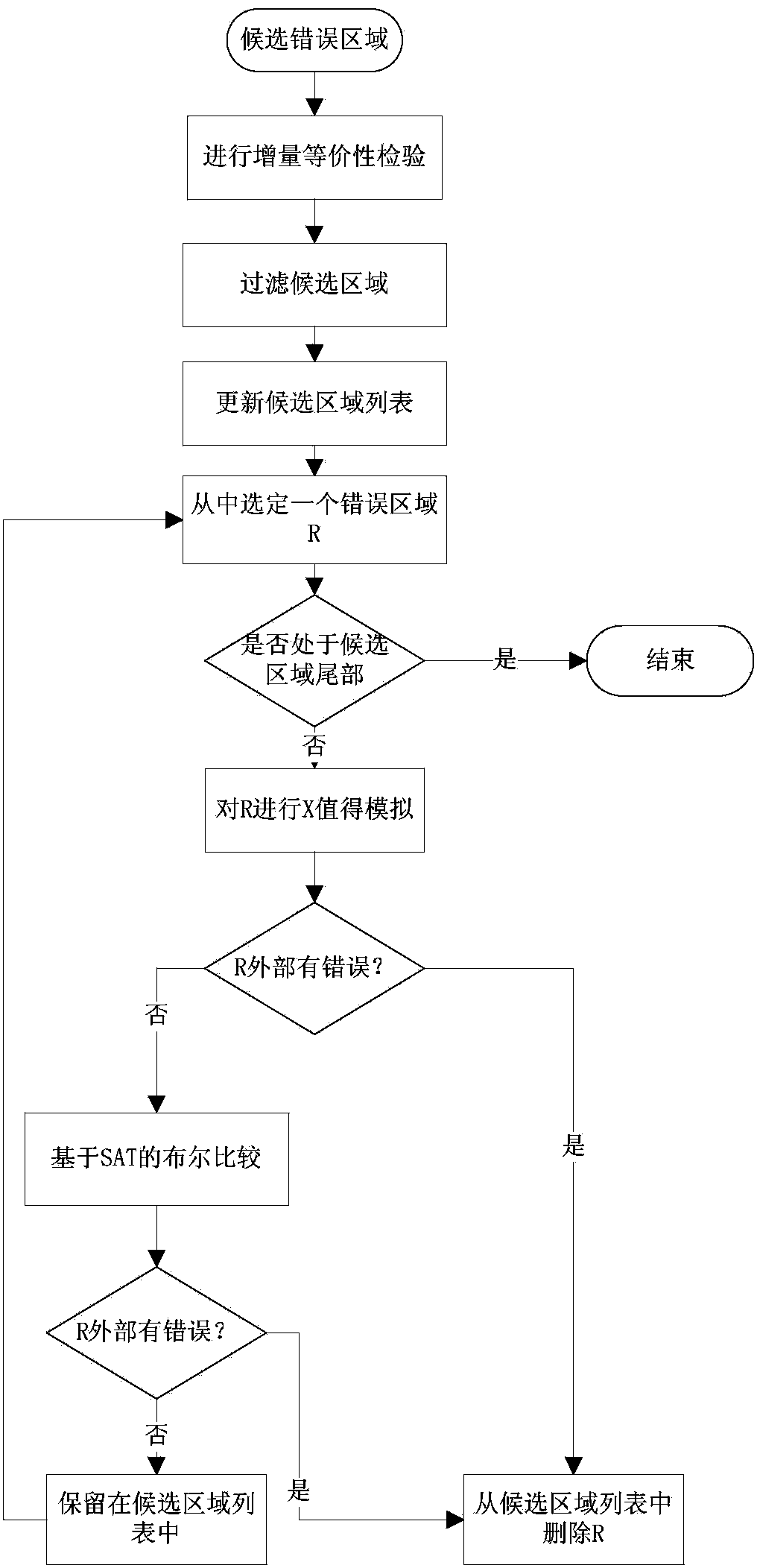

[0017] The present invention is a diagnostic mechanism for digital hardware circuit logic errors, comprising the following processing steps:

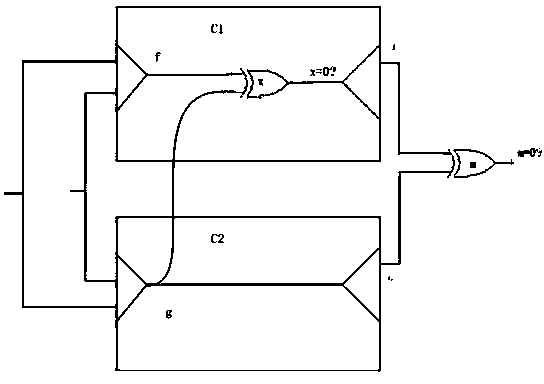

[0018] Step 1: Filter candidate regions

[0019] According to the internal characteristics of candidate error regions, some candidate regions are selectively removed by using structural similarity. To find equivalent area pairs from the selected candidate areas, that is, possibly equivalent area pairs, you can use the method of topological sorting, that is, sorting in the order of fan-in priority, so that the previously derived internal equivalence can be It is used for the subsequent equivalence derivation process, that is, to simplify the miter circuit by replacing the equivalent area. The core step of the method is to use the incremental satisfiability algorithm to verify the equivalence of all candidate regions sequentially according to topological sorting or to prove that they are not equivalent. If a region f is a region that ha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More