FPGA-based (field programmable gate array-based) USB (universal serial bus) to multilink interface circuit

An interface circuit and road link technology, applied in the field of electronic circuits, can solve the problems of increasing circuit cost and complexity, slow JTAG transmission speed, affecting data transmission speed, etc., to achieve the effect of improving transmission speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

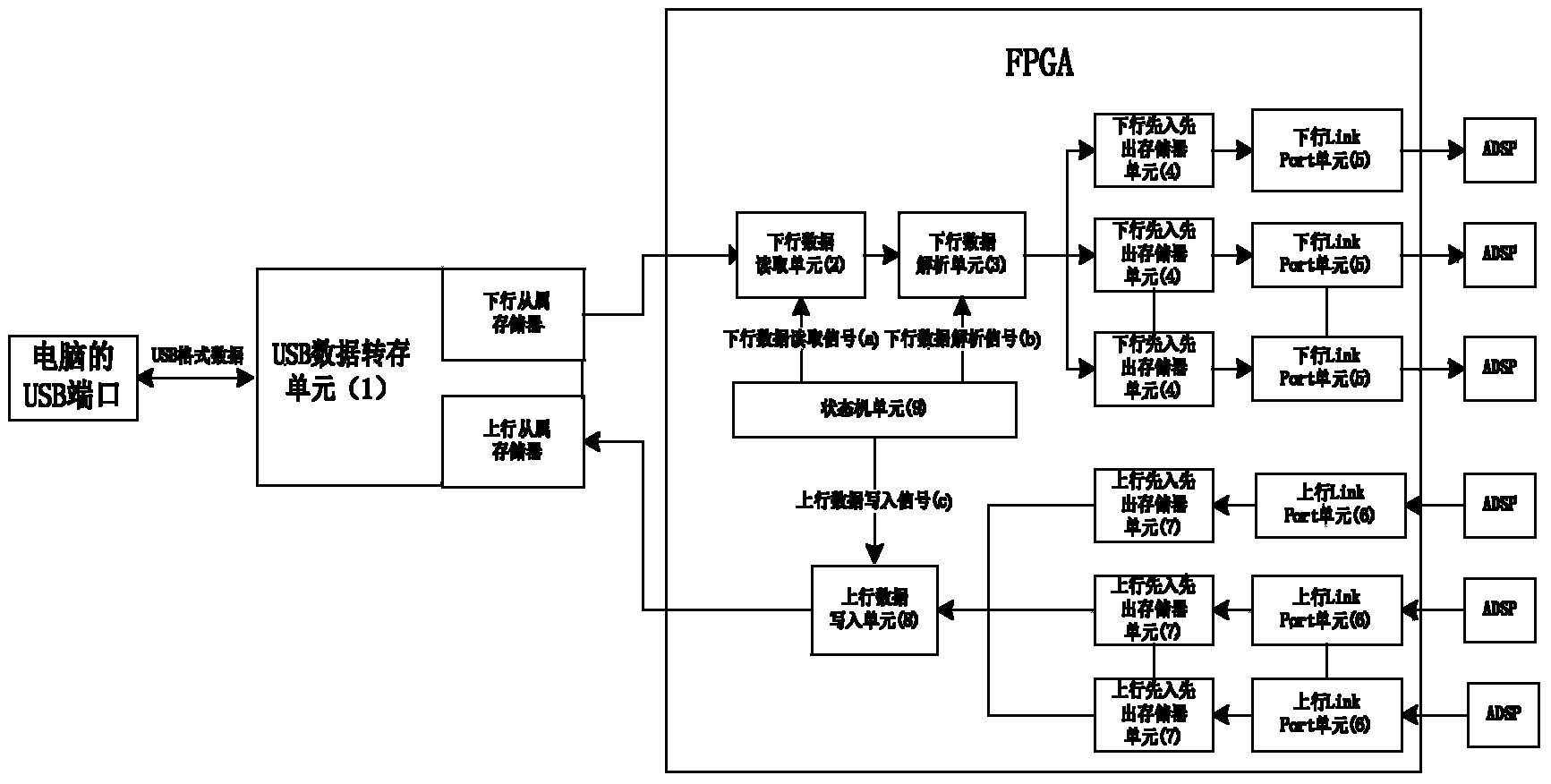

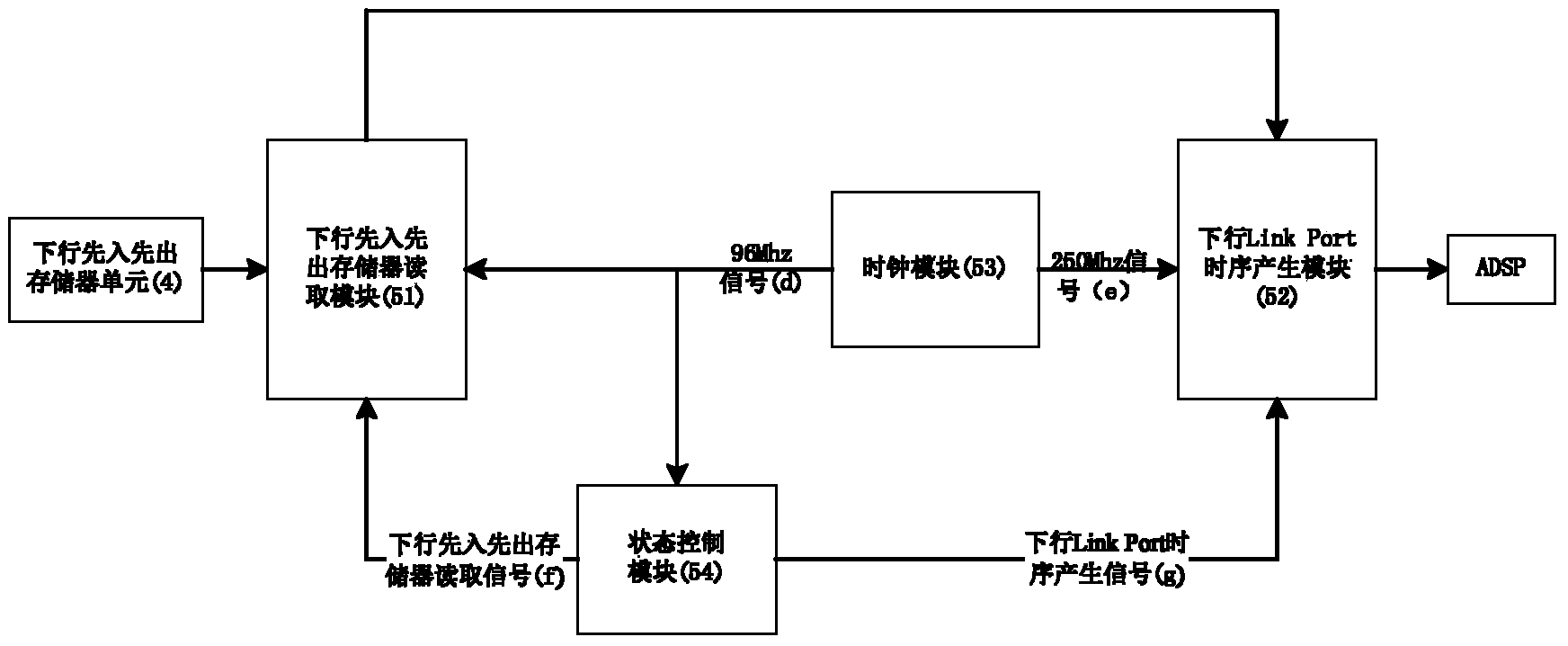

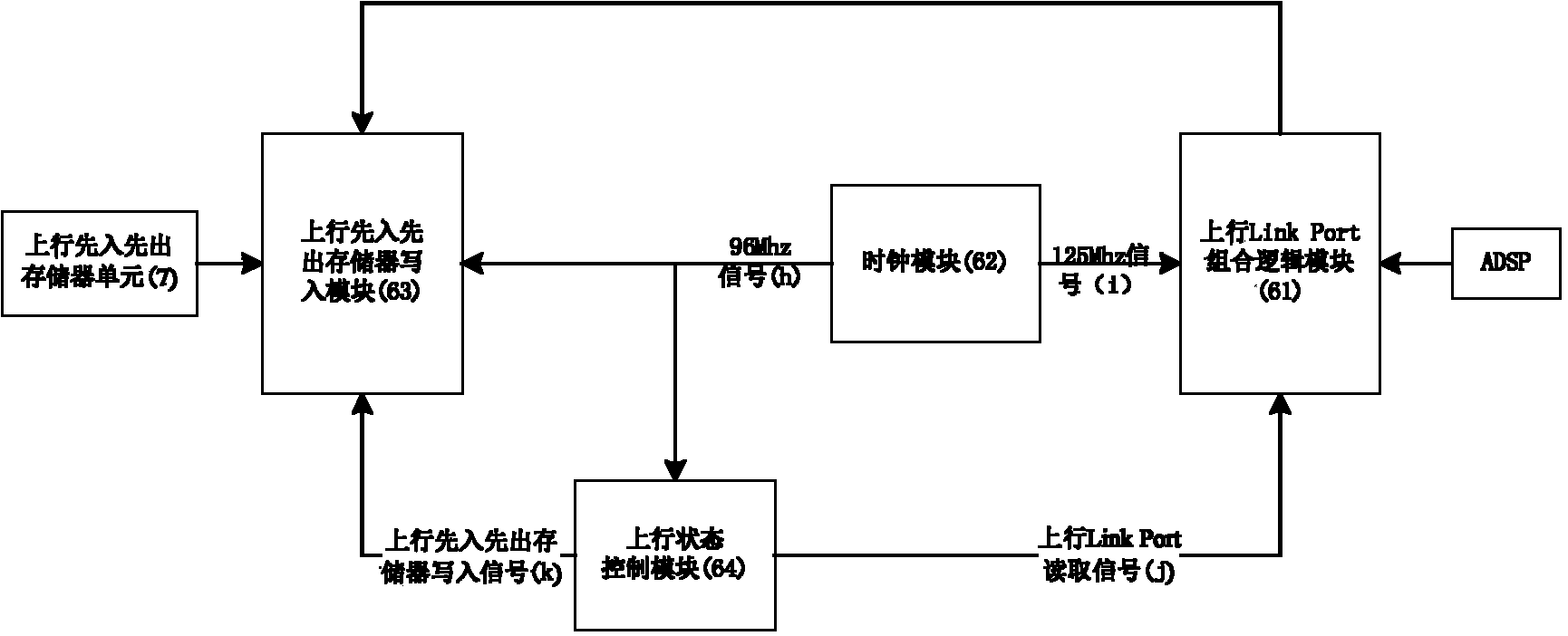

[0022] Reference figure 1 , The present invention includes: USB data transfer unit 1, downstream data reading unit 2, downstream data analysis unit 3, N downstream first-in first-out memory units 4, N downstream Link Port units 5, N upstream Link Port units 6. N upstream first-in first-out memory units 7, upstream data writing unit 8 and state machine unit 9; the USB data transfer unit 1 is composed of a CY7C68013A chip connected with a peripheral resistance-capacitance component, and the downstream data reading unit 2 , Downstream data analysis unit 3, N downstream first-in first-out memory unit 4, N downstream Link Port unit 5, N upstream Link Port unit 6, N upstream first-in first-out memory unit 7, upstream data writing unit 8 and state machine unit 9 are implemented inside FPGA, among them:

[0023] The input end of the USB data transfer unit 1 is connected to the USB interface of the computer, and the output end is connected to the downstream data reading unit 2. During dow...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More