High power consumption chip packaging structure

A chip packaging structure, high power consumption technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of poor heat dissipation of high-power chips, increased packaging costs, etc., to improve system signal integrity and power integrity, The effect of reducing junction temperature difference and low process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

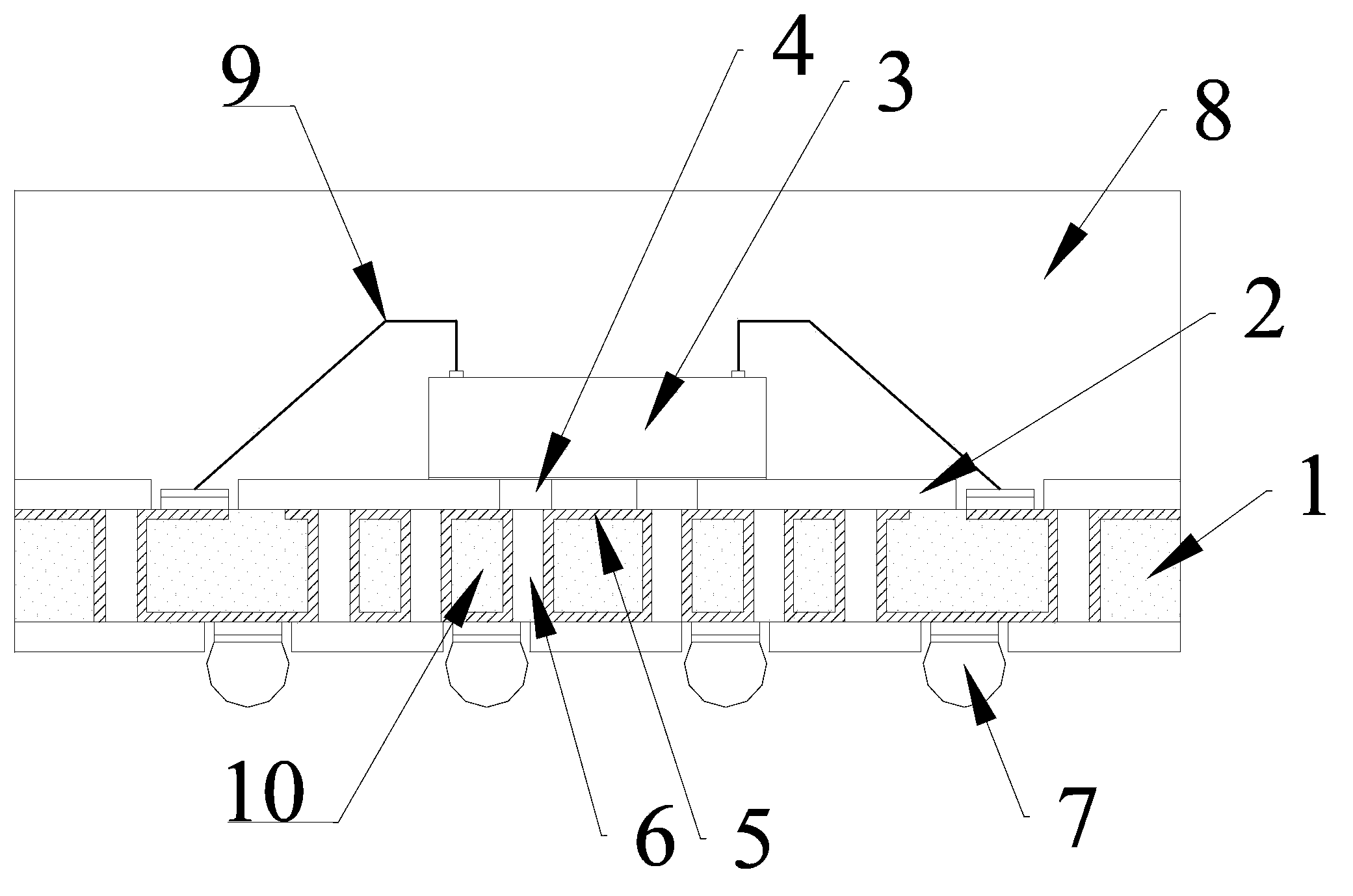

[0025] Such as figure 1 Shown: a large power consumption chip packaging structure, including: a substrate 1, with a top surface and a bottom surface opposite; the inside of the substrate 1 is a substrate 10, and the surface of the substrate 1 is an etched metal circuit layer 5, The metal circuit layer 5 is also coated with a solder resist layer 2;

[0026] It also includes a chip 3, which is arranged on the top surface of the substrate 1; directly below the chip 3 and on the solder resist layer 2 of the substrate 1, a plurality of green oil openings 4 are arranged, and the areas of the green oil openings 4 are exposed The metal circuit layer 5 is directly in contact with the chip 3;

[0027] It also includes a plurality of via holes 6 arranged on the substrate 1 and arranged under the chip 3;

[0028] It also includes a plurality of heat dissipation solder balls 7, which are arranged on the bottom surface of the substrate 1, and the heat dissipation solder balls 7 are welded...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com