Quarter-Rate 4-Tap Decision-Feedback Equalizer for High-Speed Serial Interface Receiver

A high-speed serial interface, decision feedback equalization technology, applied to the shaping network in the transmitter/receiver, baseband system components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The implementation of the present invention will be described in detail below in conjunction with the drawings and examples.

[0043] The preferred embodiments will be described in detail below in conjunction with the accompanying drawings. It should be emphasized that the following description is only exemplary and not intended to limit the scope of the invention and its application.

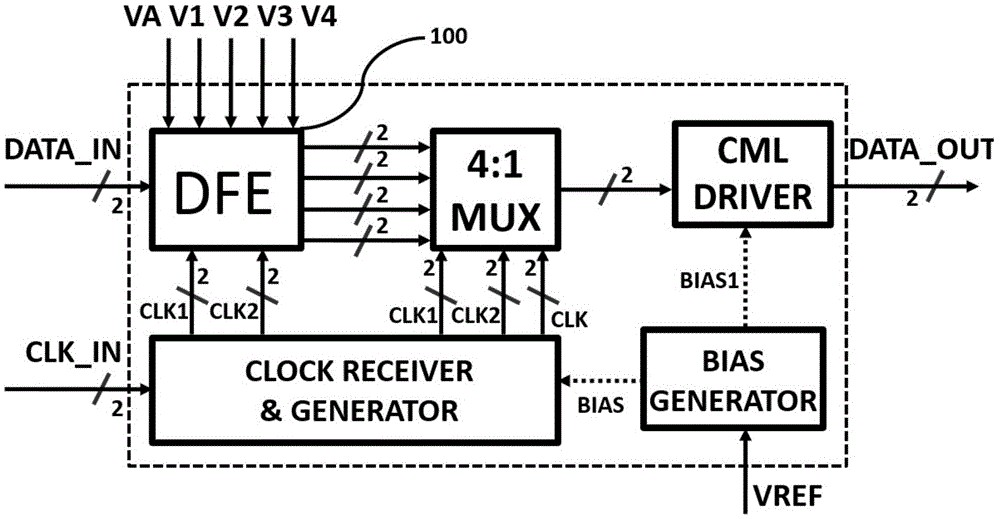

[0044] figure 1 is a simplified high-speed serial interface transceiver circuit block diagram. It includes 1 / 4 rate 4-tap decision feedback equalizer 100, 4:1 multiplexer (MUX), clock receiver and generator (ClockReceiver&Generator), current mode logic driver circuit (CMLDriver) and bias generation circuit (BiasGenerator ). The clock receiver and generator receives the half-rate CML level differential clock signal input from the outside, passes through the frequency divider and CML to CMOS circuit, and generates four 1 / 4-rate CMOS clock signals CLK1 and CLK2 with a phase shift of 90 d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More