Universal computer simulation testing platform based on CPCI bus

A technology of computer simulation and test platform, which is applied in the direction of detecting faulty computer hardware, etc. It can solve the problems of single state test, small expansion space, and poor configuration flexibility, so as to improve test coverage, realize synchronous work, and reduce Effect of hardware cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

[0024] Take a flight control computer simulation test as an example. The flight control computer is connected with peripheral devices through various interfaces, including analog, switch, communication and other interfaces. The invention is adopted as the simulation test platform of the flight control computer.

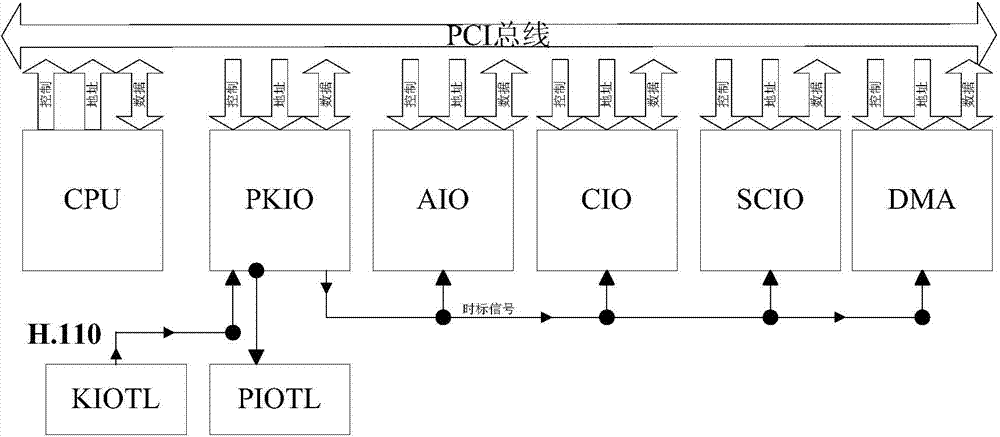

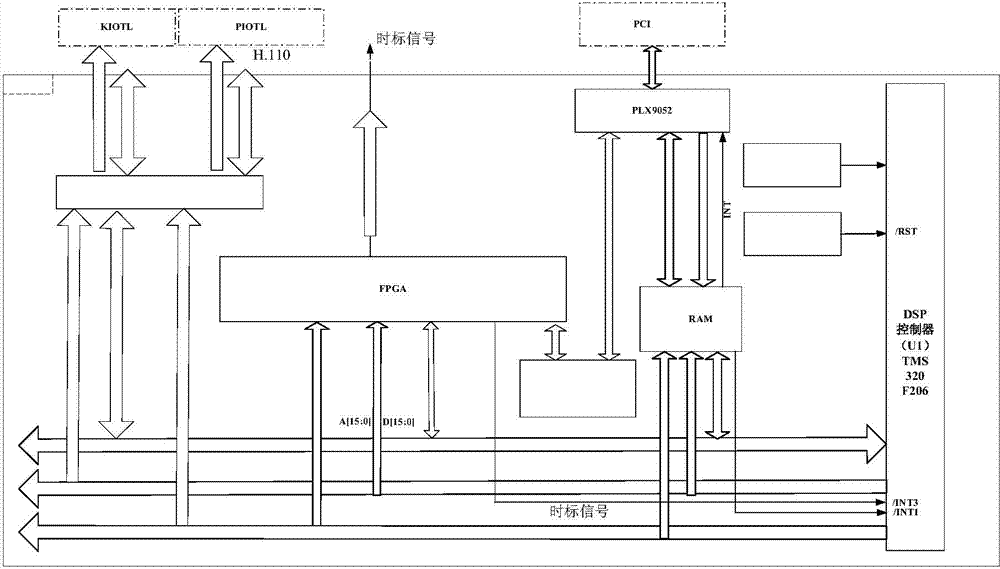

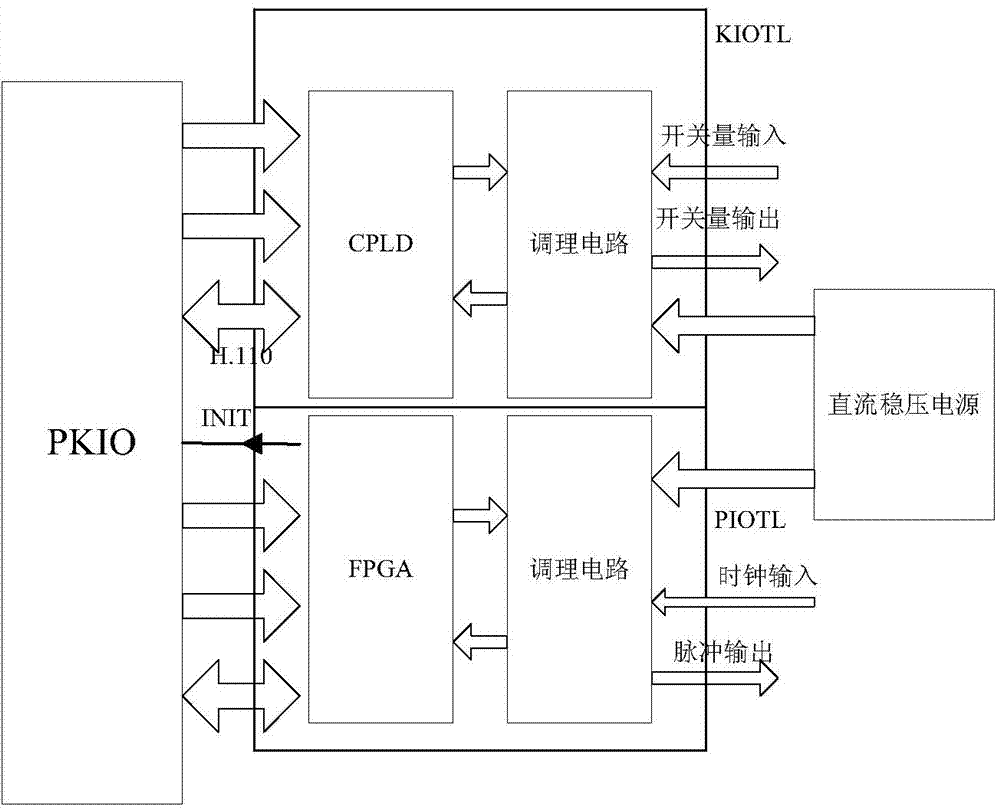

[0025] see figure 1 , the present invention is a kind of general-purpose computer emulation test platform based on CPCI bus, comprises CPCI bus cabinet, expansion plate card, and is arranged on the CPU template and the PKIO template that are connected with CPCI bus cabinet inside CPCI bus cabinet; Described CPCI bus cabinet The secondary bus conforming to the H.110 standard is expanded through the J4 slot provided on the top; each expansion board is connected to the CPCI bus and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com