IGBT (insulated gate bipolar transistor) structure with built-in diodes and method for manufacturing IGBT structure

A technology with built-in diodes and manufacturing methods, applied in the direction of diodes, semiconductor/solid-state device manufacturing, transistors, etc., can solve expensive and other problems, and achieve the effects of enhanced stability, uniform structure distribution, and uniform distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

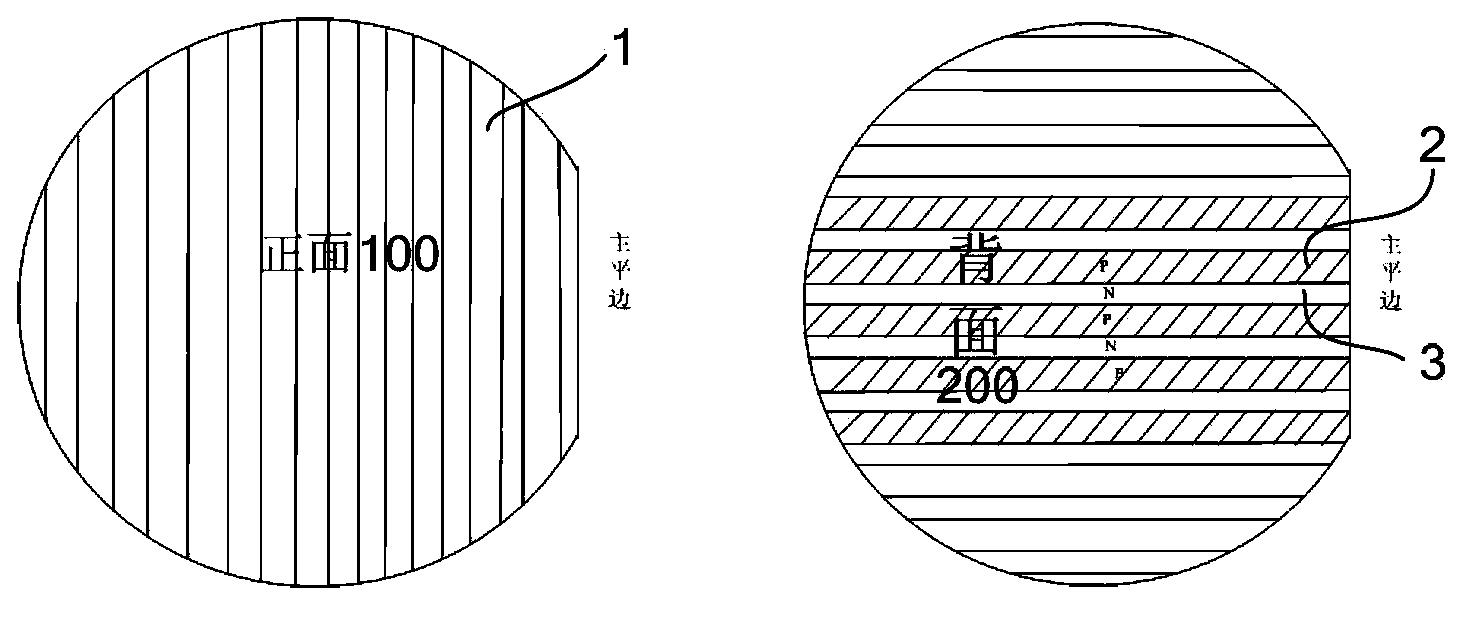

[0055] Figure 5-6 It is a structural cross-sectional view of the intermediate steps of the method for forming p-type and n-type strip-shaped doped regions on the back of the wafer according to Embodiment 1 of the present invention. Such as Figure 5-6 As shown, step S3 includes:

[0056] Step S311: Form a patterned first mask layer 110 on the back side 200 of the wafer 300, the first mask layer 110 covers the area of the back side 200 preset as a p-type strip-shaped doped region, such as Figure 5 shown.

[0057] Step S312: performing p-type doping on the back surface 200 of the wafer 300, such as Figure 5 shown.

[0058] Step S313: removing the first mask layer 110 to form p-type strip-shaped doped regions 2 and n-type strip-shaped doped regions 3, such as Figure 6 shown.

Embodiment 2

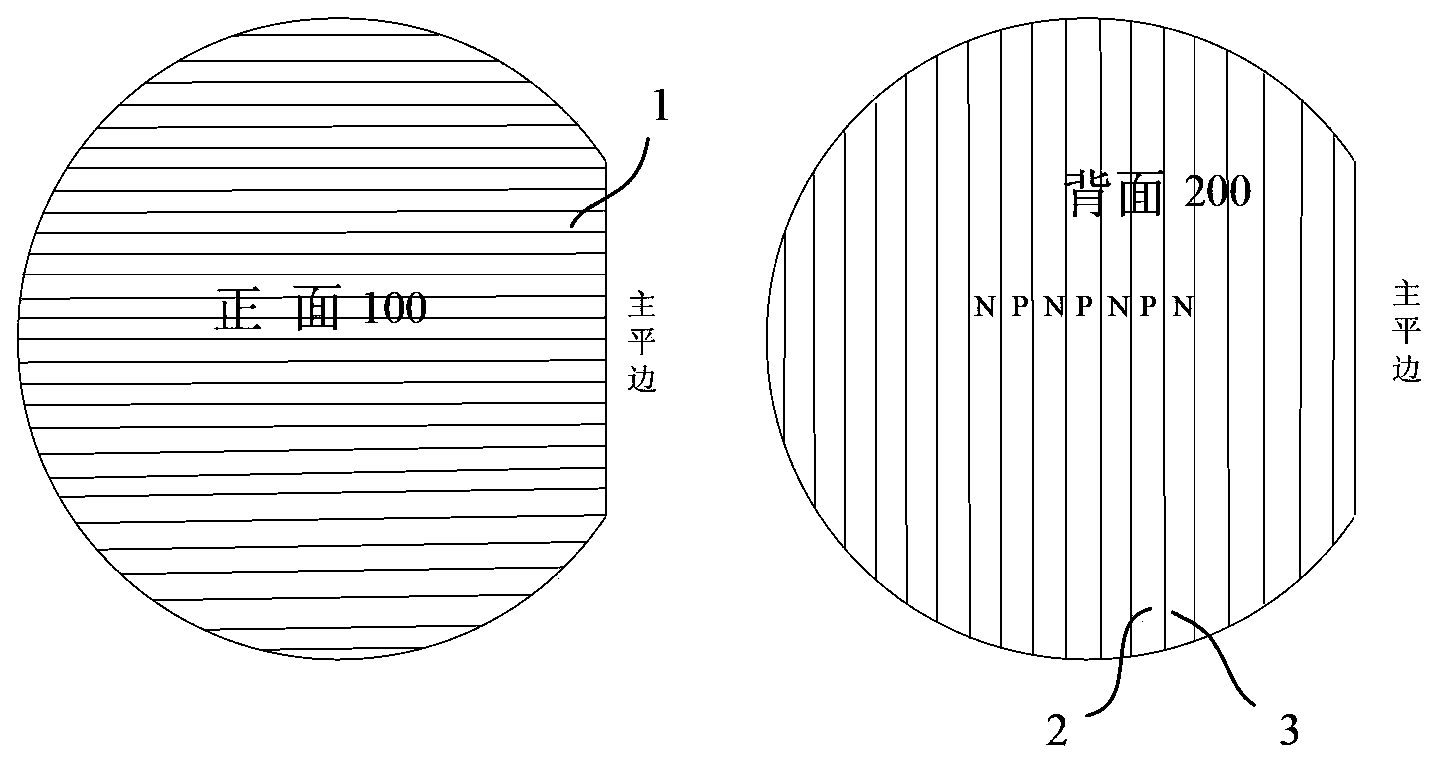

[0060] Figure 7-9 It is a structural cross-sectional view of the intermediate steps of the method for forming p-type and n-type strip-shaped doped regions on the back of the wafer according to Embodiment 2 of the present invention. Such as Figure 7-9 As shown, step S3 includes:

[0061] Step S321: Perform n-type doping on the back surface 200 of the wafer 300, such as Figure 7 shown.

[0062] Step S322: Forming a patterned second mask layer 111 on the back side 200 of the wafer 300, the second mask layer 111 covers the area of the back side 200 preset as an n-type strip-shaped doped region, such as Figure 8 shown.

[0063] Step S323: performing p-type doping on the back side 200 of the wafer 300, so that the exposed back side 200 region is reversed to p-type doping, such as Figure 8 shown.

[0064] Step S324: removing the second mask layer 111 to form p-type strip-shaped doped regions 2 and n-type strip-shaped doped regions 3, such as Figure 9 shown.

Embodiment 3

[0066] Figure 10-12 It is a structural cross-sectional view of the intermediate steps of the method for forming p-type and n-type strip-shaped doped regions on the back of the wafer according to the third embodiment of the present invention. Such as Figure 10-12 As shown, step S3 includes:

[0067] Step S331: performing p-type doping on the back surface 200 of the wafer 300, such as Figure 10 shown.

[0068] Step S332: Form a patterned third mask layer 112 on the back side 200 of the wafer 300, the third mask layer 112 covers the area of the back side 200 preset as a p-type strip-shaped doped region, such as Figure 11 shown.

[0069] Step S333: Perform n-type doping on the back side 200 of the wafer 300, so that the exposed back side 200 region is reversed to n-type doping, such as Figure 11 shown.

[0070] Step S334: removing the third mask layer 112 to form p-type strip-shaped doped regions 2 and n-type strip-shaped doped regions 3, such as Figure 12 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More