Mass production testing method of CIS chip

A test method and chip technology, applied in electronic circuit testing and other directions, can solve the problems of rising chip testing costs, high testing machine prices, and reduced test program execution efficiency, and achieve the effect of improving computing speed and shortening data processing time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the embodiments and accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

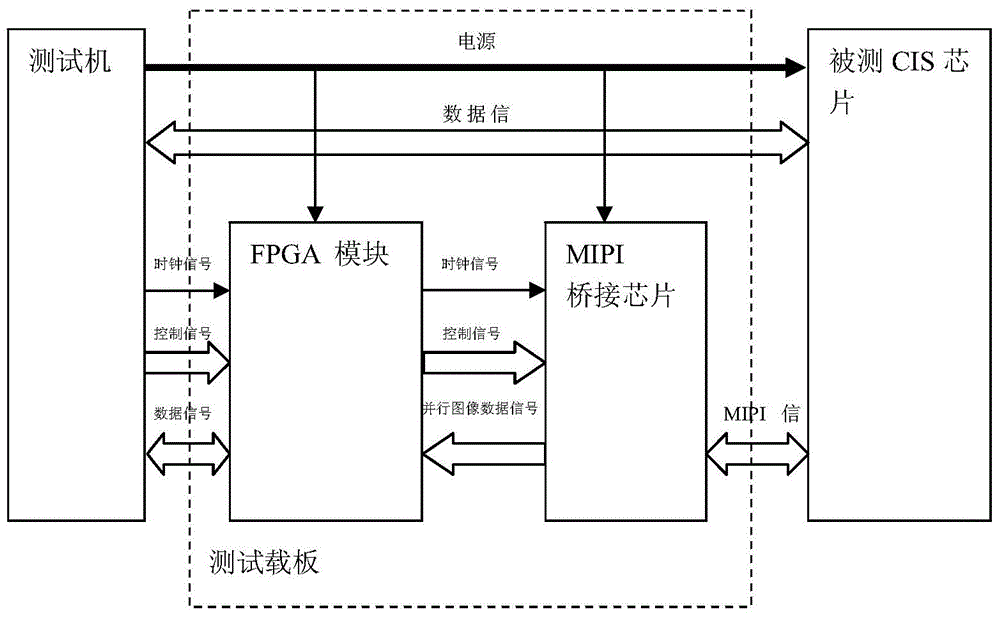

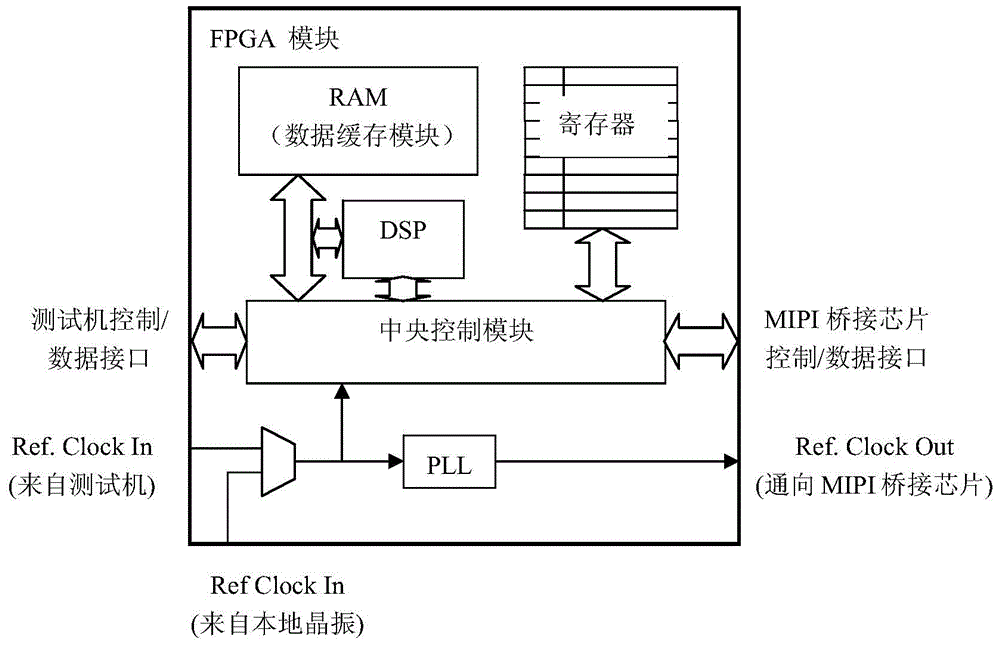

[0041] The present invention relates to the mass production test technology of CIS (CMOS Image Sensor) chip with MIPI (Mobile Industry Processor Interface) high-speed port of the mobile communication industry processor interface. The technology can adopt Field Programmable Gate Array FPGA (Field Programmable Gate Array) chip and MIPI serial-to-parallel data bridge chip to realize the CP (Chip Probe) test and FT (Final Test) test for mass production of CIS chips.

[0042] figure 1 Shown is the CIS chip test system based on the FPAG module (FPAG chip) used in an embodiment of the present invention, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More