Control flow graph reconstruction method for scheduled assembly codes

A control flow graph and scheduling technology, applied in program control design, program control devices, instruments, etc., can solve problems such as low efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

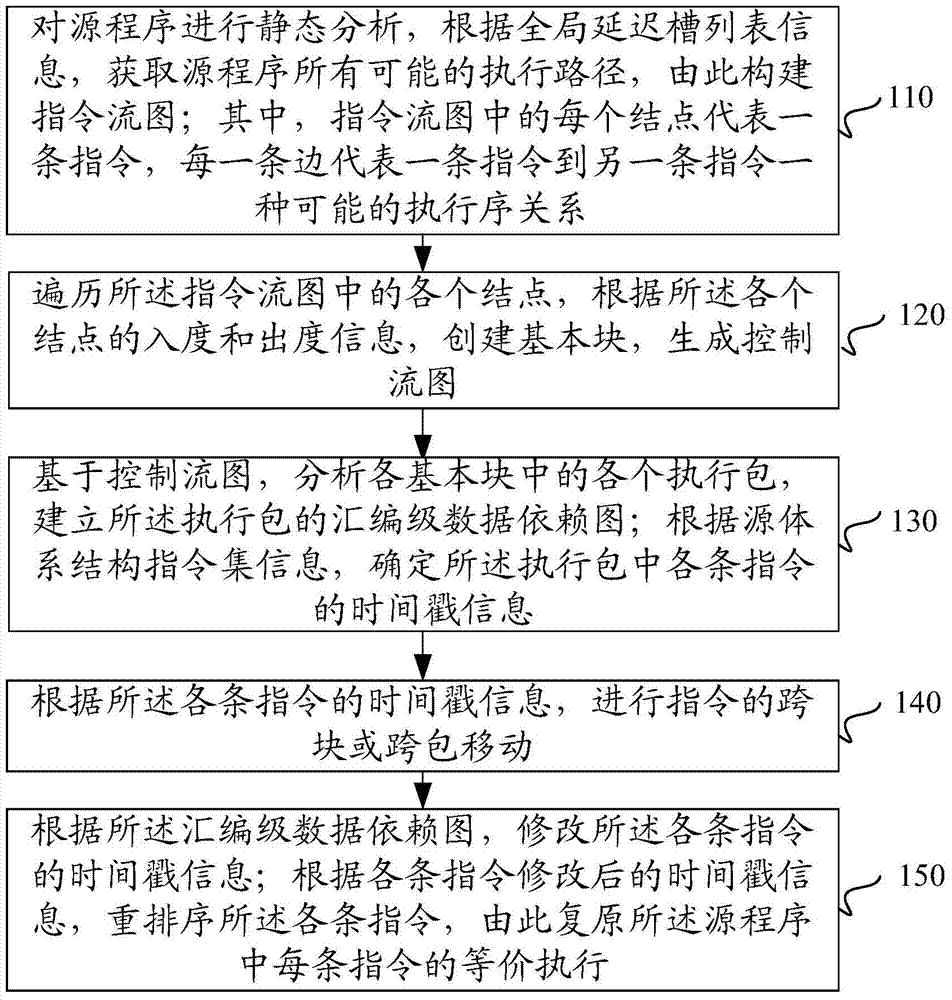

[0027] figure 1 It is a flowchart of a method for reconstructing a control flow graph of scheduled assembly code in an embodiment of the present invention. Such as figure 1 As shown, embodiments of the present invention include:

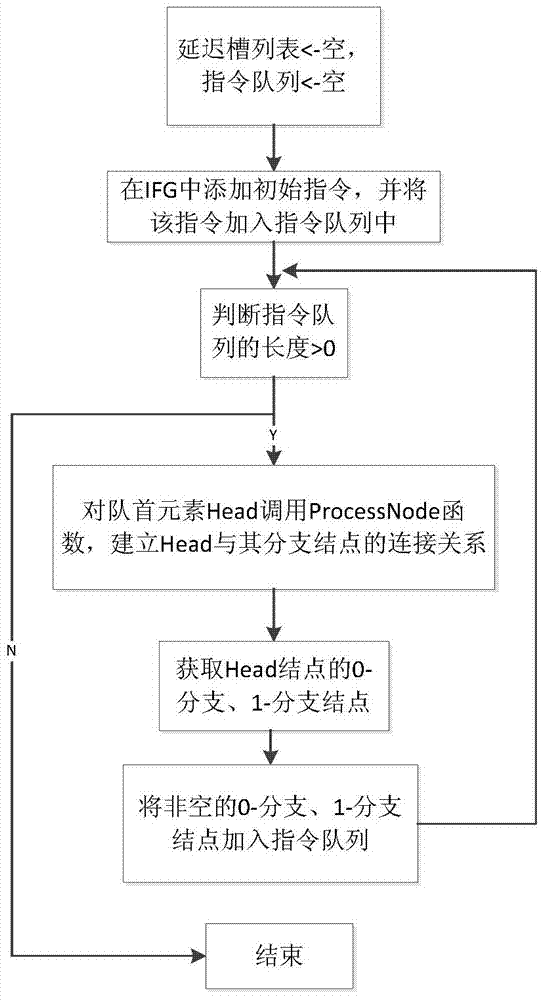

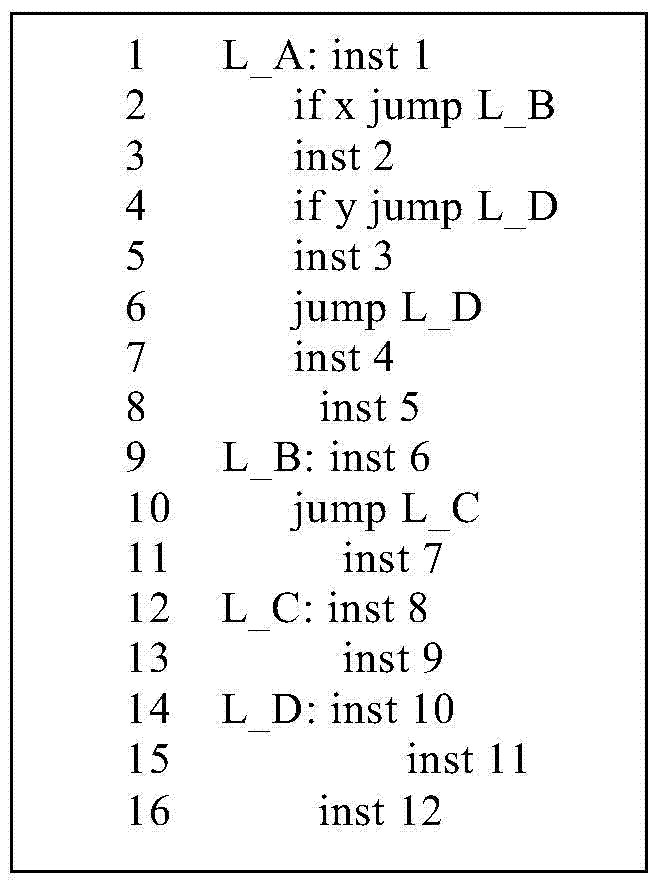

[0028] Step 110, perform static analysis on the source program, and obtain all possible execution paths of the source program according to the information of the global delay slot list, thereby constructing an instruction flow graph; wherein, each node in the instruction flow graph represents an instruction, and each An edge represents a possible execution order relationship from one instruction to another.

[0029] Only the branch instruction in the instruction set affects the control direction of the program. For a specific target architecture, there is a certain number of delay slots f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More