Semiconductor structure and fin field-effect tube forming method and etching device

A technology of a fin field effect transistor and an etching device, which is applied to the device for coating liquid on the surface, the manufacture of semiconductor devices, and semiconductor/solid state devices, etc. , the depth of the second groove 18 is difficult to control, etc., to achieve the effect of improving accuracy, high precision and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

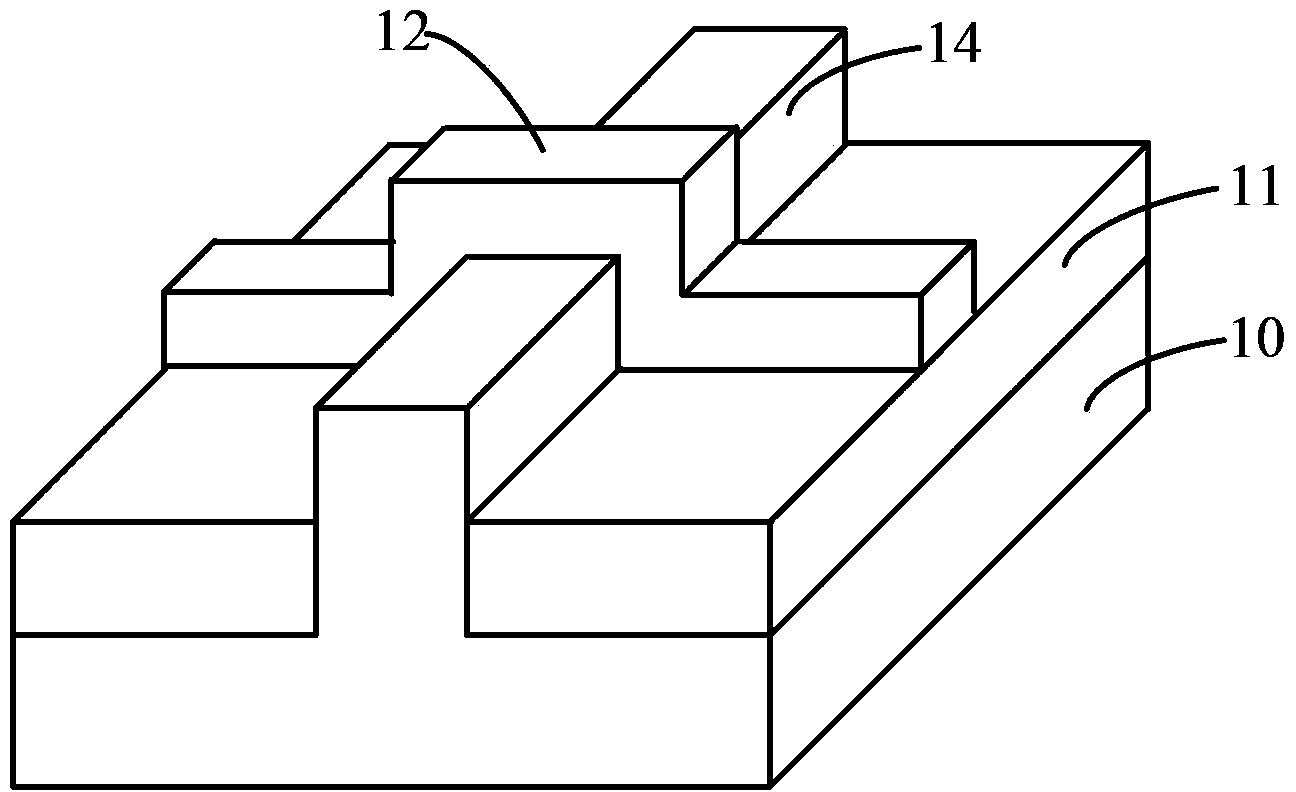

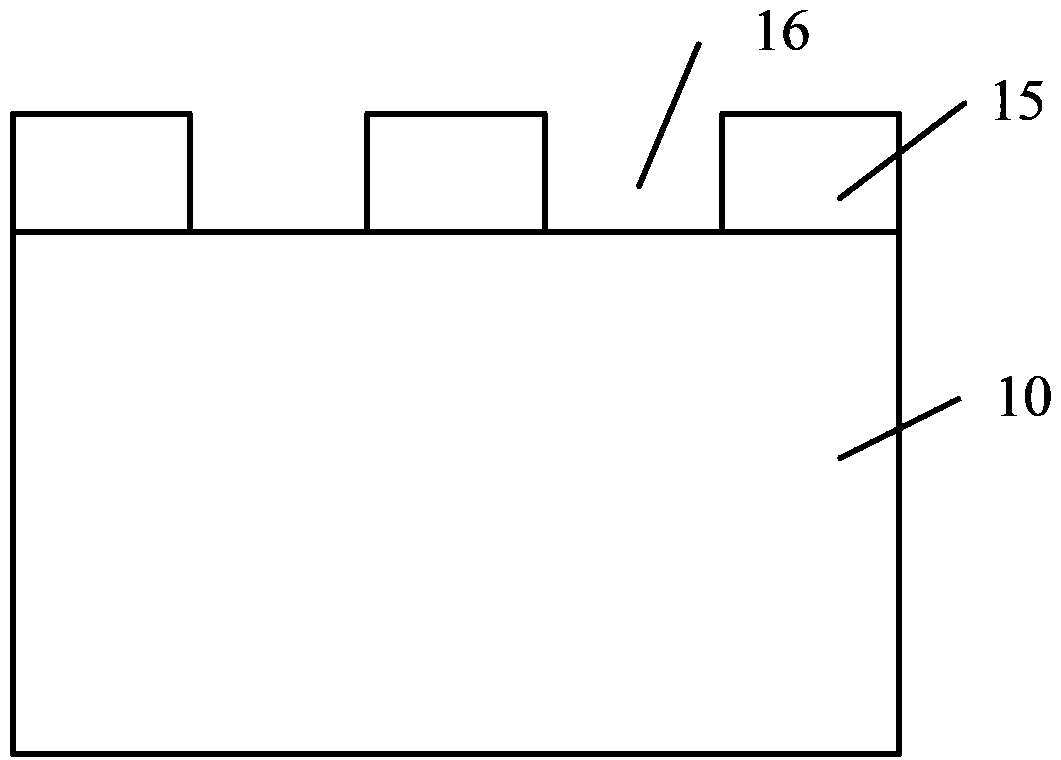

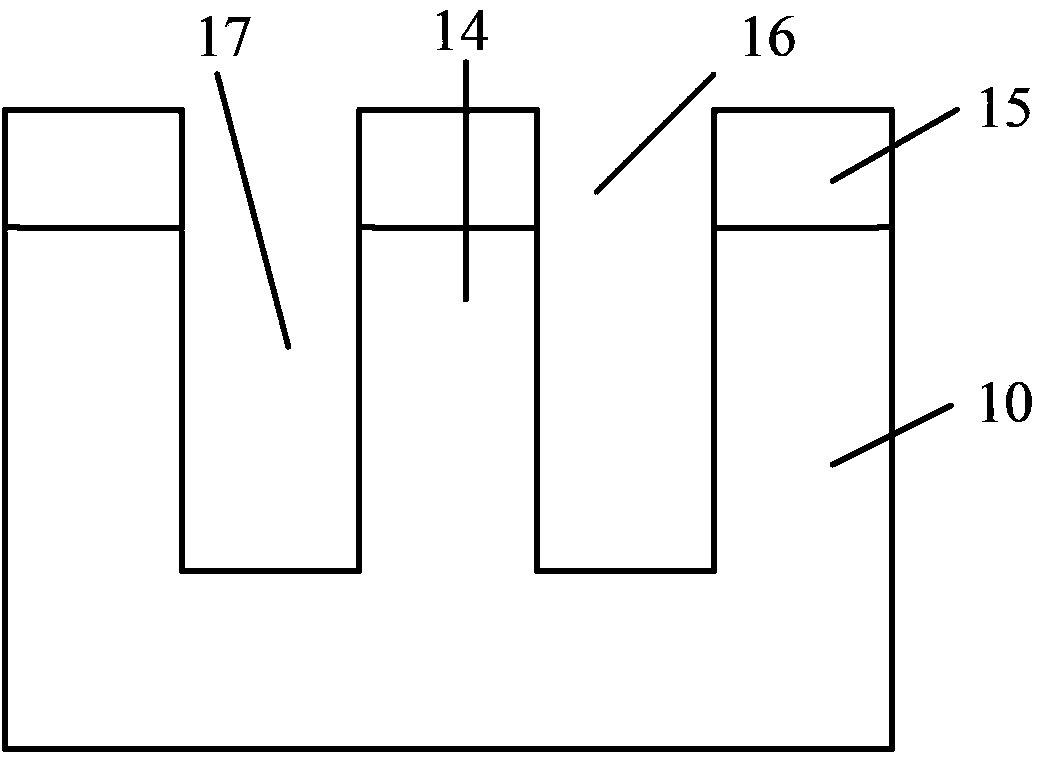

[0052] In the production process of the existing fin field effect transistor, the process of etching back the height of the exposed part of the isolation structure is a dry etching process or a wet etching process, but it is difficult to control the end point of the etching by using the existing etching process , so that it is difficult to accurately control the depth of the isolation structure being etched back, so that there is an error in the width of the exposed fin surface, and after the gate structure is formed on the exposed fin surface, the threshold voltage of the FinFET will be biased. Shift, affecting the stability of the FinFET.

[0053] In order to solve the above problems, the inventor proposes an etching device and a method for forming a semiconductor structure and a fin field effect transistor by using the etching device. In the method for forming the fin field effect transistor, when etching back the isolation structure, first A process of spraying liquid is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More