Defect density calculation method

A technology of defect density and calculation method, which is applied in the direction of electrical components, circuits, semiconductor/solid-state device testing/measurement, etc., can solve the problems of defect density error, unconsidered device test item coefficient, etc., and achieve the effect of reducing error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

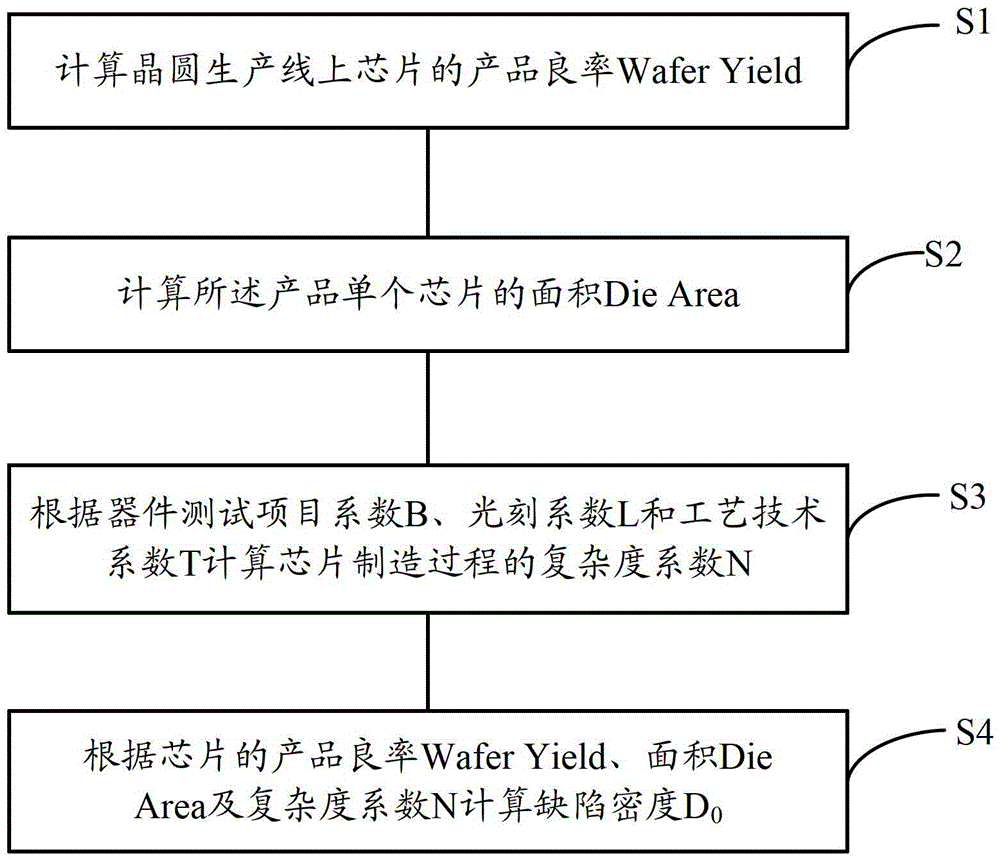

[0041] The invention discloses a defect density calculation method, comprising the following steps:

[0042] S1. Calculate the product yield WaferYield of the chip on the wafer production line;

[0043] S2. Calculate the area DieArea of a single chip of the product;

[0044] S3. Calculate the complexity coefficient N of the chip manufacturing process of the product according to the device test item coefficient DeviceTestBin, the lithography coefficient LithoCoefficient and the process technology coefficient TechnologyCoefficient;

[0045] S4. Calculate the defect density D according to the product yield rate WaferYield of the chip, the area DieArea and the complexity coefficient N 0 .

[0046] The present invention calculates the complexity coefficient N through the device test item coefficient B, the lithography coefficient L and the process technology coefficient T, and calculates the defect density through the corrected N, which reduces the error between the defect dens...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com