Three-level pulse extension control method and three-level pulse extension device of DSPACE based on FPGA

A technology of a control device and a control method, which is applied to the output power conversion device, electrical components, and the conversion of AC power input to DC power output, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

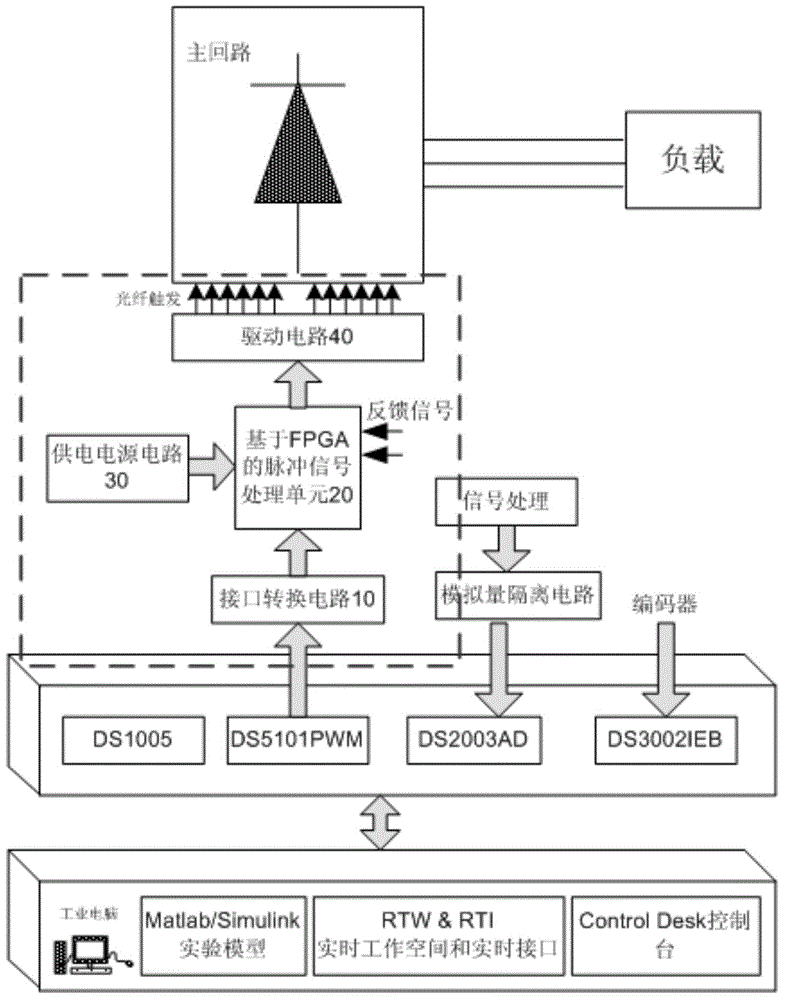

[0037] Such as Figure 1 to Figure 7 As shown, a three-level pulse extension control device based on FPGA-based DSPACE includes an interface conversion circuit 10, an FPGA-based pulse signal processing unit 20, a power supply circuit 30, and a drive circuit 40; the DS5101 digital pulse board of DSPACE The pulse waveform input to the interface conversion circuit 10, the interface conversion circuit 10 sends the pulse signal to the FPGA-based pulse signal processing unit 20 through logic level matching, and sends the pulse signal that meets the driving requirements to the pulse signal after necessary processing. The drive circuit 40 and the power supply circuit 30 provide power to the FPGA-based pulse signal processing unit 20 .

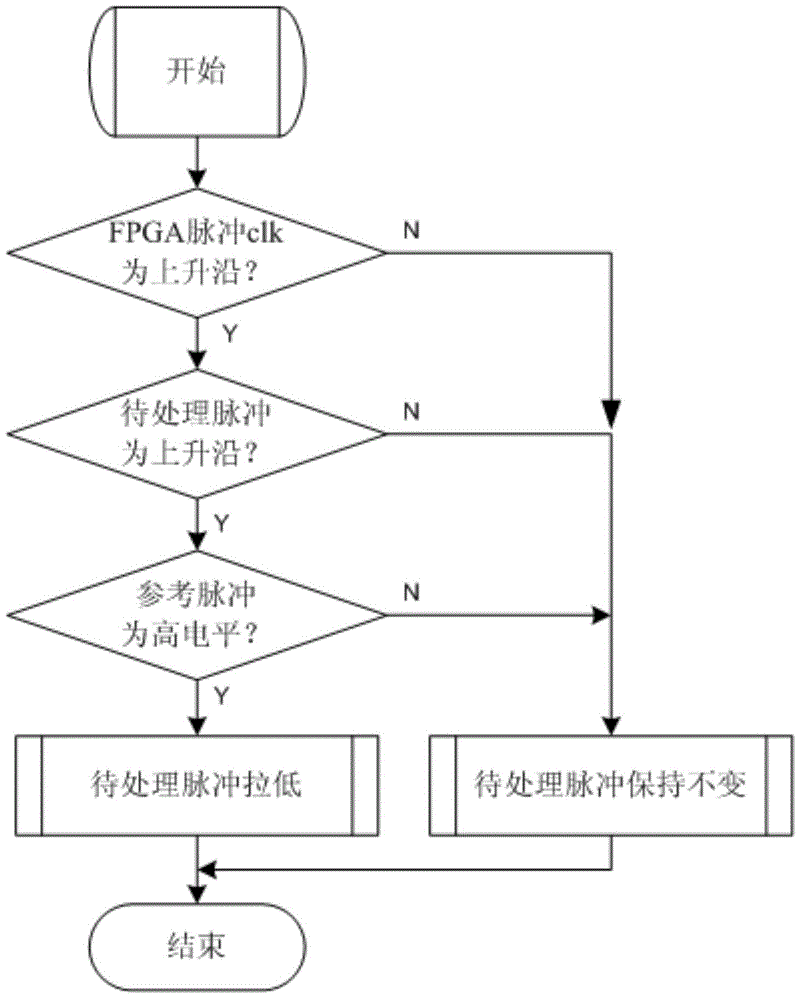

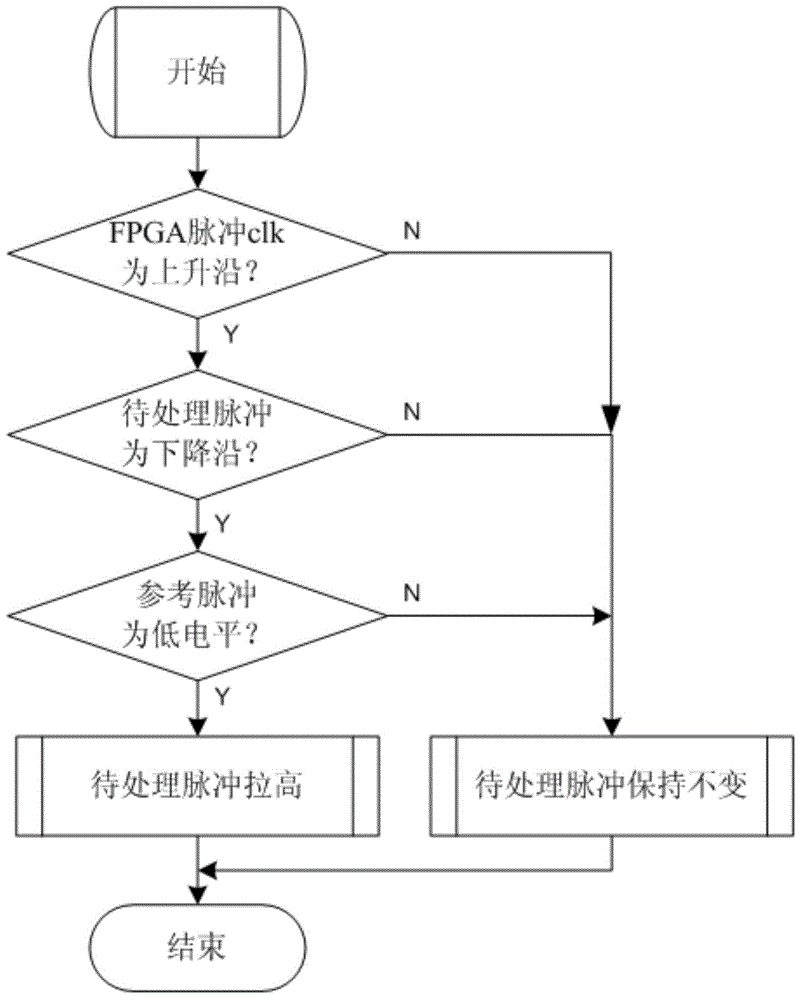

[0038] The FPGA-based pulse signal processing unit 20 is composed of a narrow pulse elimination unit, a dead zone setting unit and a power module protection unit. The pulse signal makes the pulse duty cycle reach 0% and 100% through the narrow pulse el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More