LDMOS power transistor array structure and realization method of layout of LDMOS power transistor array structure

A technology of power transistor and array structure, applied in electric solid device, semiconductor device, special data processing application, etc., can solve the problem of LDMOS power transistor array reliability deterioration, environmental temperature rise, current distribution on-resistance cracking and cracking. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

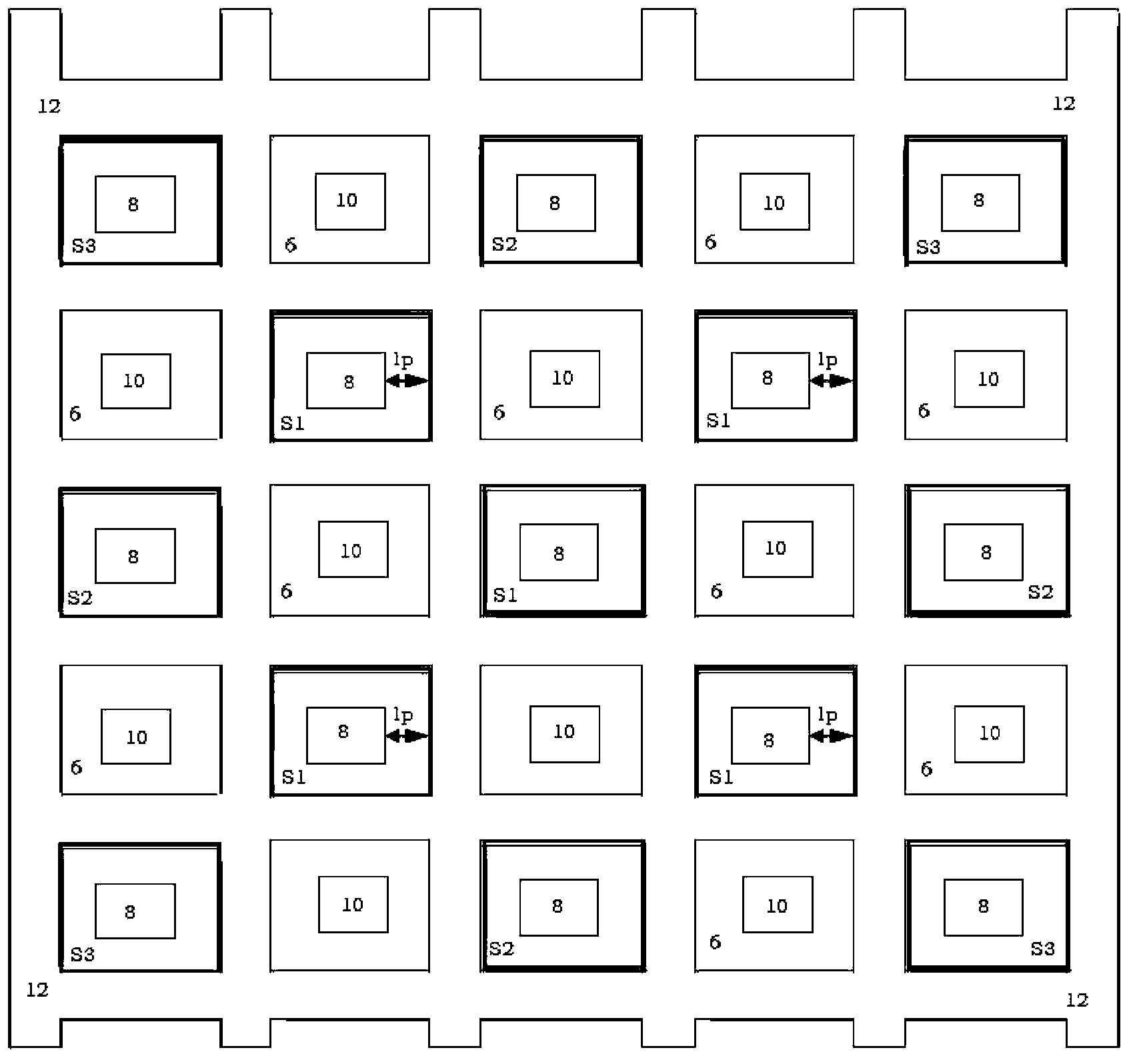

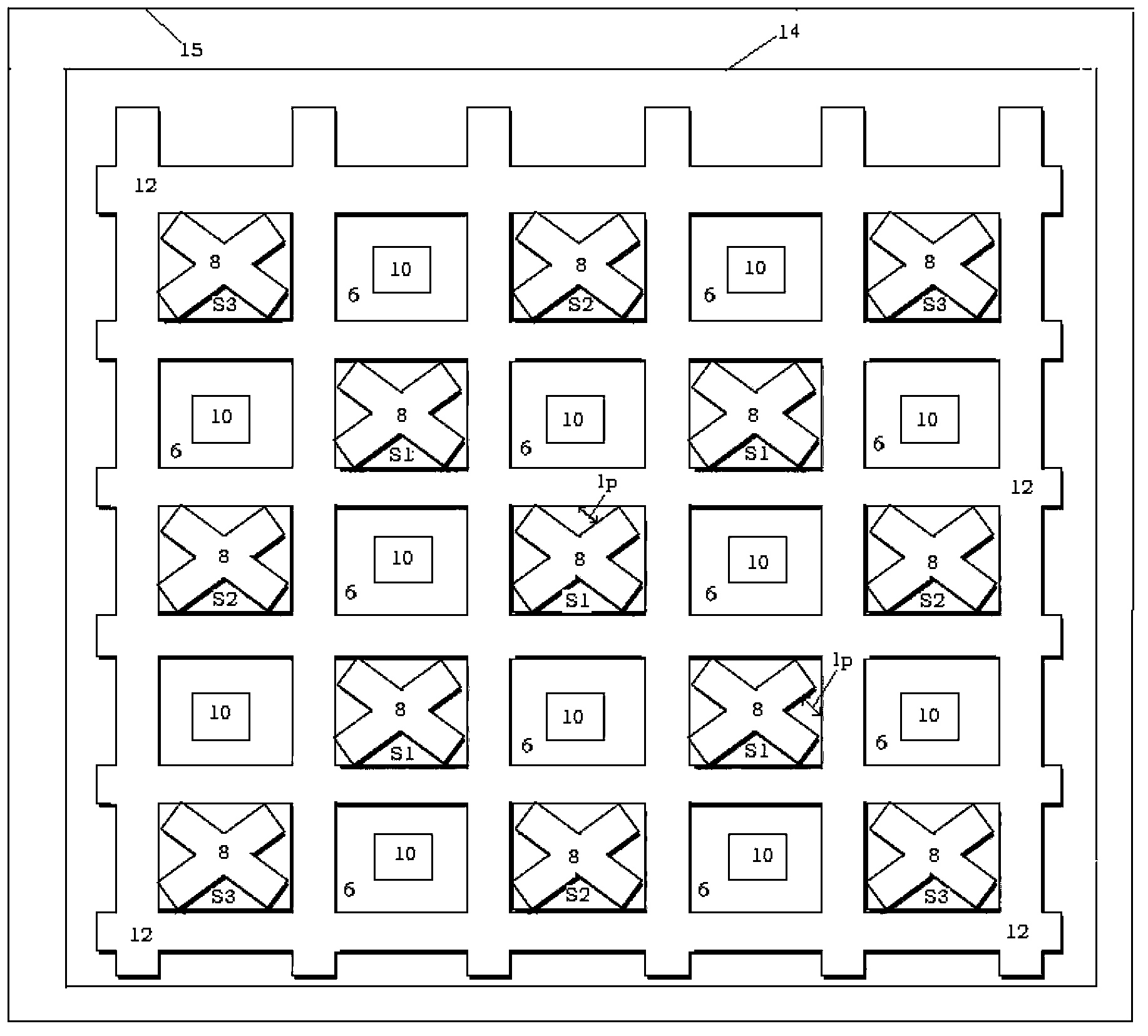

[0034] Such as figure 2 As shown, an embodiment of the LDMOS power transistor array structure of the present invention includes: a plurality of parallel-connected LDMOS transistors, and adjacent LDMOS transistors share a source or drain connection, wherein the sources and substrate terminals of all LDMOS transistors The drains are connected in parallel through metal lines, and the substrate terminal of each LDMOS transistor (i.e. image 3 The P-type heavily doped region 8) is arranged in an X-shaped cross manner, and there is a separate drain at the outermost periphery of the power transistor array to form a drain guard ring that is drawn out through metal lines, and an isolation ring is provided outside the drain guard ring .

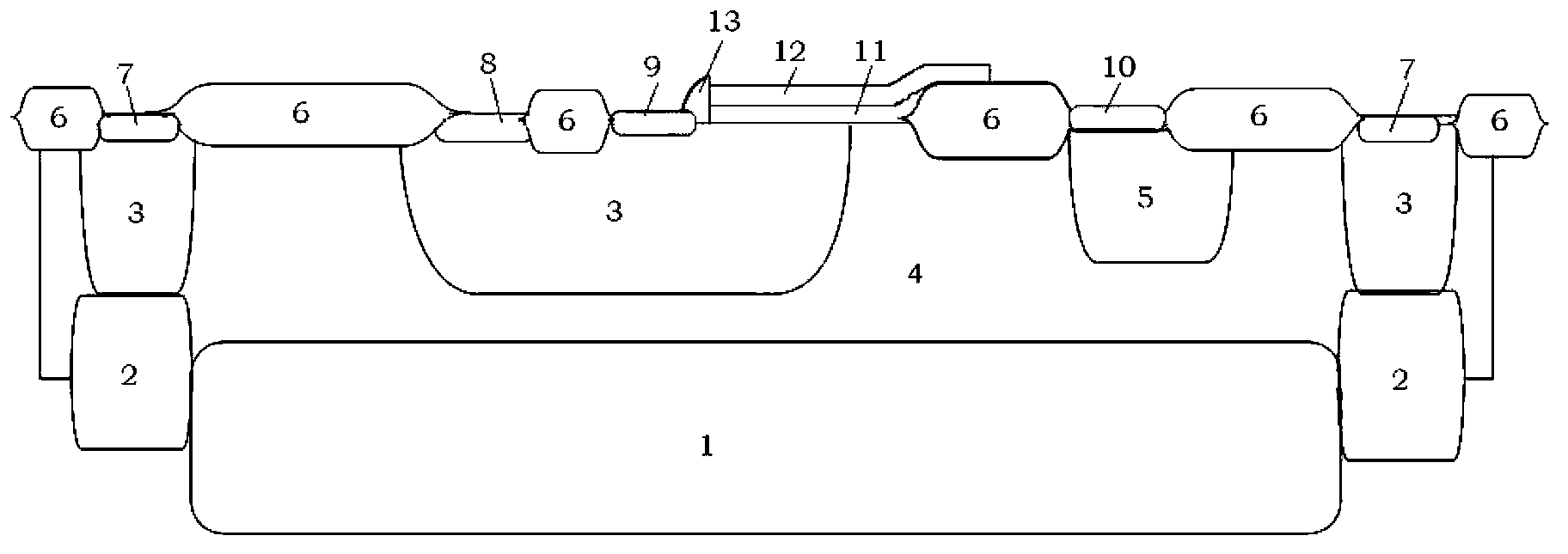

[0035] Such as image 3 As shown, each LDMOS transistor in this embodiment includes: an N-type epitaxial layer 1 formed on a P-type substrate, a P-type buried layer 2 and an N-type buried layer 4 formed on the N-type epitaxial layer 1, wherein The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More