A radio frequency chip interface circuit

A technology of interface circuit and radio frequency chip, which is applied to recording carriers used in machines, instruments, computer components, etc., can solve the problems of low data transmission rate and high power consumption, and achieve the effect of increasing data communication rate and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0008] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

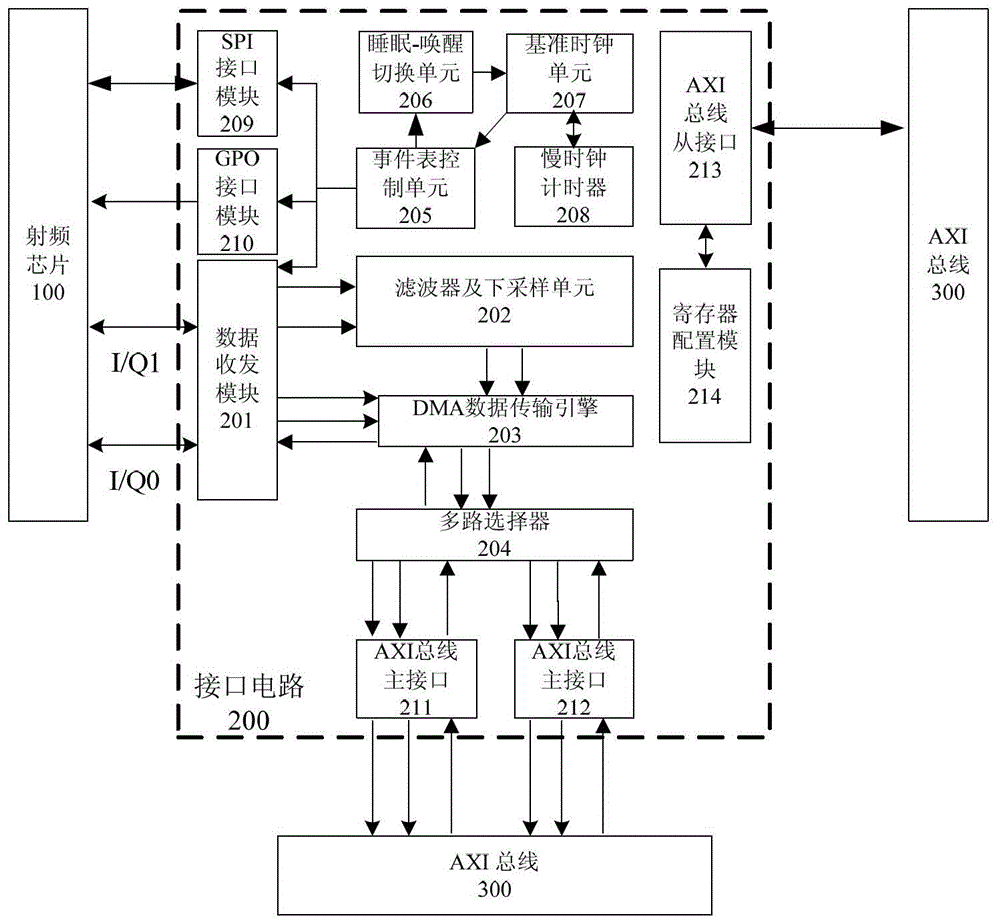

[0009] figure 1 It is a schematic structural diagram of a radio frequency chip interface circuit according to an embodiment of the present invention. Such as figure 1 As shown, the interface circuit 200 includes a data transceiving module 201, a DMA (DirectMemory Access, direct memory access) data transmission engine 203 connected with the data transceiving module 201, a multiplexer 204 connected with the DMA data transmission engine 203, and a multiplexer. AXI bus master interface 211 and AXI bus master interface 212 connected to road selector 204, event table control unit 205 connected with data transceiver module 201, sleep-wake switching unit 206 connected with event table control unit 205 and reference clock unit 207 , the slow clock timer 208 connected to the reference clock unit 207 , the AXI bus slave interfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More