Semiconductor device

A technology of semiconductor and size packaging, which is applied in the direction of semiconductor devices, circuit devices, semiconductor/solid-state device components, etc., can solve the problems of increased chip cost, increased chip area, chip layout design constraints, etc., and achieve the effect of improving ESD resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

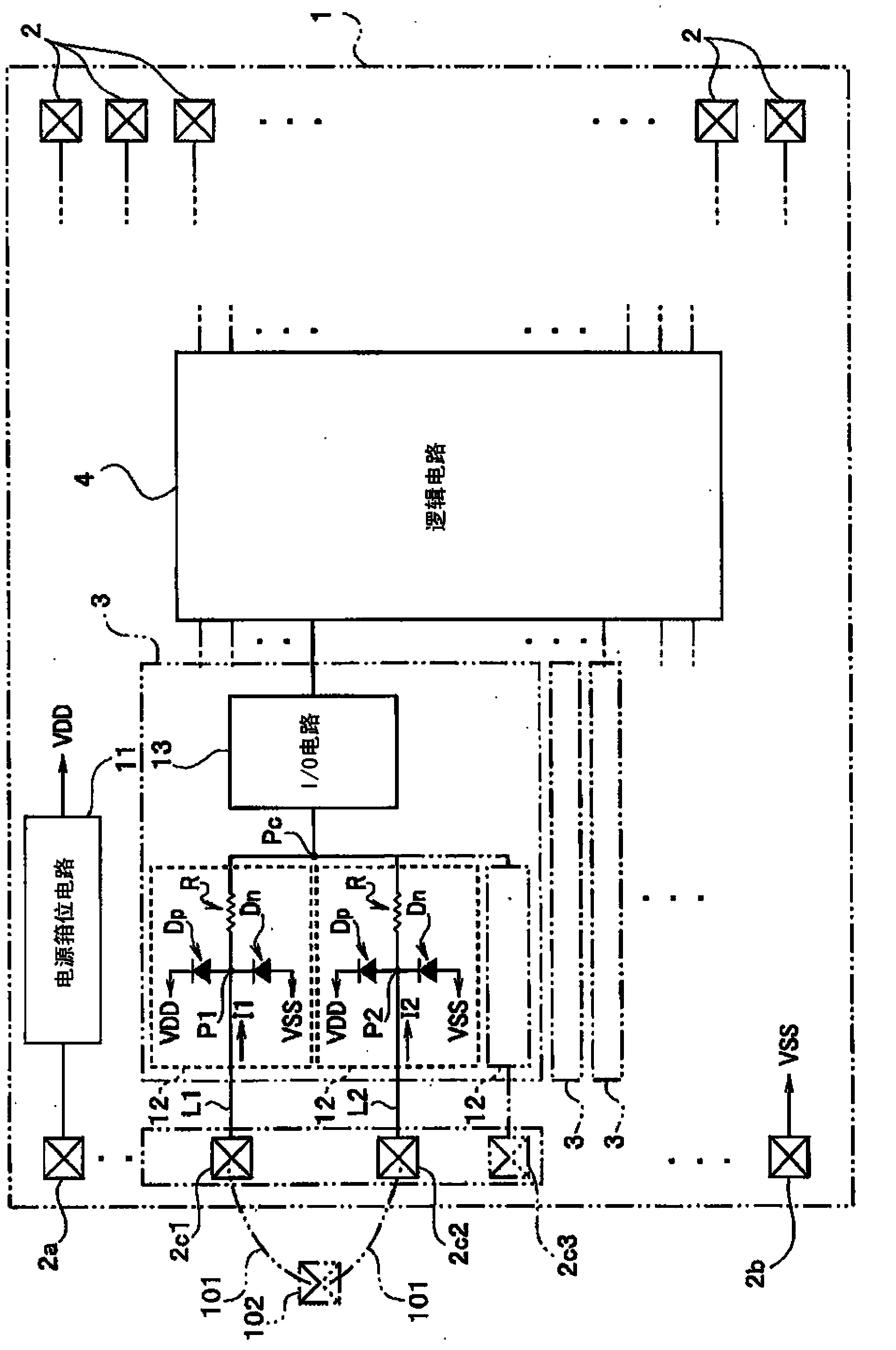

[0021] Embodiments will be described below with reference to the drawings.

[0022] (structure)

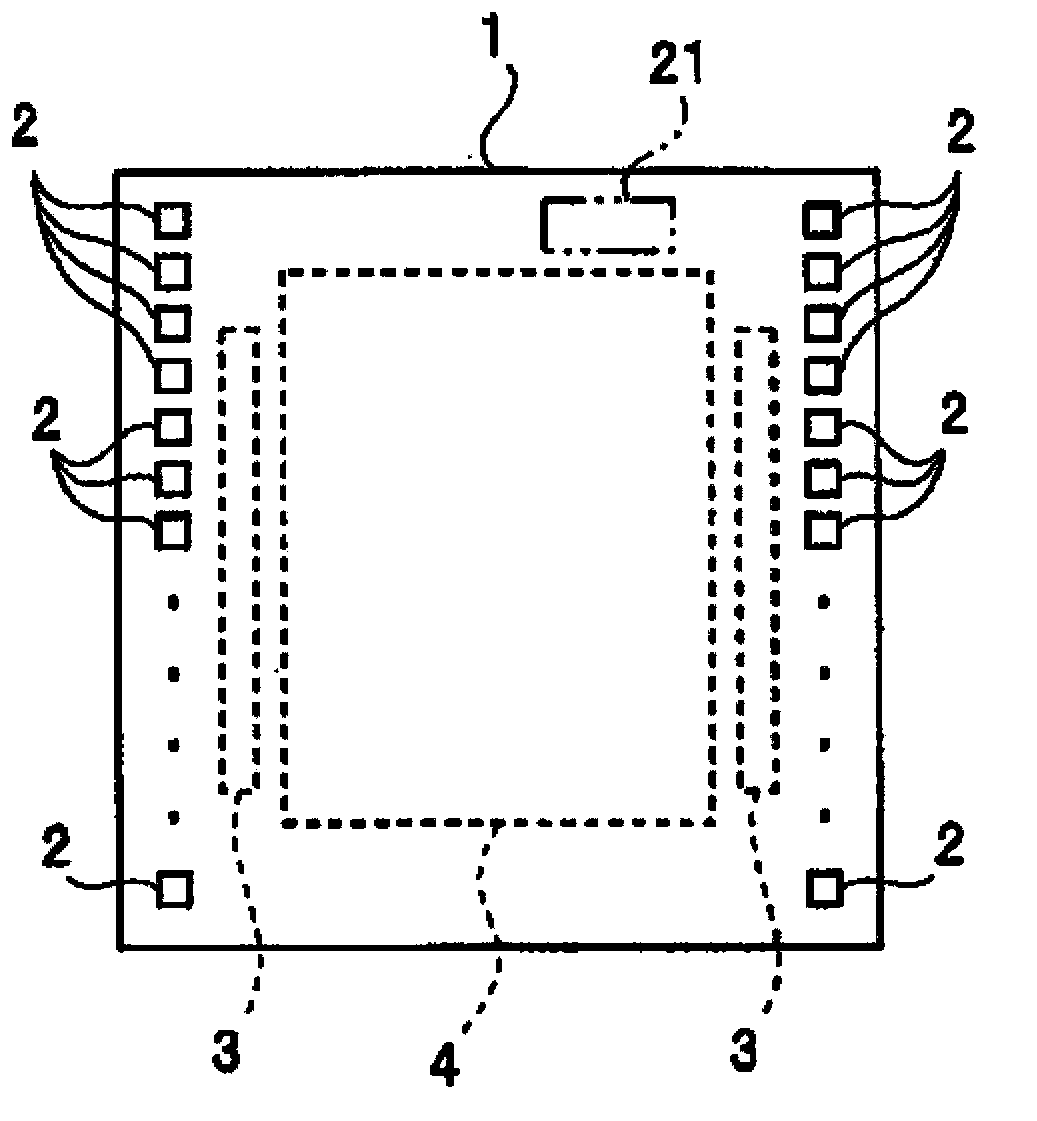

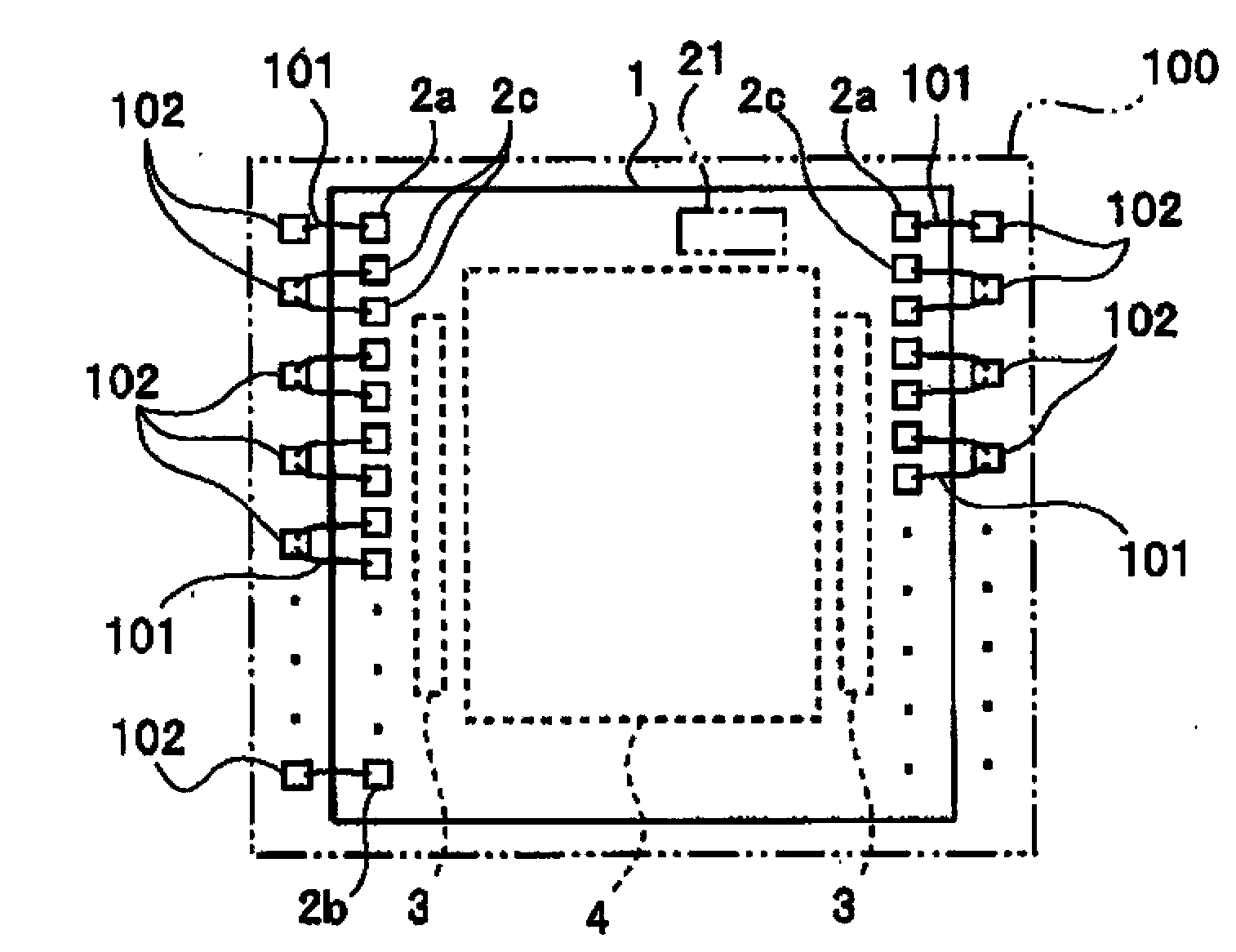

[0023] figure 1 It is a figure showing the concept of the chip layout of the semiconductor device of this embodiment. figure 2 It is a figure for explaining the state in which the semiconductor device of this embodiment is mounted on the semiconductor package.

[0024] In the semiconductor chip (hereinafter simply referred to as chip) 1 of this embodiment, if figure 1 As shown, in both peripheral portions of a rectangular chip, for example, a plurality of pads 2 for connecting bonding wires are arranged linearly along both sides of the chip 1 .

[0025] In addition, here, the plurality of bonding pads 2 are arranged in a linear shape at the peripheral portions of both sides of the chip 1 having a rectangular shape, but the plurality of bonding pads 2 may also be arranged at the peripheral portions of the four sides, or not only at the peripheral portions. .

[0026] Some pad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More