A method and system for improving dynamic redundant multithreading performance and reducing power consumption overhead

A dynamic redundancy and multi-threading technology, the redundancy applied in the operation is used for data error detection, response error generation, etc., which can solve performance and power consumption overhead, overestimate AVF, and overestimate the effective occupation of processor components. rate and other issues, to achieve the effect of reducing performance and power consumption overhead, reducing running time, and improving prediction accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to make the object, technical solution and advantages of the present invention clearer, the implementation of the present invention will be further described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

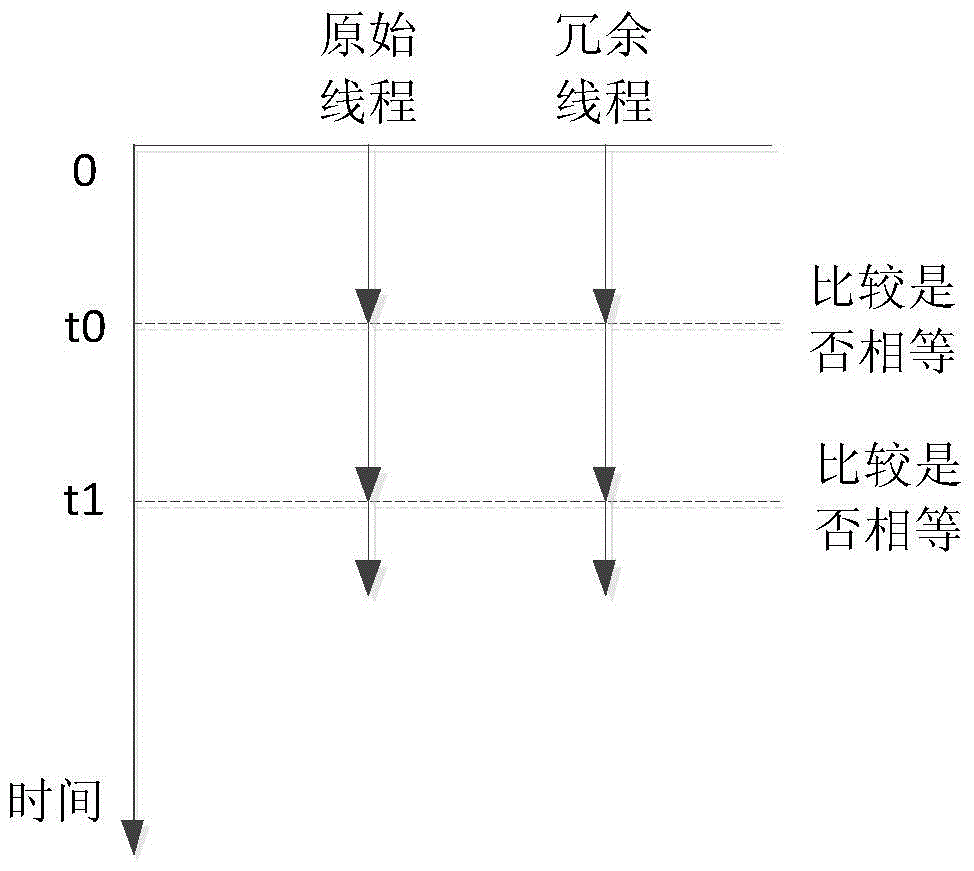

[0014] In order to alleviate the soft error problem, the industry often uses redundancy technology, especially redundant multi-threading technology. Use SMT hardware resources or multi-core processors to run two identical threads at the same time. Only when the outputs of the two threads are equal, the program can continue to execute, such as figure 2 shown.

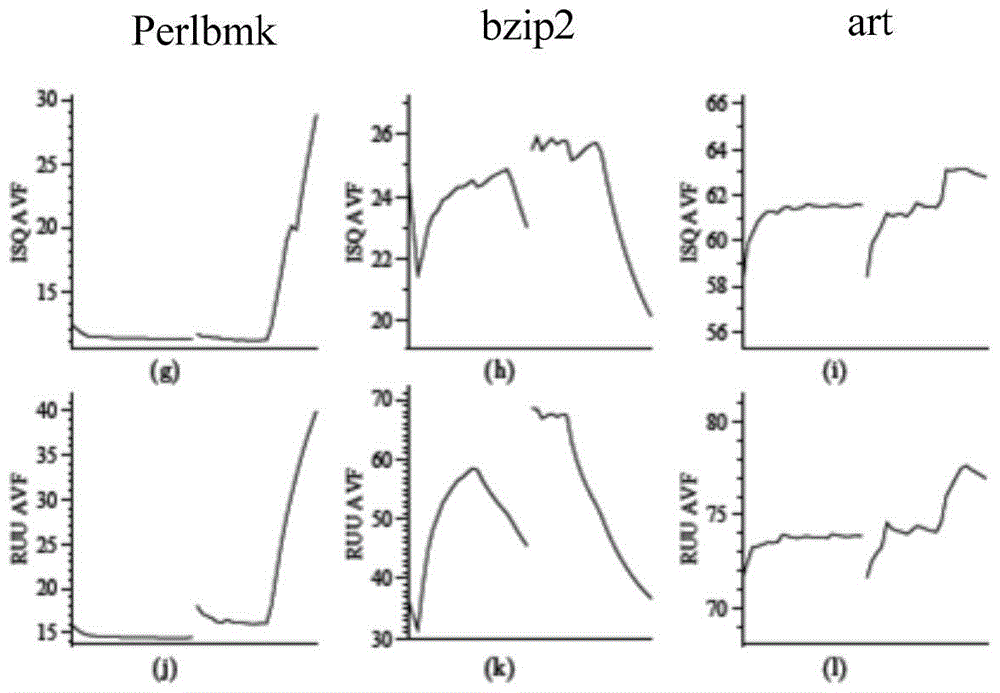

[0015] During the entire process of program running, redundant threads are always detecting soft errors, ensuring that all soft errors will be detected. But in fact, it is not necessary to use such high-cost detection measures in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More