Array substrate, preparation method thereof and display device

A technology for array substrates and display devices, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, diodes, etc., can solve the problems of complex structure, reduce the production yield of array substrates, and difficult to prepare high array substrates, so as to ensure production safety and The effect of production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

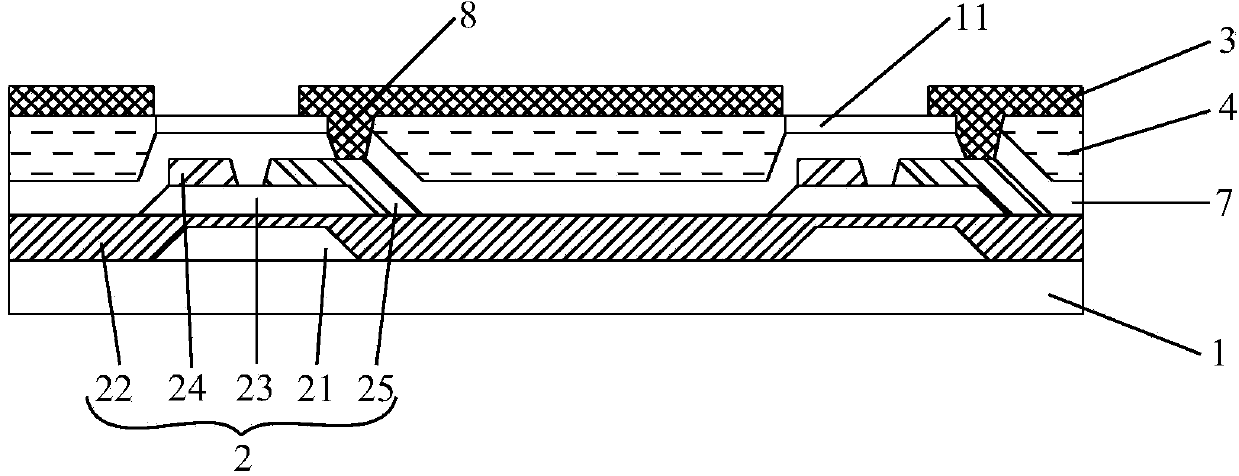

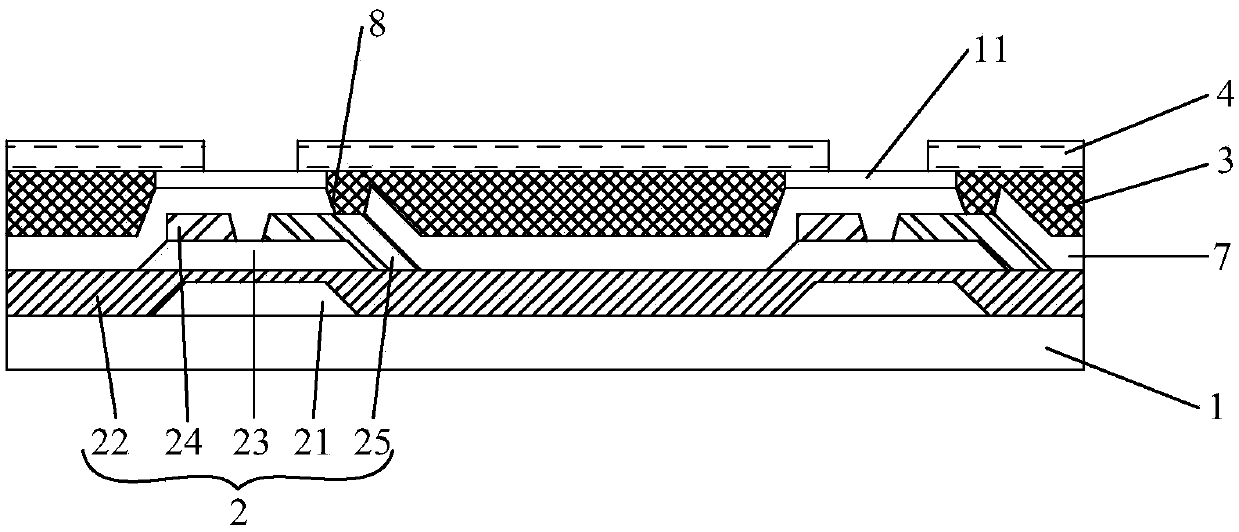

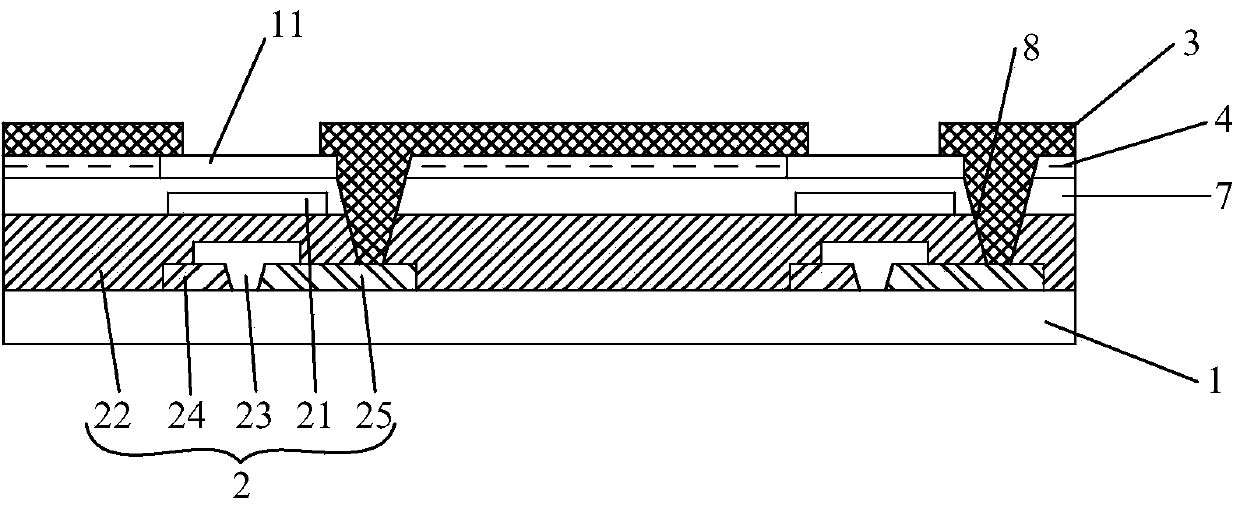

[0058] An embodiment of the present invention provides an array substrate, such as figure 1As shown, it includes a base substrate 1, a thin film transistor unit 2 located on the base substrate 1, a color filter 4 and a flat protective layer 3, and the flat protective layer 3 is connected to the drain 25 of the thin film transistor unit 2 electrical connection, wherein the flat protective layer 3 is conductive.

[0059] Wherein, the flat protective layer 3 formed on the array substrate is usually formed by a resin with a certain viscosity, which can flatten the uneven structure on the array substrate, and protect the structure under the flat protective layer 3 from being damaged. Corrosion, to ensure that the subsequent manufacturing process of the array substrate can be carried out smoothly.

[0060] But in the embodiment of the present invention, the flat protective layer 3 can also conduct electricity, so that the flat protective layer 3 can not only play the role of flat p...

Embodiment 2

[0106] The embodiment of the present invention provides a method for preparing the array substrate described in Embodiment 1, such as Figure 10 Shown, this preparation method comprises:

[0107] Step S101 , forming a pattern including a drain of a thin film transistor unit, a color filter and a flat protection layer electrically connected to the drain of the thin film transistor unit.

[0108] Thus, it is possible to form Figure 1-Figure 7 The shown flat protective layer 3 is electrically connected to the array substrate with the drain electrode 25 . Specifically, it can be known from Embodiment 1 that the array substrate provided by the embodiment of the present invention is at least as Figure 1-7 In the seven structures shown, that is, the drain 25 of the thin film transistor unit 2 can be either above the flat protective layer 3 or below the flat protective layer 3, and the thin film transistor unit 2 can be a bottom gate type Also available as top gate type.

[0109...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More