Power failure detection circuit based on field programmable gate array (FPGA) network management system and detection method

A power-down detection and network management system technology, applied in the field of communication, can solve problems such as failure to recognize power-down of client devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

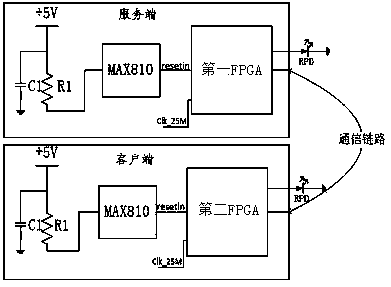

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0024] The present invention adopts CLK_50M as the input of the system clock at both the server end and the client end, connects the 50M crystal oscillator, and outputs CLK_25M in the FPGA to provide the clock for the Ethernet chip. The first detection circuit and the second detection circuit are connected through optical fibers, and the interface is PMII interface. RESET is the FPGA system reset input pin, used for system reset. RESET8051 and RESET8995 are the output pins for the FPGA to control the reset of the external microcontroller and Ethernet chip. Their function is to ensure that all chips are in the initial state when the power is turned on, and other chips start to work after the FPGA works normally. CPLD_RUN is an indication that the system is running normally. When it is working normally, it outputs a square wave and an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More