Method for testing pins of integrated circuit

A test method and integrated circuit technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of high test cost, high test machine purchase cost, low efficiency, etc., and achieve the goal of shortening test time and test cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

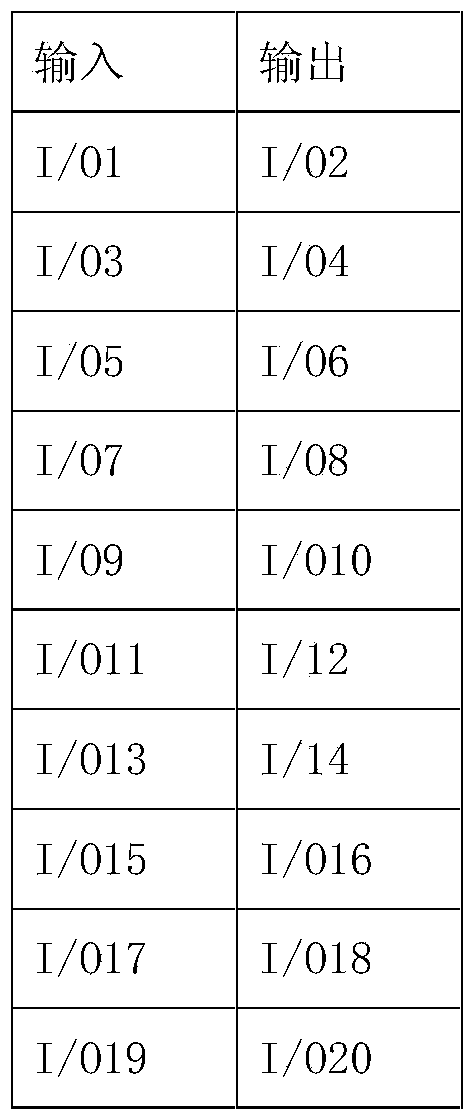

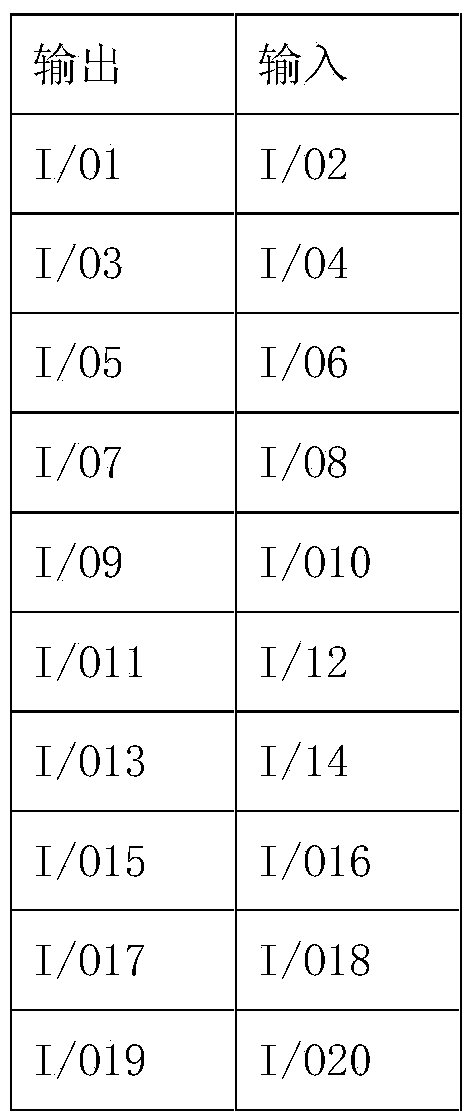

[0016] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements. As mentioned above, the present invention provides a method for testing integrated circuit pins. The method divides the pins of the integrated circuit into two groups. The two test modes of IOMODE1 test mode and IOMODE2 test mode only need to test the two groups of pins respectively. The test can be completed by performing two tests, which greatly reduces the test time and cost.

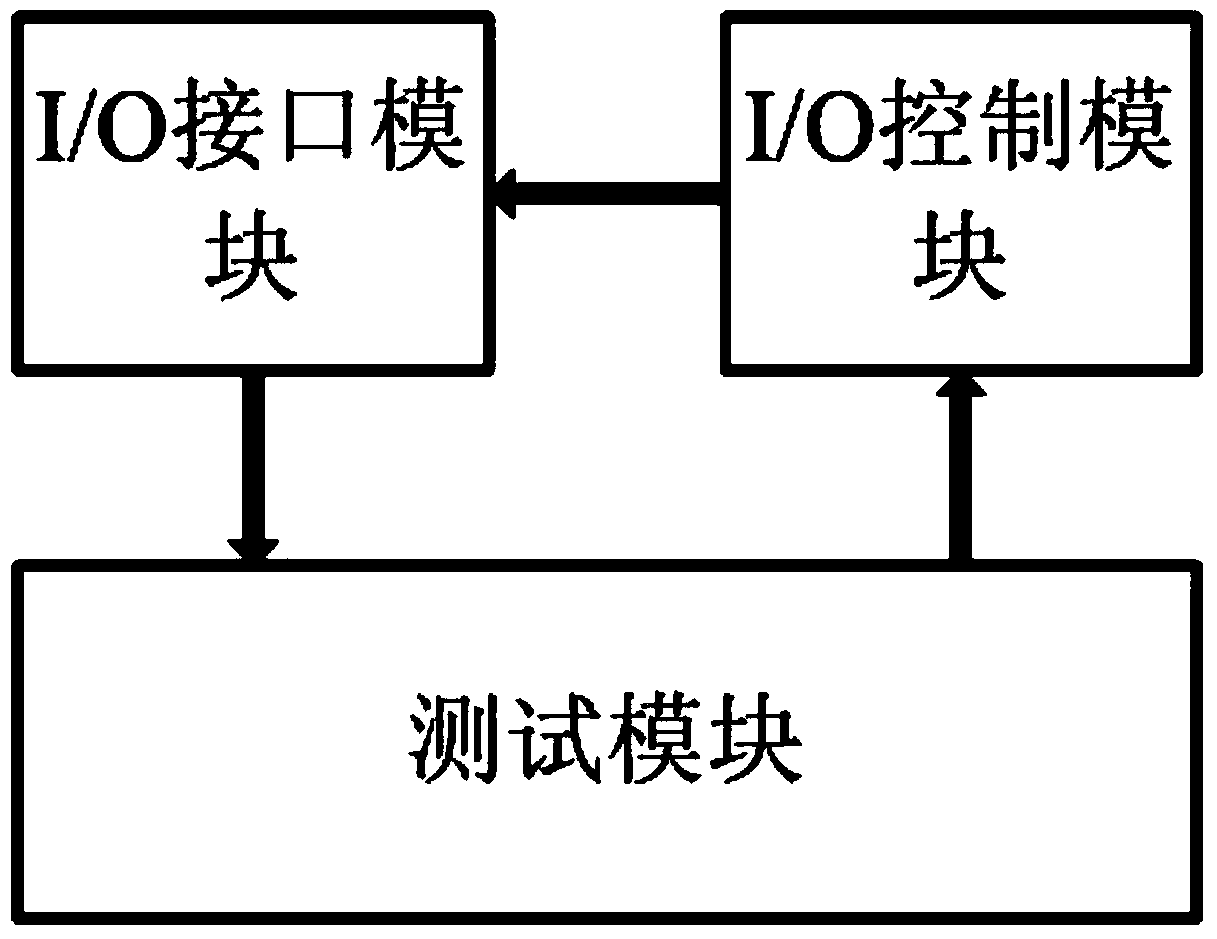

[0017] Please refer to figure 1 , figure 1 It is a structural block diagram of a method for testing integrated circuit pins in the present invention. As shown in the figure, a test method for integrated circuit pins of the present invention includes a test module, an I / O (digital-to-analog conversion) interface module and an I / O control module, and the test module is preset to have 20 pins In the chip to be tested and matched with the I / O inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com