Multicore-oriented reconfigurable fault tolerance system and multicore-oriented reconfigurable fault tolerance method

A fault-tolerant system and multi-core technology, applied in the direction of response errors, etc., can solve the problems of complex system design verification, backwardness, lack of guidance methods and verification methods, etc., to achieve clear division of labor, ensure reliability, and improve system reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

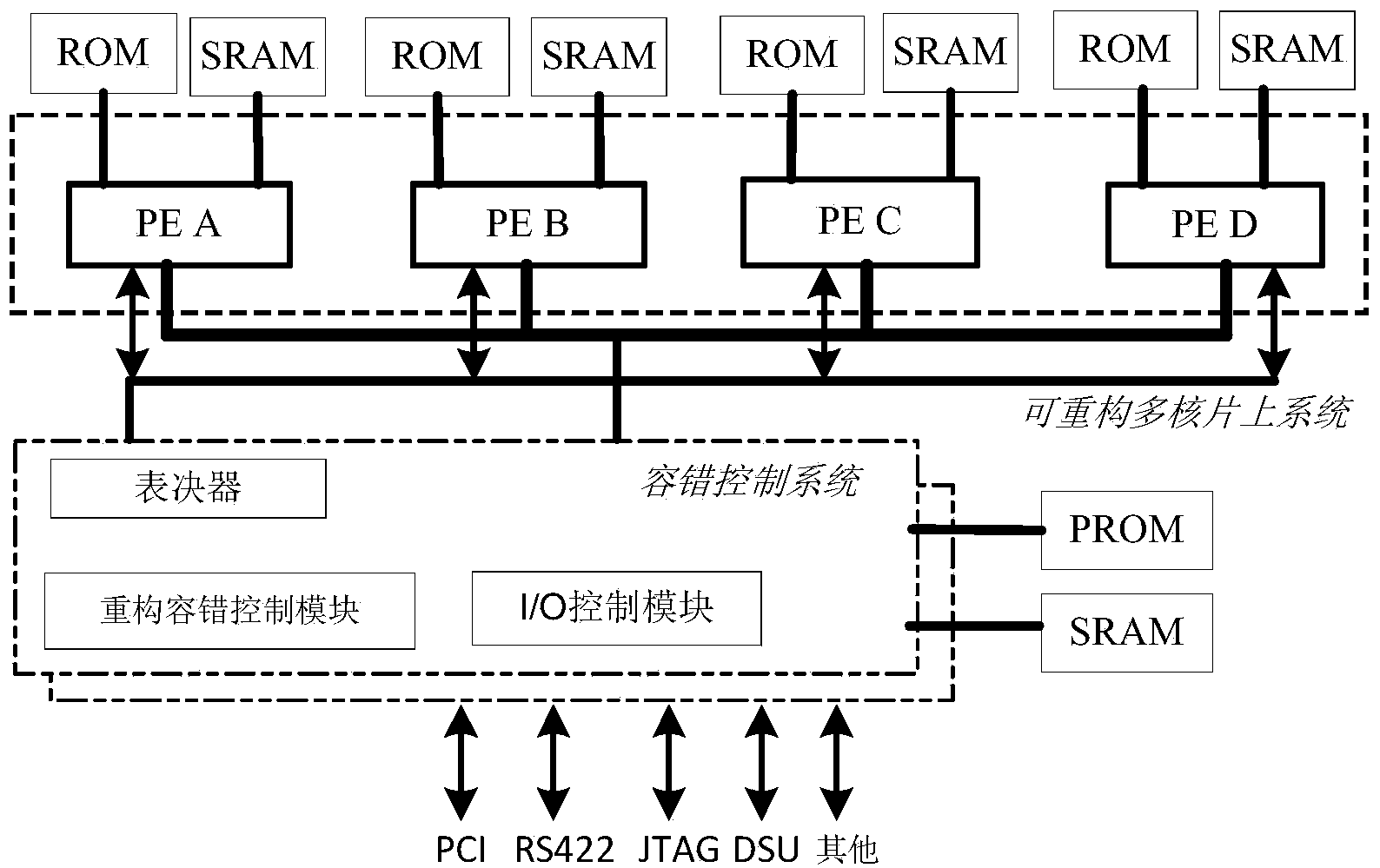

[0040] Such as figure 1 As shown, the multi-core in the multi-core reconfigurable fault-tolerant system of the present invention mainly refers to having four processor units, specifically including: four processor units, a fault-tolerant control system and a storage unit; The reconfigurable SRAM type FPGA implements, and the reconfigurable fault-tolerant control module adopts off-chip ASIC or antifuse FPGA to realize, and provides independent storage units for the four processor units and the reconfigurable fault-tolerant control module.

[0041] The specific implementation is as follows:

[0042] 1. Processor unit (PE, Processor Element)

[0043] The processor unit is the main execution unit for system task processing. The specific internal functional structure design of the processor unit in the present invention can be designed and modified according to the system function requirements, and has good tailorability.

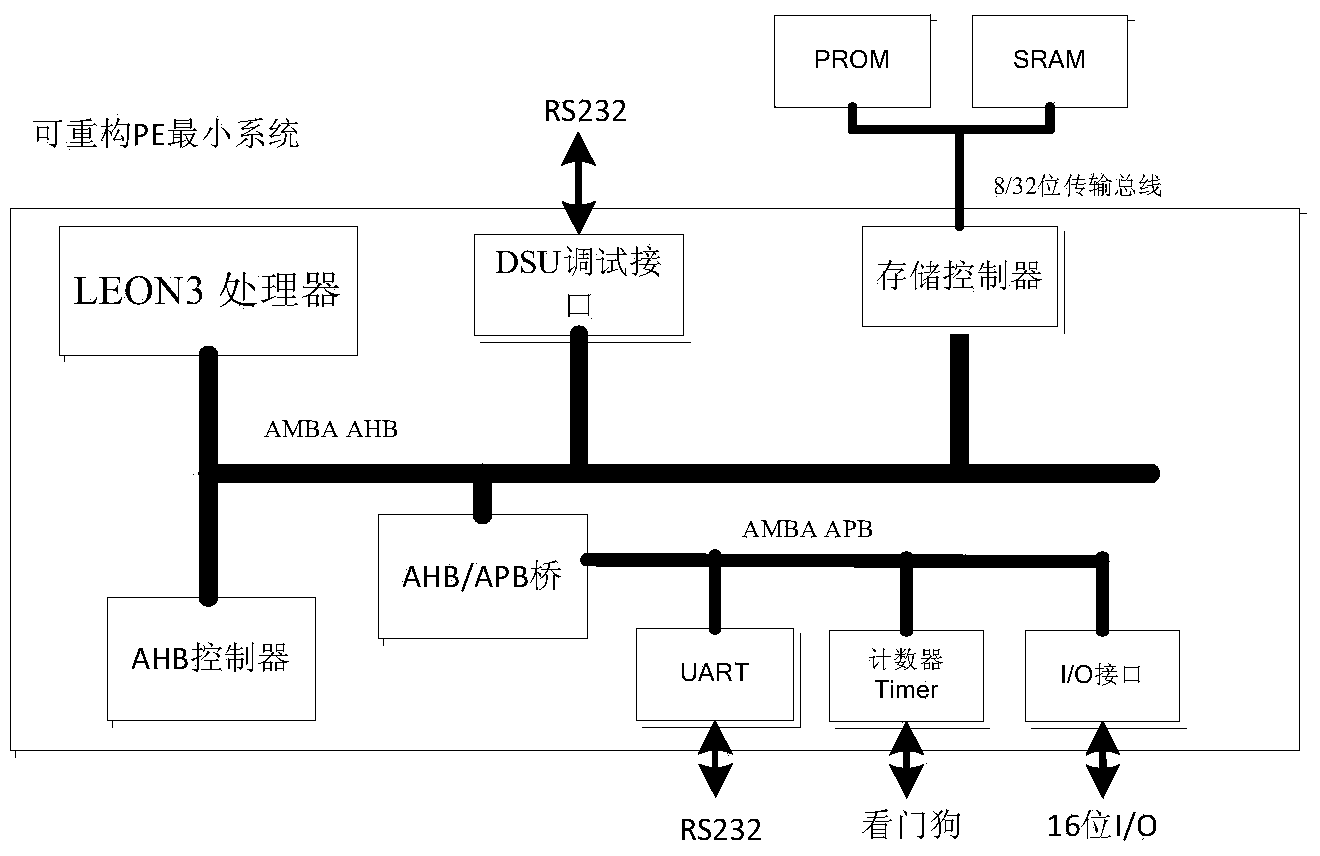

[0044] The present invention realizes and adopts the LE...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More