Method and system for replacing through holes in memory cell array layout data

A storage cell array, storage cell technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as time-consuming, large number of through holes, loss of through holes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

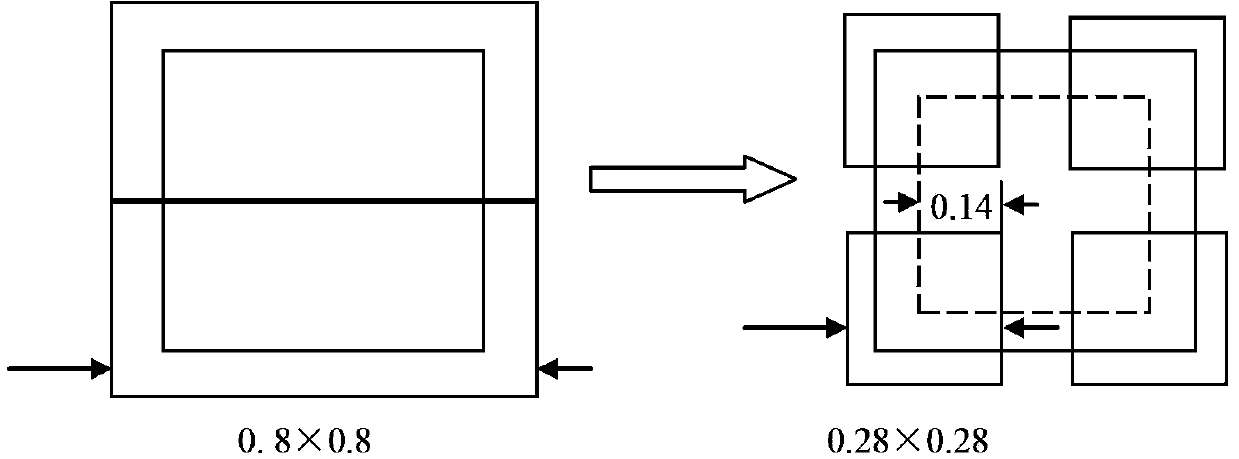

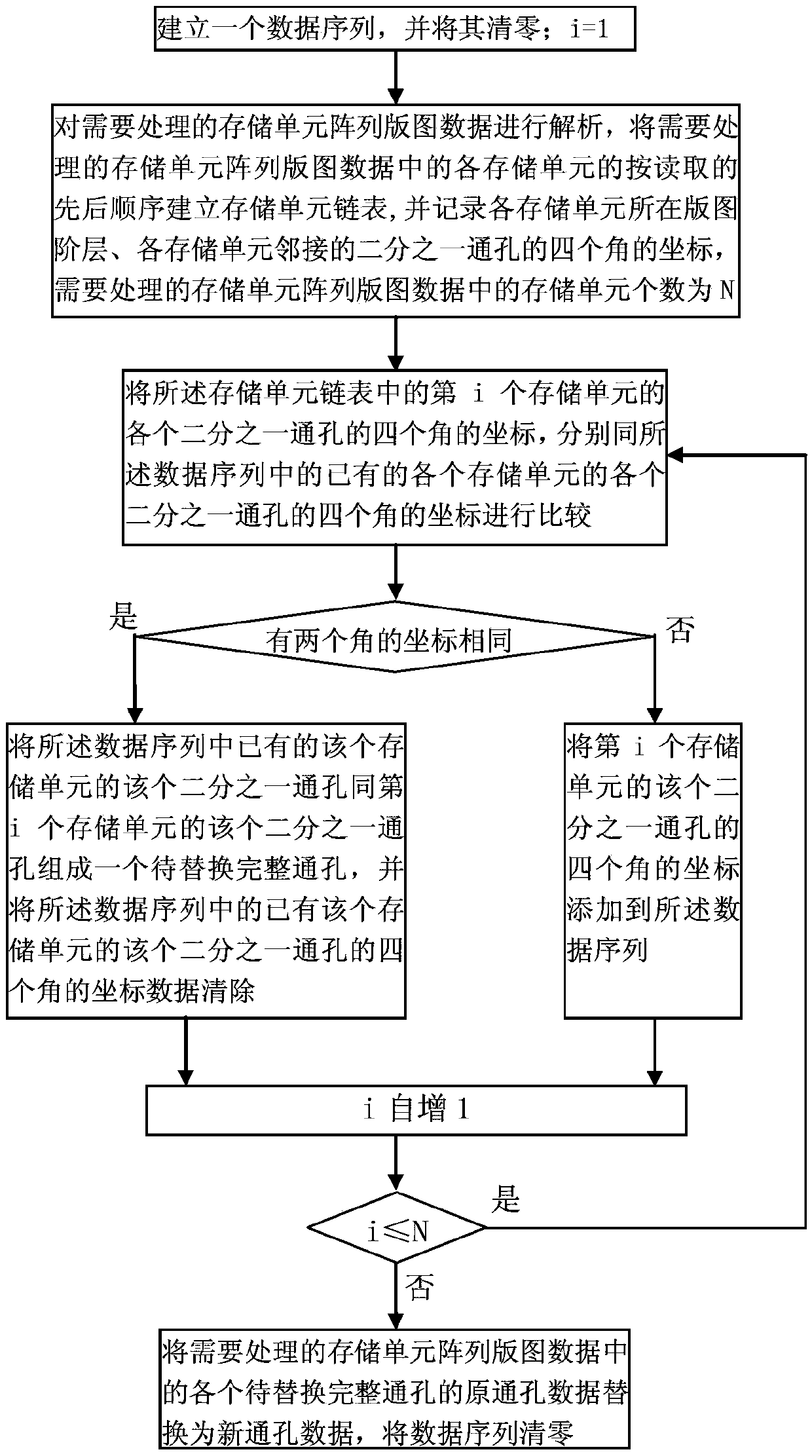

[0028] The method for replacing the through holes in the memory cell array layout data comprises the following steps:

[0029] 1. Create a data sequence and clear it; i=1

[0030] 2. Analyze the layout data of the memory cell array that needs to be processed, establish a linked list of storage cells according to the order of reading for each memory cell in the layout data of the memory cell array that needs to be processed, and record the layout level of each memory cell, each The coordinates of the four corners of the 1 / 2 through hole adjacent to the memory cell, the number of memory cells in the layout data of the memory cell array to be processed is N;

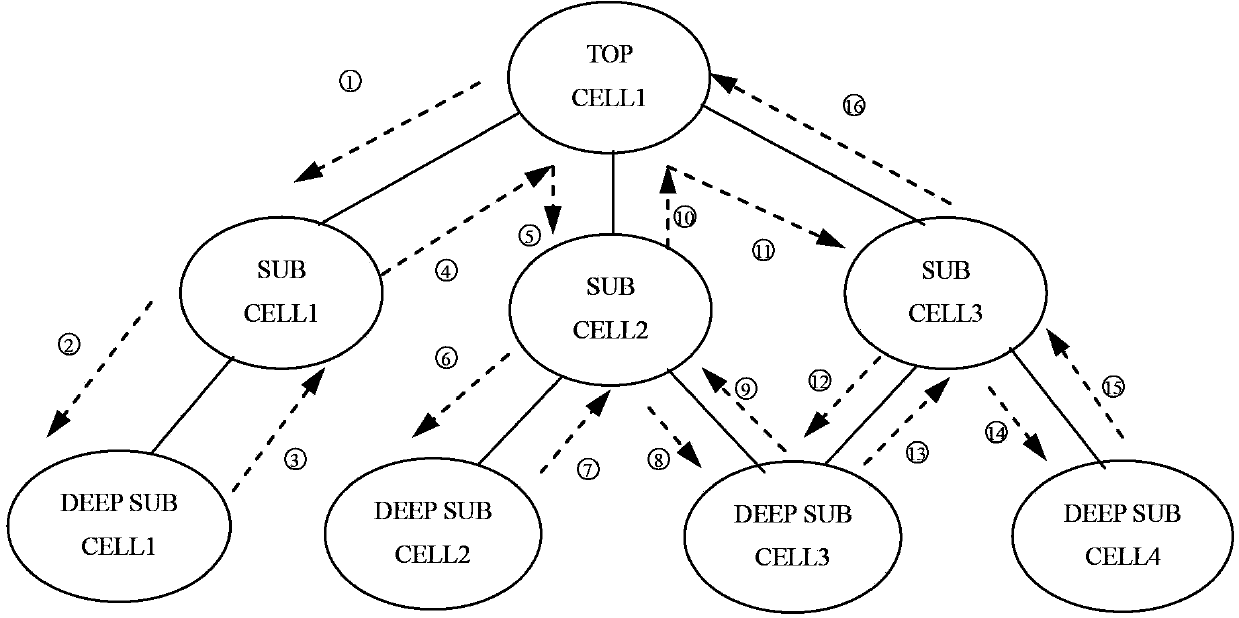

[0031] A memory cell linked list of memory cell array layout data such as figure 2 As shown, in the storage unit linked list of the tree structure, each storage unit is distributed in three layout levels: the first layout level (TOP), the second layout level (SUB), and the third layout level (DEEPSUB); each storage unit (...

Embodiment 2

[0036] A replacement system for vias in memory cell array layout data, such as Figure 4 As shown, it includes a memory cell array layout data analysis module, a data sequence module, a matching processing module, and a complete through-hole replacement module;

[0037]The storage cell array layout data analysis module is used to analyze the storage cell array layout data that needs to be processed, and establish a storage cell linked list for each storage cell in the storage cell array layout data that needs to be processed according to the order of reading, and Record the coordinates of the four corners of each half of the through holes adjacent to each memory cell, and record the number of memory cells in the layout data of the memory cell array to be processed;

[0038] The data sequence module is used to store data sequences, and the initial state is cleared;

[0039] The matching processing module works as follows:

[0040] a.i = 1;

[0041] 2. The coordinates of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More