Combinational logic circuit capable of maintaining duty ratio

A combination logic circuit and duty cycle technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve disadvantages and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

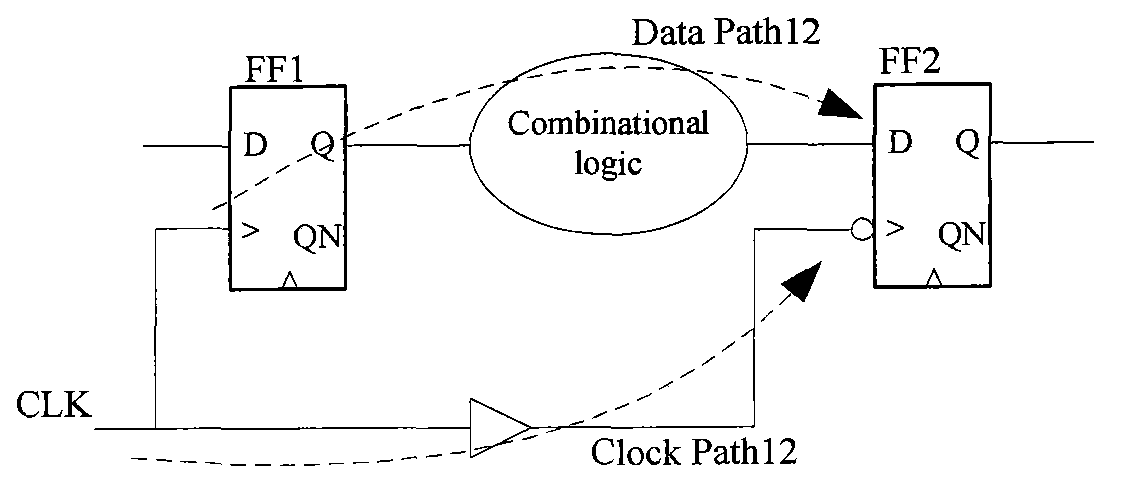

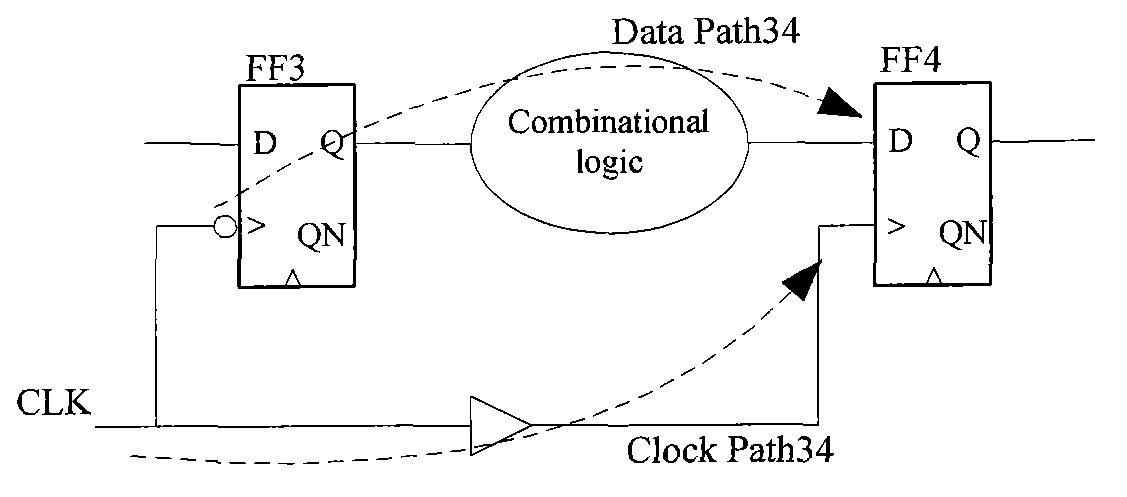

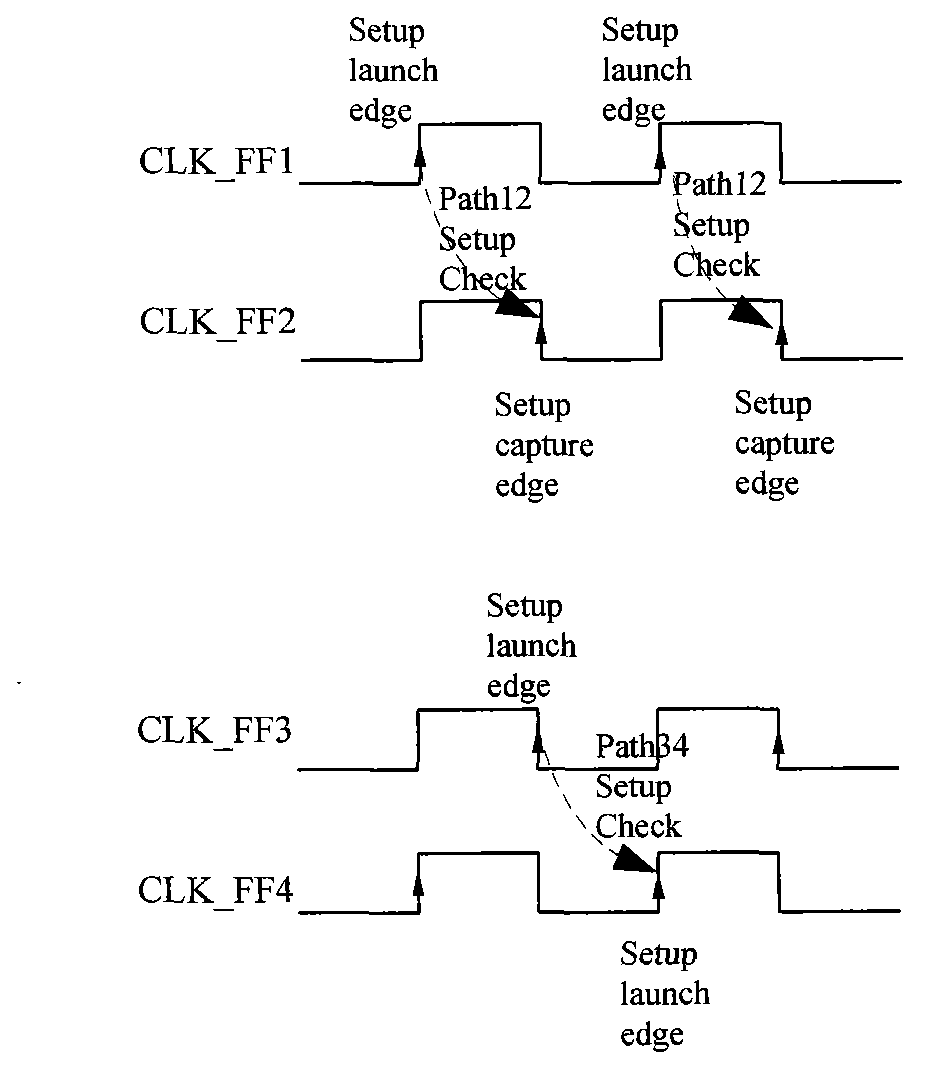

[0021] Due to the asymmetry of the rising edge and falling edge delay of the combinational logic device in the process library, the clock signal passes through Figure 4 The rising edge delay and the falling edge delay after the combination of the clock network shown in the logic device are not equal, which will cause the duty cycle of the trigger clock to deteriorate, which is not conducive to the timing convergence of the half-cycle path setup.

[0022] If the required logic provides the same logic cell with inverted output in the standard cell library, keep the duty cycle logic implementation structured as Figure 5 shown. Figure 5 Indicates that two identical outputs are inversely connected in series, such as Figure 8 , Figure 9 , to realize the AND or OR logic that maintains the duty cycle, then connect two NAND gates or NOR gates with the same driving capability in series. Its principle of maintaining the duty cycle is as Figure 7 As shown, the rising edge delay ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com