Display Device And Inspection Method Thereof

A display device and display area technology, applied in static indicators, instruments, etc., can solve the problems that the size of the semiconductor chip mounting area cannot be reduced, and the wiring disconnection inspection cannot be drawn out, and the effect of reducing the size can be achieved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

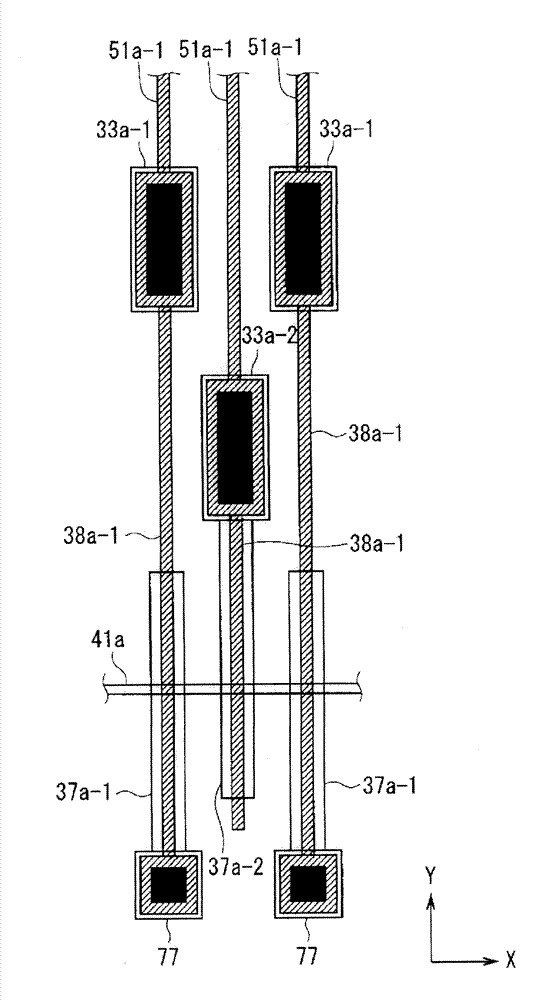

[0022] figure 1 It is a circuit diagram showing the configuration of the display device (display panel) according to Embodiment 1 of the present invention. also, figure 1 The reference numerals of the constituent elements of the display device according to the first embodiment are also assigned to the same or similar constituent elements in the display devices of the other embodiments.

[0023] Such as figure 1 As shown, the display device according to Embodiment 1 includes a substrate 1 provided with a display region 11 and a semiconductor chip mounting region (here, the first and second semiconductor chip mounting regions 31a and 31b) shown by dotted lines, and the two-dot-dashed The gate drive circuit 32a and the source drive circuit 32b shown by the line are configured.

[0024] In the display area 11, a plurality of semiconductor switching elements (here, a plurality of display TFTs (Thin Film Transistor) 12) arranged in a matrix, and a plurality of gate signal lines c...

Embodiment approach 2

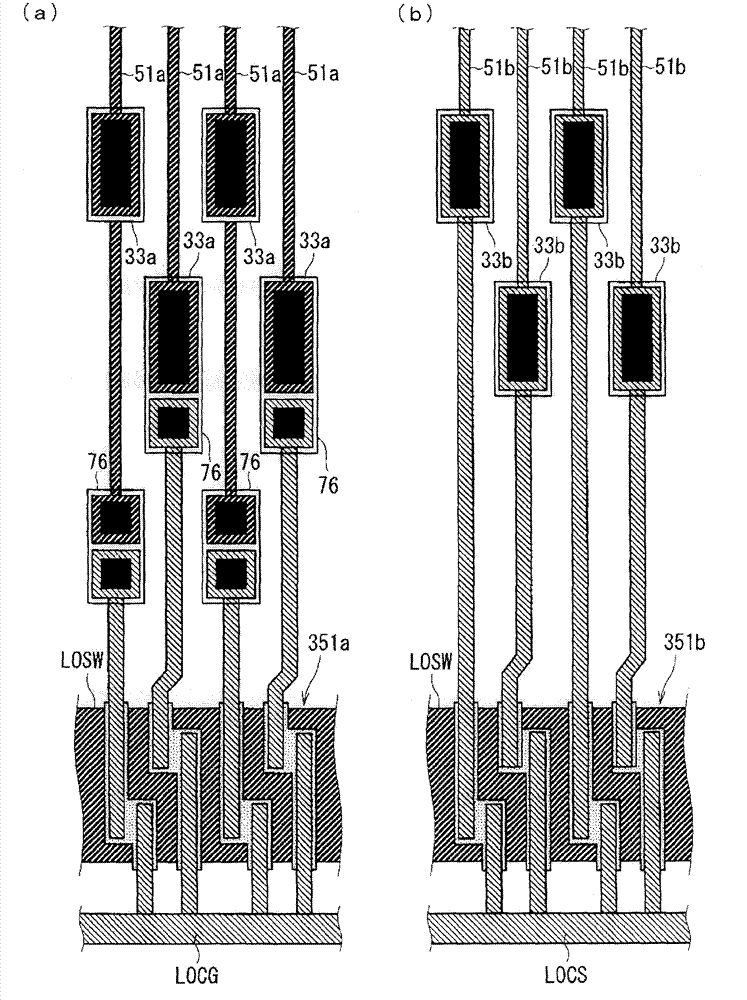

[0075] Embodiment 2 of the present invention is a modified example of the basic configuration of Embodiment 1 described above.

[0076] As mentioned above, in the lead-out wiring breakage inspection, attention is paid to whether there is a bright line (normally white) that crosses from one end of the display area 11 to the other end, not whether there is a bright line in the pixel display of the display area 11. Uneven display. That is, in the first and second lead wire disconnection inspection circuits 35a and 35b, it is not necessary to pay attention to unevenness in the display panel surface due to resistance distribution.

[0077] Therefore, in the second embodiment, the wiring width of the inspection signal lines LOCG and LOCS is reduced. Specifically, the wiring width of the inspection signal line LOCG serving as the first lead wire disconnection inspection signal line is configured to be smaller than the wiring width of the inspection signal lines LTGO and LTGE serving...

Embodiment approach 3

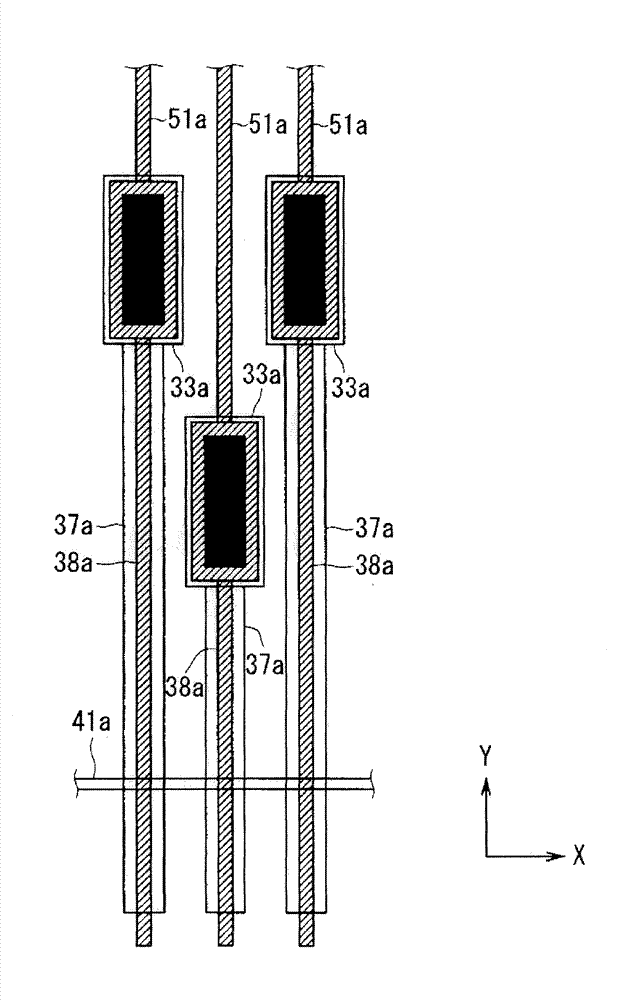

[0083] Embodiment 3 of the present invention is a modified example of the basic configuration of Embodiment 1 or 2 described above. Figure 4 It is a circuit diagram showing the configuration of a display device (display panel) according to the third embodiment. Such as Figure 4 As shown, in Embodiment 3, the terminals 36a and 36b for cut-off voltage are provided in the first semiconductor chip mounting region 31a.

[0084] The cut-off voltage terminal 36a is connected to the above-mentioned inspection signal line LTSW, and can apply a common gate potential to the plurality of first and second inspection TFTs 611a and 611b via the inspection signal line LTSW.

[0085] The off-voltage terminal 36b is connected to the inspection signal line LOSW of the first semiconductor chip mounting region 31a via the terminal OSW, and can apply a common gate potential to a plurality of first lead-out wiring disconnection inspection TFTs 351a via the inspection signal line LOSW. . In addi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More