Measuring method for capacity parameters of each chip on silicon chip

A measurement method and technology of silicon wafers, applied in the direction of measuring devices, measuring electrical variables, measuring resistance/reactance/impedance, etc., to achieve the effects of less equipment investment, improved test efficiency, and reduced test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

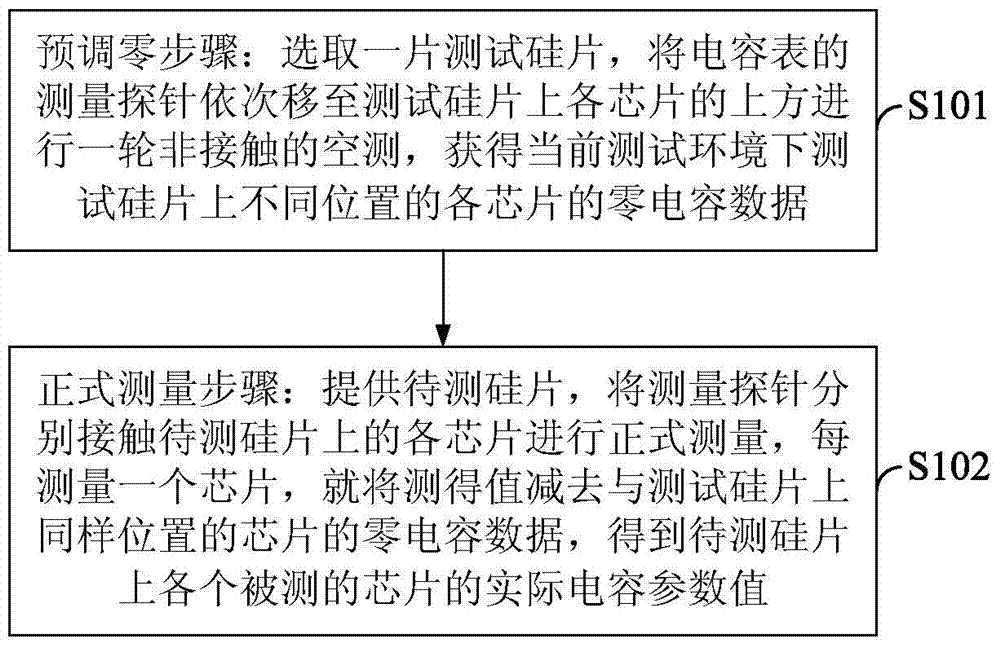

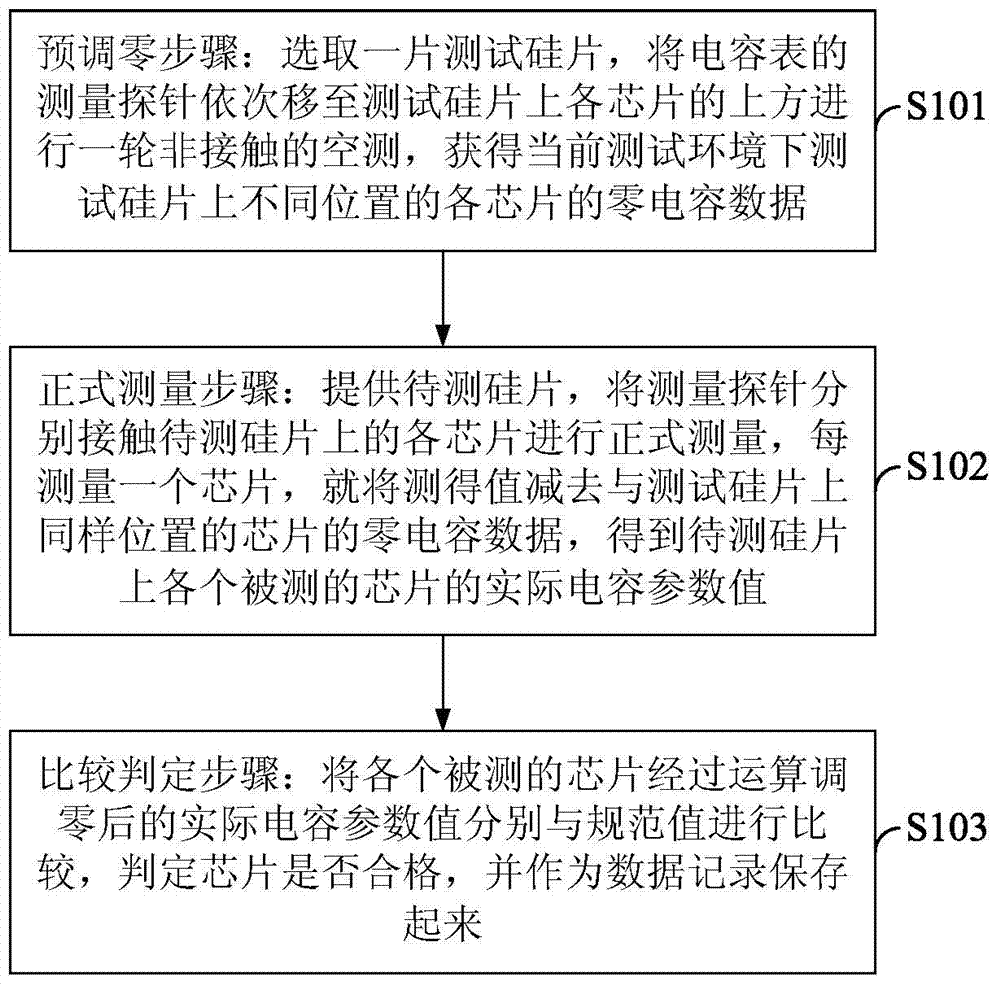

[0022] The idea of the invention is: if the capacitance parameter is to be accurately measured, the capacitance meter must be zeroed before the measurement. The method of zero adjustment is that when the measuring probe is at a very close distance above the chip under test but has not yet touched the capacitance electrode, first perform a blank measurement to obtain a capacitance parameter value, and the capacitance meter stores this value as a calibration value. Then the measurement probe touches the chip under test for formal measurement, and the measured value minus the calibration value obtained by the empty test is the actual capacitance parameter value of the chip under test.

[0023] According to this train of thought, the present invention has developed a kind of " pre-zeroing " method. That is, before the formal production and measurement of silicon wafers, first take a test silicon wafer for a round of non-contact air testing, and then you can get the zero-capacita...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Capacitance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com