Integrated passive device fan-out wafer level packaging structure and manufacturing method

A technology for integrating passive devices and wafer-level packaging, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of occupying product assembly costs, shorten the length of electrical connections, and improve the quality factor Q Value, improve the effect of electrical quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with specific drawings.

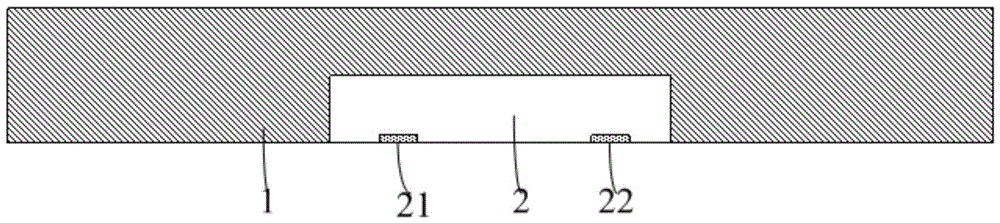

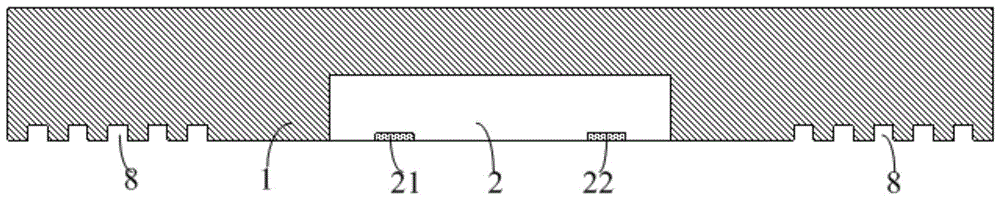

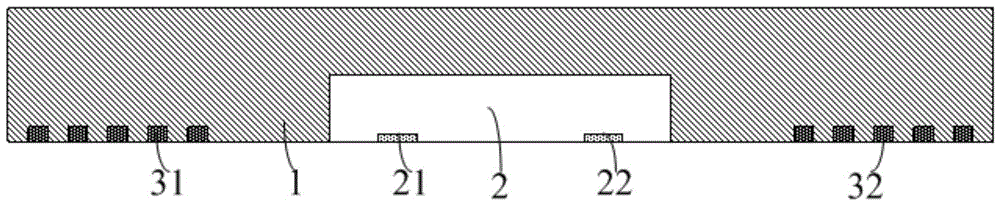

[0029] Such as Picture 10 Shown: the integrated passive device fan-out wafer-level packaging structure includes a molding compound body 1 and a fan-out chip 2 molded in the molding compound body 1. The chip 2 has a first electrode 21 and a second electrode on the front side 22. The front surface of the chip 2 is flush with the front surface of the molding compound body 1; the molding compound body 1 is provided with a first metal wiring layer 31 and a second metal wiring layer 32, a first metal wiring layer 31 and a second metal wiring layer The layer 32 is flush with the front surface of the molding compound body 1; Picture 11 As shown, the first metal wiring layer 31 and the second metal wiring layer 32 are spirally distributed on the molding compound body 1, and electrical characteristics of resistance or inductance are obtained through the spiral structure; on the front sid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More