Embedded capacitor structure and manufacturing method thereof

A capacitor structure and manufacturing method technology, applied in the field of capacitors, can solve problems such as large parasitic capacitors, achieve the effects of reducing area, realizing diversity, and ensuring verticality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

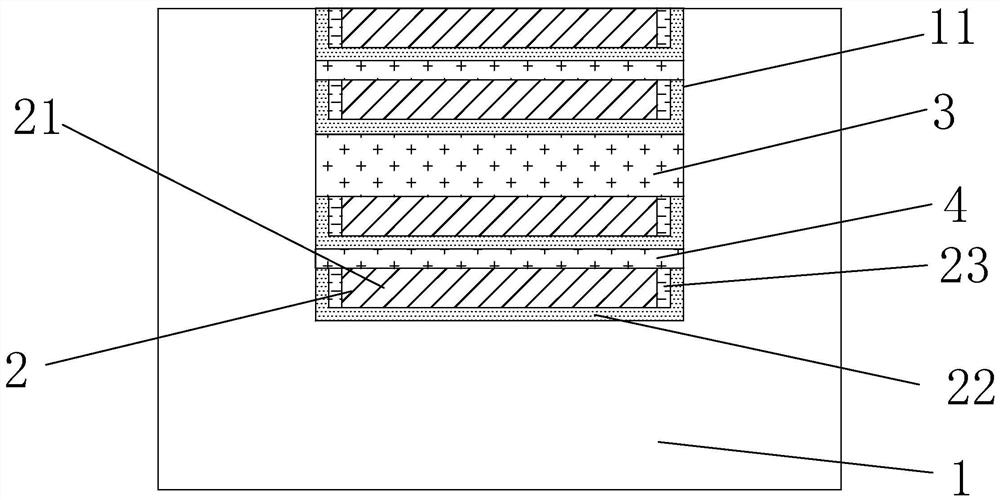

Embodiment 1

[0036] refer to figure 1 , the embedded capacitive structure proposed by the embodiment of the present application includes a substrate and at least one set of capacitive structures 2 . Where there is a trench 11 with a certain depth on the substrate 1, and a third dielectric layer 3 may be arranged between two adjacent groups of capacitive structures 2, at least two groups of capacitive structures 2 and the third dielectric layer 3 in the middle are laminated and arranged in the trench 11 constitutes an embedded capacitor. Wherein, the thickness of the substrate 1 is 625-665 μm, and the material of the substrate 1 includes Si or GaAs. The depth of the trench 11 is 10 μm˜100 μm, and the sidewall of the trench 11 has a certain verticality in the substrate 1 . Specifically, the included angle between the sidewall of the ditch 11 and the bottom of the ditch 11 is 88°-92°. From the bottom of the trench 11 along the depth direction of the trench 11, multiple layers of the capaci...

Embodiment 2

[0050] refer to figure 1 , another embedded capacitor structure, which differs from the first embodiment in that the adhesive layer 22 is made of Si, and the electrode layer is manufactured using a self-aligned silicide (Salicide) process in step 4. Therefore, in the case where the adhesive layer 22 is Si, the electrode layer is deposited on the surface of the Si layer, and the electrode layer is in contact with the surface of the Si layer. Then heat treatment is performed to form a silicide electrode layer on the surface of the contact electrode layer and the Si layer. In step 5, the first dielectric layer and the Si layer on the sidewall of the ditch above the silicided electrode layer are removed, wherein the electrode layer can be selected from one of the metals Ti, Co, and Ni.

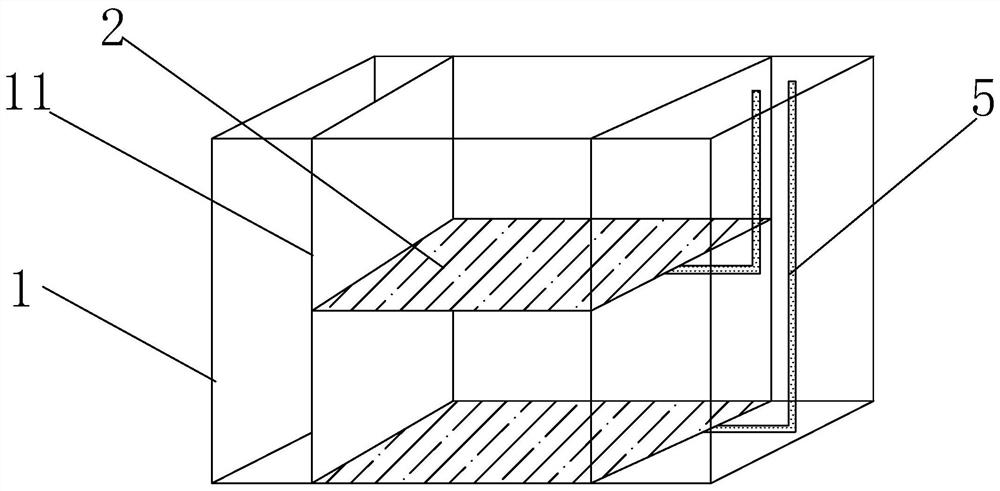

Embodiment 3

[0052] refer to Figure 4 , another embedded capacitor structure, which is different from Embodiment 1 in that an air layer 5 is between two adjacent capacitor structures. Specifically, in step 6, a sacrificial material is filled between two adjacent capacitor structures, and the third dielectric layer 3 is set as a sacrificial layer. In the manufacturing method, step 8 further includes: forming an air layer 5 between two sets of adjacently spaced capacitor structures by opening holes and removing the sacrificial layer after the fabrication of the last group of capacitor structures is completed. Sacrificial material can choose SOG.

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More