Capacitor and layout method thereof

A layout method and capacitor technology, which is applied in capacitors, electric solid devices, circuits, etc., can solve problems such as low capacitance matching accuracy, unsuitable design requirements, and inconsistent capacitance values, and achieve the effect of improving capacitance matching accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

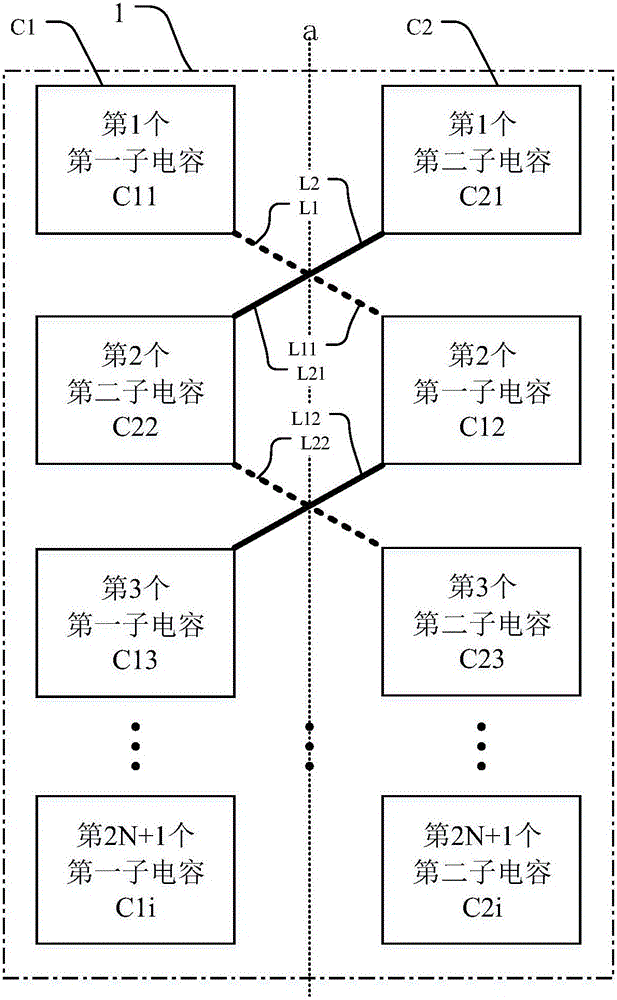

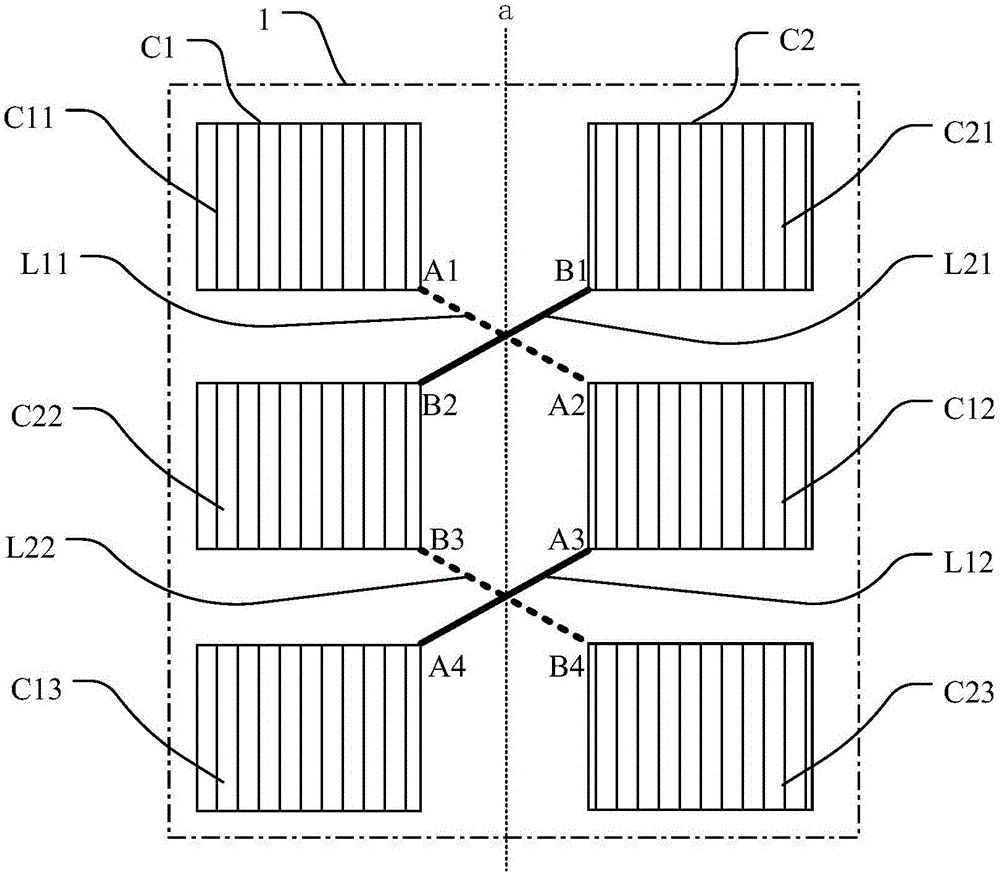

[0034] Please refer to figure 1 , the embodiment of the present invention provides a capacitor 1, including:

[0035] Symmetrically arranged first capacitor C1 and second capacitor C2;

[0036] The first capacitor C1 includes the first group of metal wiring L1 and 2N+1 first sub-capacitors (C11~C1i), and the second capacitor C2 includes the second group of metal wiring L2 and 2N+1 second sub-capacitors (C21 ~C2i); wherein, N is a positive integer, i is equal to 2N+1, 2N+1 first sub-capacitors (C11~C1i) are sequentially connected through the first group of metal connection lines L1, and 2N+1 second sub-capacitors ( C21~C2i) are sequentially connected through the second group of metal connection lines L2; 2N+1 first sub-capacitors (C11~C1i) and 2N+1 second sub-capacitors (C21~C2i) The symmetry axis a of the capacitor C2 is arranged crosswise;

[0037] The difference rate between the capacitance sum of 2N+1 first sub-capacitors (C11~C1i) and the sum of capacitance values o...

Embodiment 2

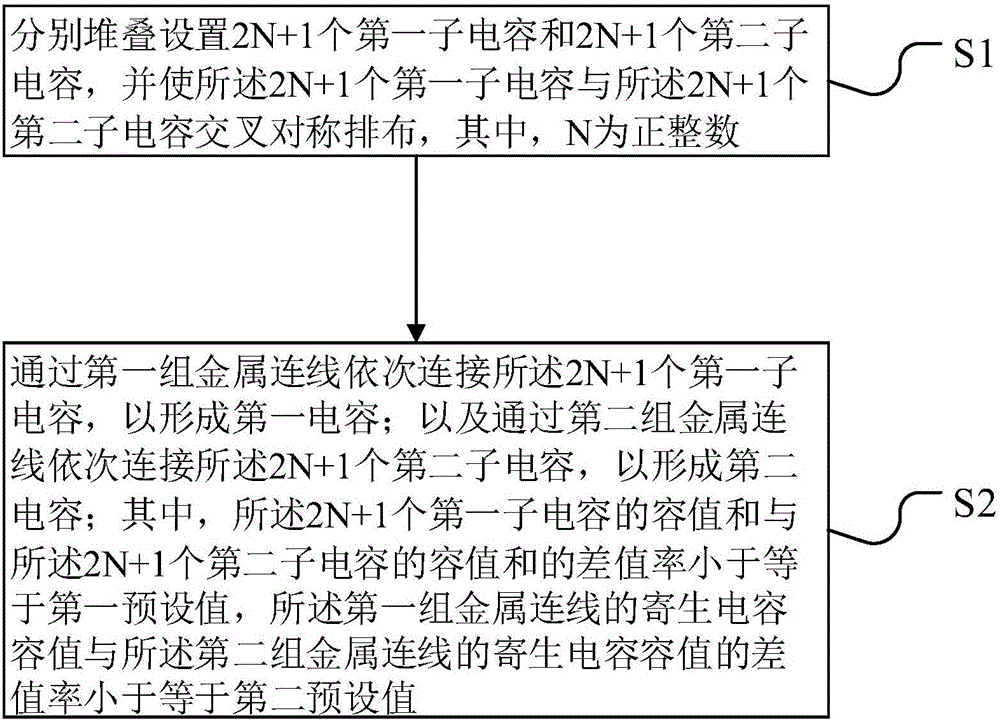

[0051] Based on the same inventive concept, please refer to image 3 , the present application also provides a capacitor layout method, comprising the following steps:

[0052] S1, respectively stacking 2N+1 first sub-capacitors and 2N+1 second sub-capacitors, and making the 2N+1 first sub-capacitors and the 2N+1 second sub-capacitors cross-symmetrically arranged , where N is a positive integer;

[0053] S2. Connect the 2N+1 first sub-capacitors sequentially through the first group of metal wires to form a first capacitor; and sequentially connect the 2N+1 second sub-capacitors through the second group of metal wires to form forming a second capacitor; wherein, the difference rate between the capacitance sum of the 2N+1 first sub-capacitors and the capacitance sum of the 2N+1 second sub-capacitors is less than or equal to a first preset value, and the A difference rate between the parasitic capacitance of the first group of metal connections and the parasitic capacitance of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More