Method for transmitting video data on FPGA and DSP structure on basis of SRIO bus

A technology for video data and bus transmission, applied in the direction of digital video signal modification, electrical components, image communication, etc., can solve the problems of DSP not being able to focus on video processing, programming difficulty, cumbersome, etc., to reduce the complexity of read and write buffer design, Reduce design complexity and save occupancy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The specific implementation manner of the present invention will be further described below by taking a YCbCr4:2:2 video with a resolution of 720×576 as an example.

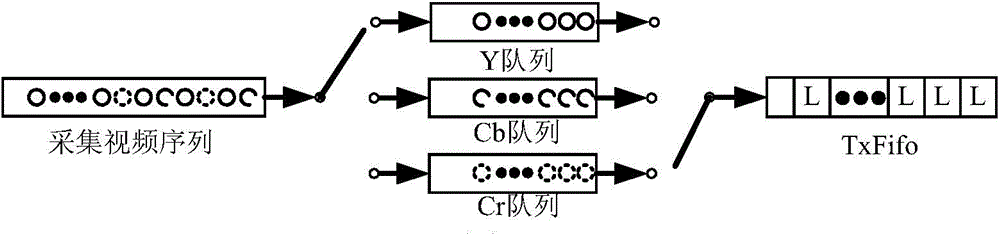

[0026] FPGA captures YCbCr4:2:2 video data in packaged format, and sets up respective video buffer queues for the three components, which are used to separate and temporarily store video components, such as figure 1 shown. Complete video sampling format conversion (YCbCr4:2:2 to YCbCr4:2:0) at the same time during the separation process. The collected video data is sequentially input according to the top field, bottom field and video components, the Cr data in the top field and the Cb data in the bottom field are discarded, and the remaining video data is stored in the corresponding video buffer queue according to different components. When the component data of a complete video line is written into their respective video buffer queues, read each video buffer queue respectively, and write 720 bytes of Y c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More